Xilinx原语详解:从DSP48到全面功能介绍

Xilinx原语是Xilinx公司为FPGA设计者提供的一组特定的模块名称,它们在硬件逻辑单元中扮演着核心角色,类似于软件中的库函数或机器语言指令。这些原语包括了诸如LUT(查找表)、D触发器、RAM等基础元素,是实现设计时必不可少的基础构造块。在使用Xilinx器件进行设计时,所有设计元素必须转换为目标设备支持的原语,否则无法在实际硬件上实现。

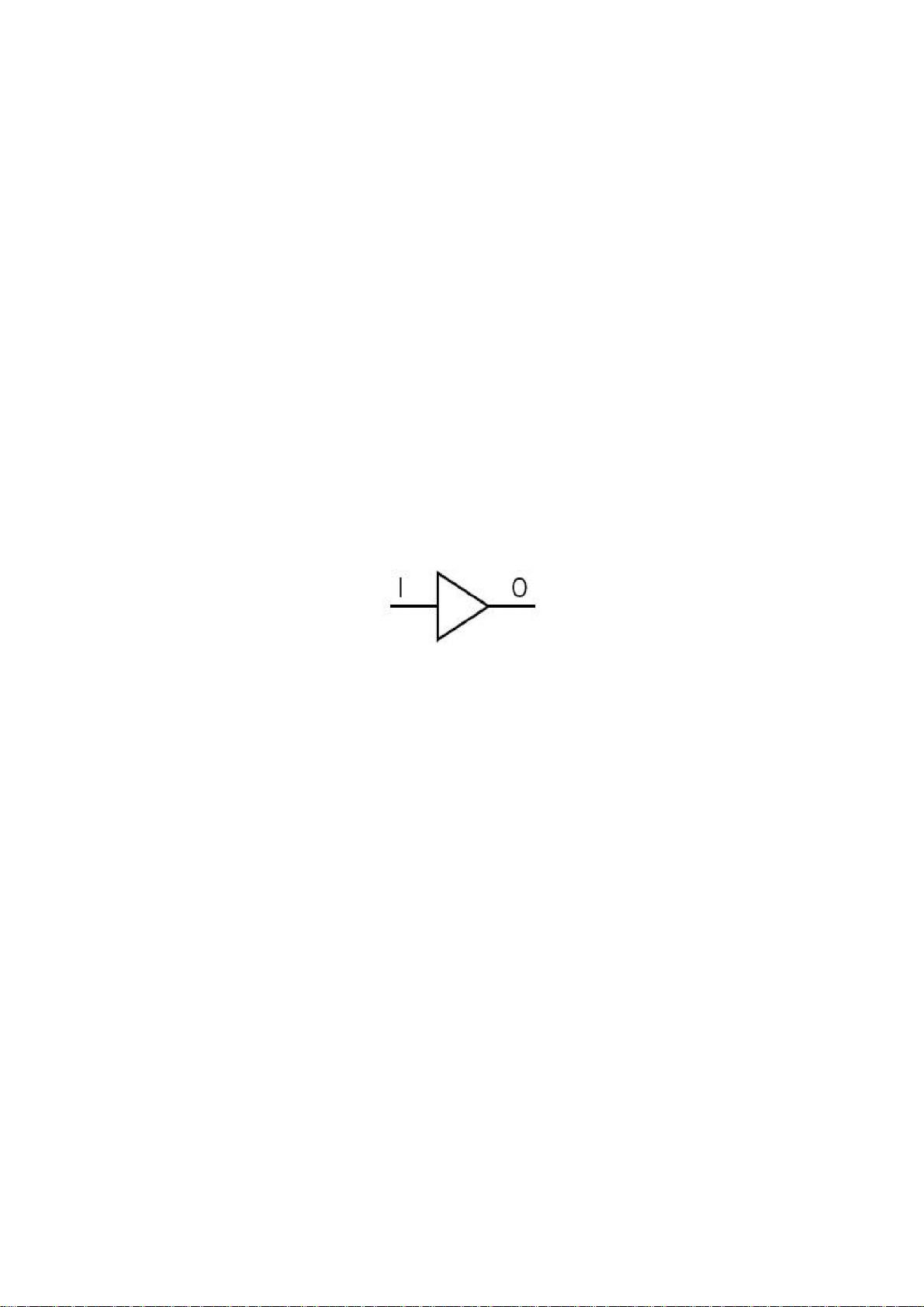

原语的使用方式直接且直观,就像在Verilog HDL中使用模块一样。对于Virtex-4平台,其原语类型最为丰富,涵盖了十类主要功能:计算组件(如DSP48核,一种包含18x18有符号乘法器和可配置流水线的3输入加法器,广泛用于滤波器系统,提升系统稳定性和逻辑资源利用率),I/O端口组件,寄存器和锁存器,时钟组件,处理器组件,移位寄存器,配置和检测组件,RAM/ROM组件,Slice/CLB(小逻辑块)以及G比特收发器组件。

DSP48核是一个具体的例子,它是一个高度集成的硬件乘法器加法器,具有18位和48位两种应用位宽选择。在Verilog设计中,通过如下的实例化模板来使用DSP48:

```verilog

module fpga_v4_dsp48(

BCOUT, P, PCOUT, A, B, BCIN, C, CARRYIN, CARRYINSEL, CEC, CECARRYIN, CECINSUB, CECTRL, CEM, CEP, CLK, OPMODE, PCIN, RSTA, RSTB, RSTC, RSTCARRYIN, RSTM, RS);

```

每种原语都有其特定的接口和功能,设计师需要根据项目需求选择并正确地调用这些原语。值得注意的是,并非所有原语都能在所有Xilinx芯片上通用,因此在设计时需要确保所使用的原语与目标器件的特性相匹配。学习和熟练运用这些原语对于高效地利用FPGA资源,优化电路性能至关重要。

124 浏览量

125 浏览量

118 浏览量

1207 浏览量

977 浏览量

118 浏览量

2110 浏览量

1125 浏览量

321 浏览量

heiguang2005

- 粉丝: 5

- 资源: 22