Industry Council on ESD Target Levels 20

Chapter 1: Introduction & Purpose

Robert Ashton, ON Semiconductor

Charvaka Duvvury, Texas Instruments

1.0 History of the Industry Council on ESD Target Levels

The Industry Council on ESD Target Levels (Council) was formed in 2006 to address a growing

disconnect between original equipment manufacturers (OEMs) and manufacturers of integrated

circuits (ICs) with regard to electrostatic discharge (ESD). The competitive environment requires

that OEMs create products with higher performance in ever smaller form factors while

maintaining and improving reliability and offering the products at competitive prices. This

progress was made possible by imposing the following improvements in ICs; higher levels of

functionality, higher speeds, smaller component size and lower power. That is, the burden of

higher performance has been transferred to the IC suppliers, who must achieve these

improvements through enhancements in their chip designs. IC manufacturers have been able to

make these improvements by employing new IC technologies with smaller feature sizes to

improve functionality and speed and lower working voltages to prevent wear-out of the circuit

and maintain reasonable power levels.

OEMs of course need these improvements, but they do not want them at the cost of reliability and

yield. OEMs therefore maintained the same quality and reliability requirements on ICs produced

in the latest technology as they had for a more mature product. One of these requirements was for

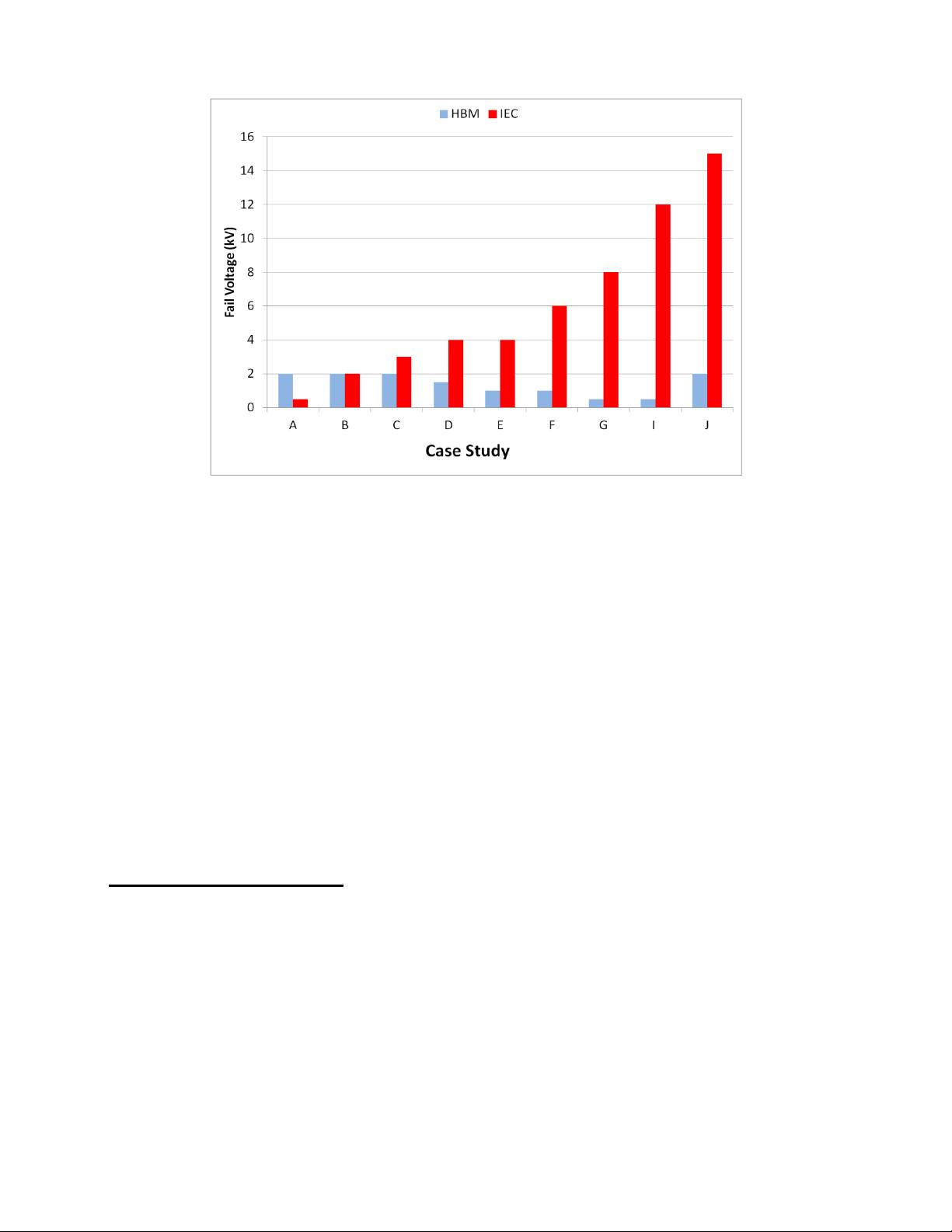

the ESD robustness of ICs. 2 kV of human body model (HBM) robustness had long been a de

facto standard and 500 V of charged device model (CDM) robustness was becoming a similar

requirement. Also, there was an unintended, albeit perceived important, requirement that the ICs

must simultaneously meet 200 V for the machine model (MM). However, starting around the 90

nm technology node, IC manufacturers were finding it increasingly difficult, and sometimes

impossible, to consistently meet these requirements. The smaller feature sizes, lower operating

voltages and high speed signal requirements of ICs were shrinking the design window available

for ESD protection. IC manufacturers, however, knew that 2 kV HBM and 500 V CDM levels

were not needed. HBM and CDM tests are performed to ensure that ICs can survive manufacture

in an ESD controlled manufacturing facility. Experience has shown that with basic ESD control

procedures, ICs with far lower HBM and CDM levels could be handled. Furthermore, without

basic ESD controls, robustness far beyond 2 kV HBM and 500 V CDM will not survive.

Attempting to meet 2 kV HBM and 500 V CDM was therefore costing the industry millions of

dollars in redesigns and delays to market without any benefit to the industry.

The Council was formed to show the electronics industry that lowering ESD levels from 2000 V

HBM and 500 V CDM was not only possible without sacrificing quality and reliability, but also

the right thing to do. “White Paper 1: A Case for Lowering Component Level HBM/MM ESD

Specifications and Requirements” [1] demonstrated why it was becoming more difficult to design

high levels of HBM performance in advanced technologies and presented data that proved lower

HBM levels do not lead to higher levels of failure. White Paper 1 also showed that designing for

HBM would guarantee adequate levels of intrinsic MM performance and that specifically testing

for MM was not necessary. “White Paper 2: A Case for Lowering Component Level CDM ESD

Specifications and Requirements” [2] made a similar case for CDM levels below 500 V by