基于EDA的CPLD与VHDL设计:数字电压表研究

151 浏览量

更新于2024-08-28

收藏 303KB PDF 举报

"数字电子系统的EDA设计方法研究"

在当今高速发展的计算机与微电子技术背景下,电子设计自动化(Electronic Design Automation, EDA)已经成为电子技术的核心。随着需求的增长,数字系统设计追求更高的运行速度、更大的存储容量、更小的体积以及更轻的重量。这一发展趋势的驱动力在于CPLD(复杂可编程逻辑器件)技术的不断进步和完善。CPLD作为一种灵活的硬件解决方案,能够适应各种复杂的电子设计需求。

EDA设计涉及多个技术领域,包括计算机软件、硬件和微电子技术的交叉应用。其中,VHDL(Very High-Speed Integrated Circuit Hardware Description Language)是重要的EDA设计语言,它不仅用于电路的描述,还能进行电路合成和仿真,极大地加速了电路设计过程。举例来说,一个采用VHDL语言设计的数字电压表项目,就充分展示了VHDL的强大功能。

在这个项目中,使用了美国Altera公司的Max+PlusⅡ软件,这是一款先进的计算机辅助工程(CAE)工具,专门用于CPLD的设计和实现。通过这样的工具,设计者可以更加高效地创建和调试电路设计。

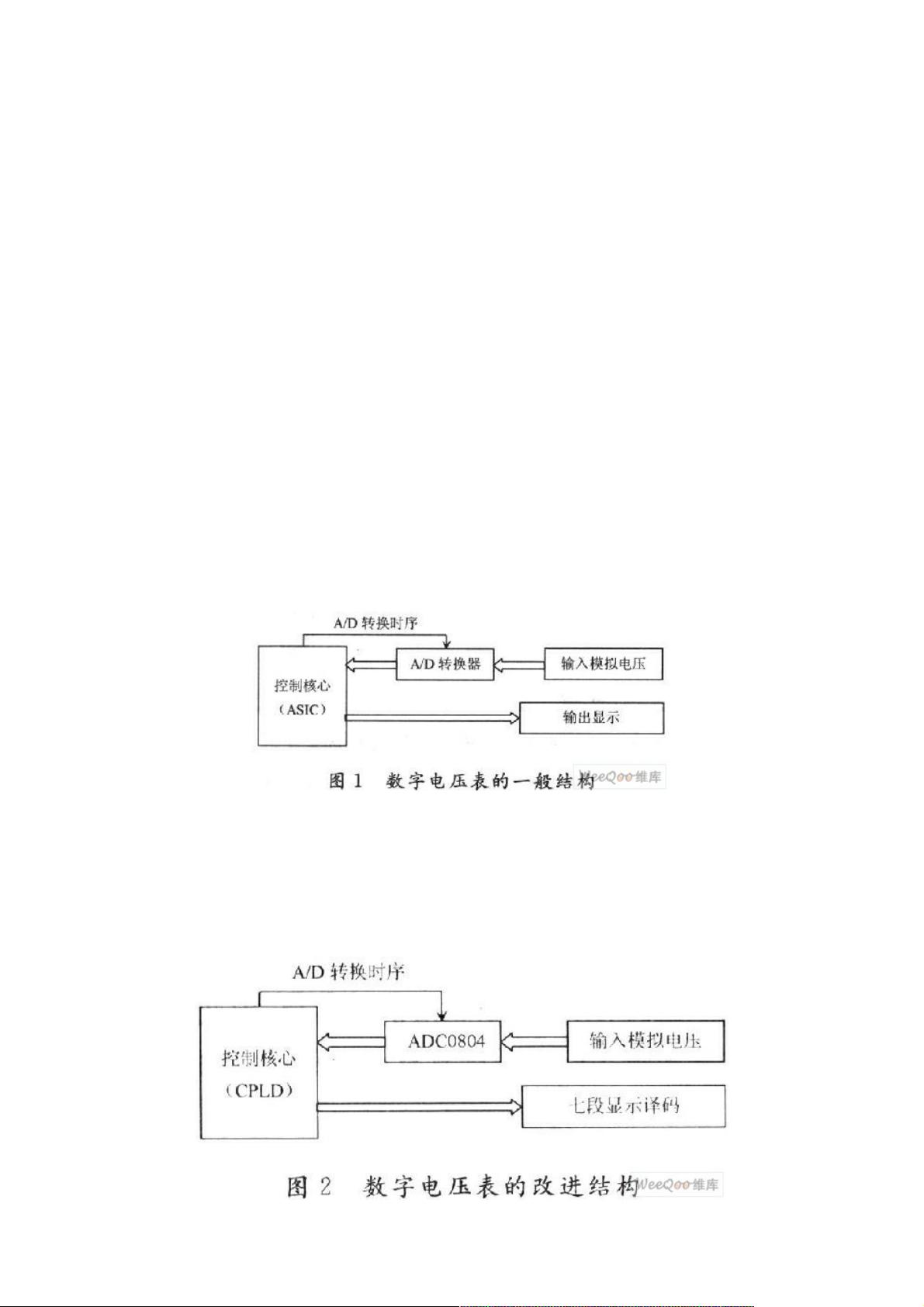

数字电压表是数字电子系统的一个基本组件,广泛应用于电子电工测量、工业测量以及自动化系统等领域。传统上,数字电压表由ASIC(Application-Specific Integrated Circuit)芯片和外围硬件构成,但这种设计方式灵活性较低。相比之下,采用EDA方法,特别是利用CPLD,可以实现更高的灵活性。在CPLD中,系统功能不再受限于固定的硬件结构,而是可以通过编程语言(如VHDL)进行定义和更新,使得系统在硬件不变的情况下,仅通过修改程序就能实现功能的扩展和更新。

如图1所示,数字电压表的核心是A/D转换器,它在控制ASIC产生的时序信号引导下,将输入的模拟信号转化为数字值。控制单元随后处理这些转换结果,并驱动显示器呈现数字电压信号。当使用CPLD替代ASIC时,这种转换和处理过程可以更加灵活地调整,从而增强了系统的可定制性和适应性。

通过以上分析,我们可以看到,EDA设计方法和CPLD技术的结合,为数字电子系统的设计提供了新的可能性,不仅提升了系统性能,还增加了设计的灵活性和可扩展性,这对于应对日益复杂的电子系统需求至关重要。在实际应用中,这种设计理念可以应用于各种电子设备的创新和改进,以满足未来电子技术发展的挑战。

902 浏览量

312 浏览量

2044 浏览量

128 浏览量

2010-06-29 上传

155 浏览量

220 浏览量

2023-06-13 上传

117 浏览量

weixin_38642636

- 粉丝: 12

- 资源: 931

最新资源

- MATLAB在图像处理技术方面的应用论文

- 回溯算法 用来设计货箱装船、背包、最大完备子图、旅行商和电路板排列问题的求解算法。

- 有关贪婪算法的一篇文章

- 2410-S实验指导书.pdf

- makefile PDF 经典电子书

- 嵌入式CC++语言精华文章集锦

- visual studio .NET 技术手册

- 测试用例设计指南说明

- 正交试验设计测试用例

- 中软终端安全解决方案

- Python Essential Reference (3rd Edition)

- The Art of Unix Programming

- Linux内核完全注释-3.0

- 自考英语2的复习知识重点难点

- 全国计算机等级考试三级C语言上机100题

- 蓝屏代码 蓝屏代码 详解