Xilinx AXI_BRAM IP核:高性能内存控制器

需积分: 35 116 浏览量

更新于2024-07-22

收藏 1.44MB PDF 举报

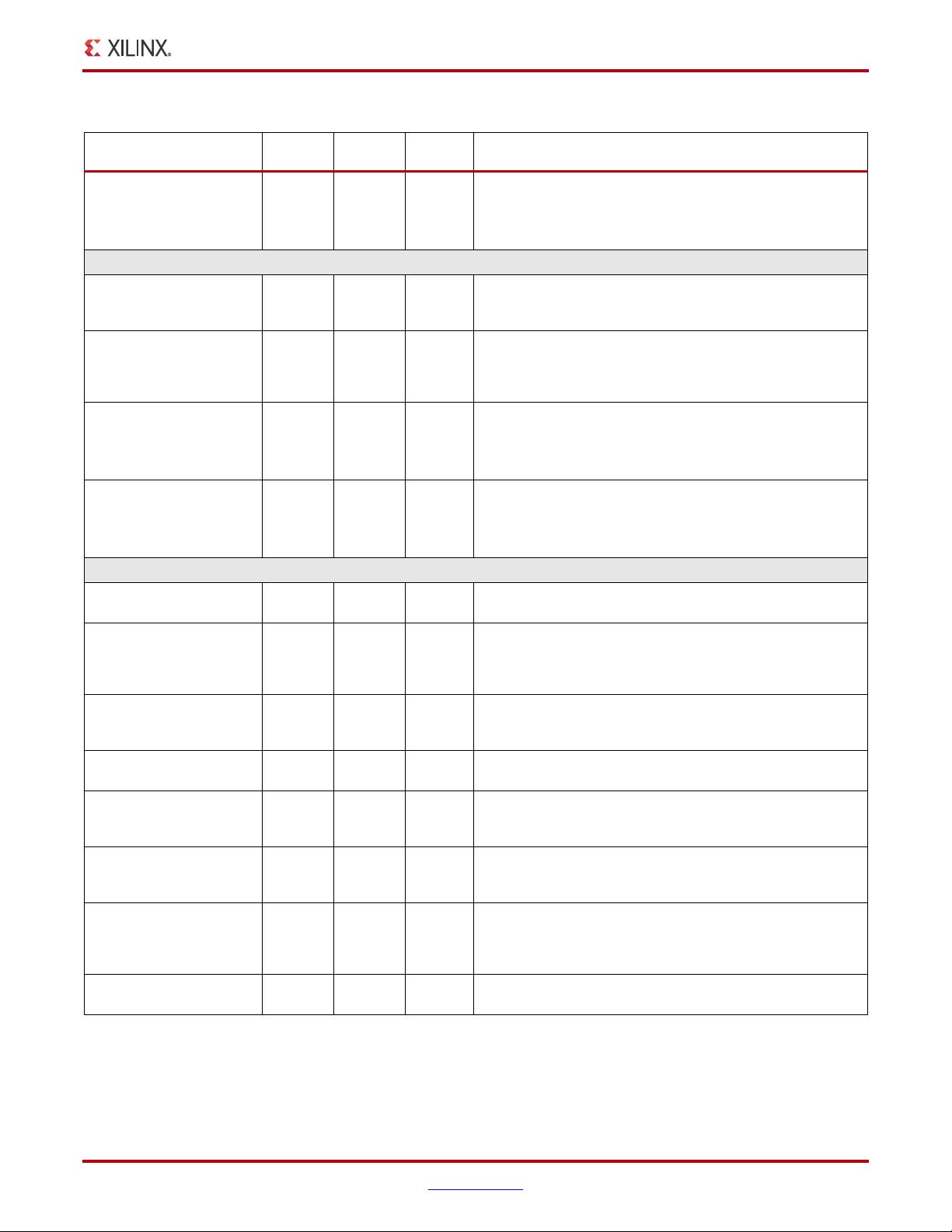

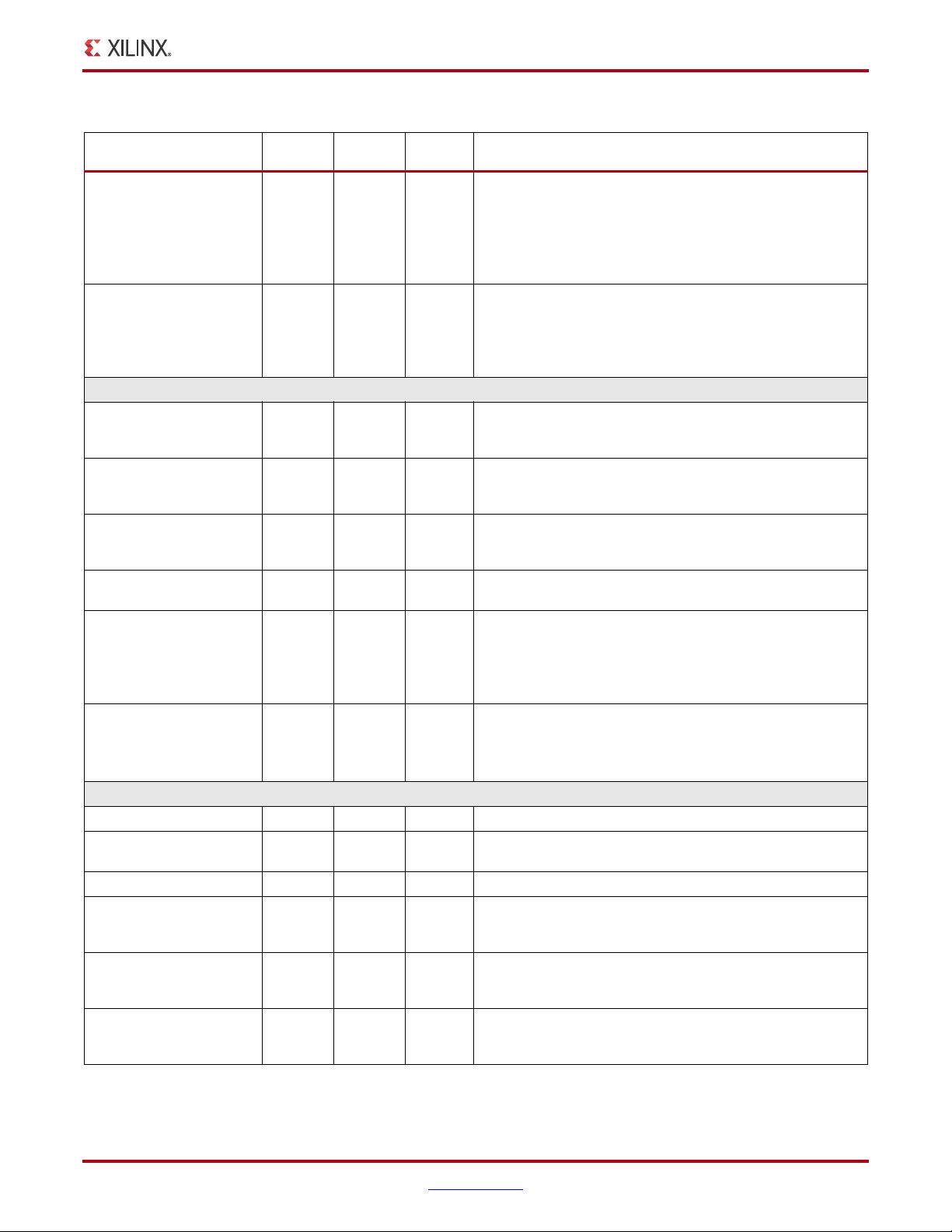

"Xilinx AXI_BRAM IP核是Xilinx公司提供的一种软逻辑CORE IP,用于嵌入式开发工具包(EDK)。该IP核设计为AXI接口的从设备,能够与AXI互连和系统主设备集成,实现与本地BRAM的通信。它支持单次和突发交易,优化了性能,适用于高性能应用。

特性:

- 支持AXI4(内存映射)从接口

- 低延迟内存控制器

- 分离的读写通道接口,利用双口FPGA BRAM技术

- 可配置的BRAM数据宽度(32位、64位和128位)

- 支持递增模式下的最大256次数据传输的突发操作

- 支持2、4、8和16个数据拍的WRAP突发操作

- 支持AXI窄写和未对齐的写突发传输

- 与Xilinx的其他AXI接口兼容

AXI_BRAM IP核的使用使得在FPGA设计中访问存储器变得更加方便和高效。它的AXI4从接口遵循AXI协议标准,提供了内存映射的访问方式,可以处理简单的读写操作以及复杂的突发传输。低延迟特性使其在实时应用中表现出色,确保数据传输的快速响应。

分离的读写通道接口是AXI_BRAM IP核的一个关键特点,它允许同时进行读取和写入操作,这对于需要高速并发读写的系统来说至关重要。此外,通过配置BRAM数据宽度,可以适应不同带宽需求的应用场景。

支持不同的突发模式(INCR和WRAP)使AXI_BRAM IP核能够灵活地处理各种数据流,例如连续的数据块传输或循环数据访问模式。AXI窄写和未对齐的写突发传输功能则增强了其对不规则数据访问的支持,这对于处理非结构化数据或边界情况非常有用。

Xilinx AXI_BRAM IP核是一个强大且灵活的内存控制器,适用于需要高效访问内部BRAM资源的FPGA设计。它能够无缝地融入基于AXI的系统架构中,为高性能、低延迟的内存访问提供了解决方案。设计者可以根据具体需求配置IP核的各项参数,以满足特定应用的性能和功能要求。"

1708 浏览量

966 浏览量

2024-11-09 上传

2024-11-10 上传

320 浏览量

2023-03-21 上传

1208 浏览量

171 浏览量

x9i8a7o6p5e4n3g2

- 粉丝: 0

- 资源: 1

最新资源

- JSP数据库编程指南

- Office Project Server 2007 部署图示指南

- C/C++编程之C++批判(第三版)

- 基于弹片机的交通灯的毕业设计论文

- 算符优先算法.pdf

- 一个关于‘网络安全’基础教程

- Lotus Domino服务器安装配置实例

- USB枚举过程中文翻译

- tc编程错误手册下载,很好的

- COM技术初探_doc

- 用C#编写的五子棋规则"Rule",按禁手规则编写

- Automatic Creation of Object Hierarchies for Ray Tracing of Dynamic Scenes

- Wind River Workbench 3.0

- 商用车控制系统局域网络

- 非常好的单片机编程keil使用详解.pdf

- 单片机编程规范.doc