Cadence Allegro V16X高级设计教程

版权申诉

138 浏览量

更新于2024-06-26

收藏 4.67MB PDF 举报

"Cadence Allegro V16X进阶教材提供了一个全面的学习路径,涵盖了PCB设计的关键方面,包括逻辑导入、高级放置、约束管理器、差分对、异常属性、引脚延迟、重用功能以及模块重用等主题。这本教程适合那些已经对Allegro基础有一定了解并希望提升技能的专业人士。"

在Cadence Allegro V16X这个版本中,电路板设计者可以利用一系列高级工具和特性来优化他们的设计流程。以下是一些关键知识点的详细解释:

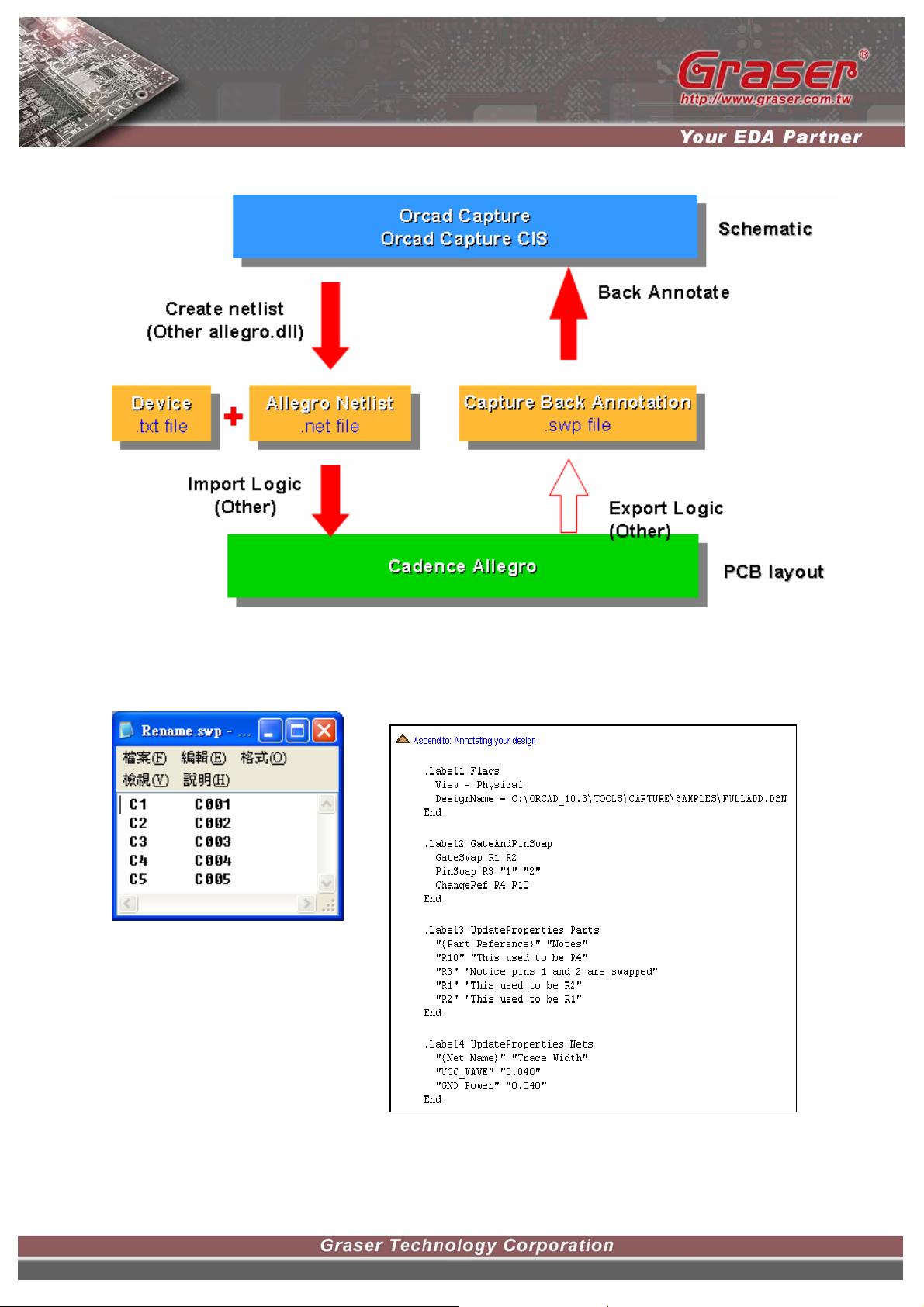

1. **导入逻辑(Importing Logic)**:这一章节主要讲解如何将逻辑设计(如原理图或HDL代码)导入到Allegro PCB设计环境中,以便进行物理布局和布线。理解如何正确导入和关联逻辑网表是确保设计准确性和完整性的基础。

2. **高级放置(Advanced Placement)**:高级放置功能允许设计师根据规则和限制进行精确的元件布局。它涉及到自动化工具,如智能放置、手动调整以及考虑热管理、EMI(电磁干扰)等因素的优化策略。

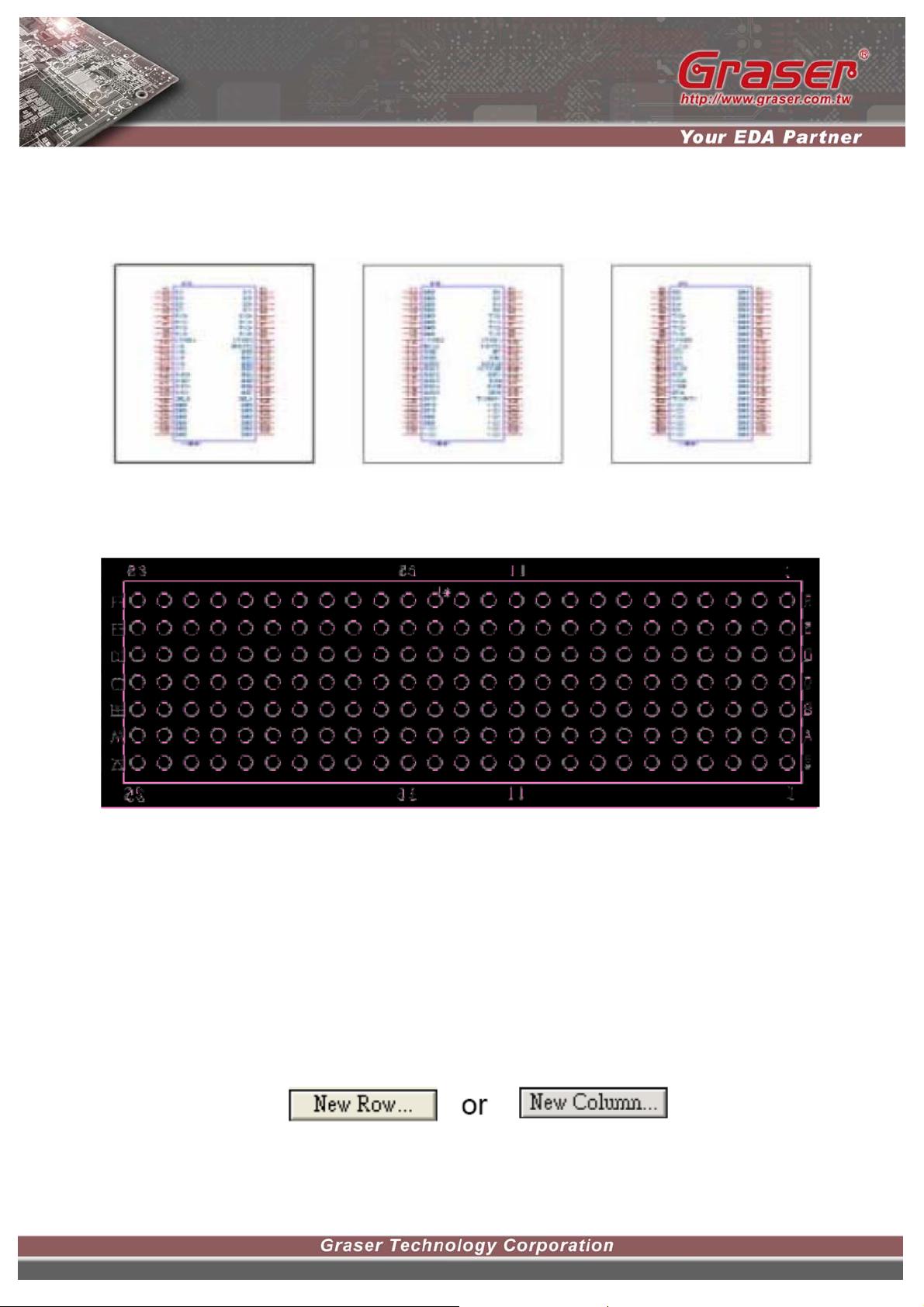

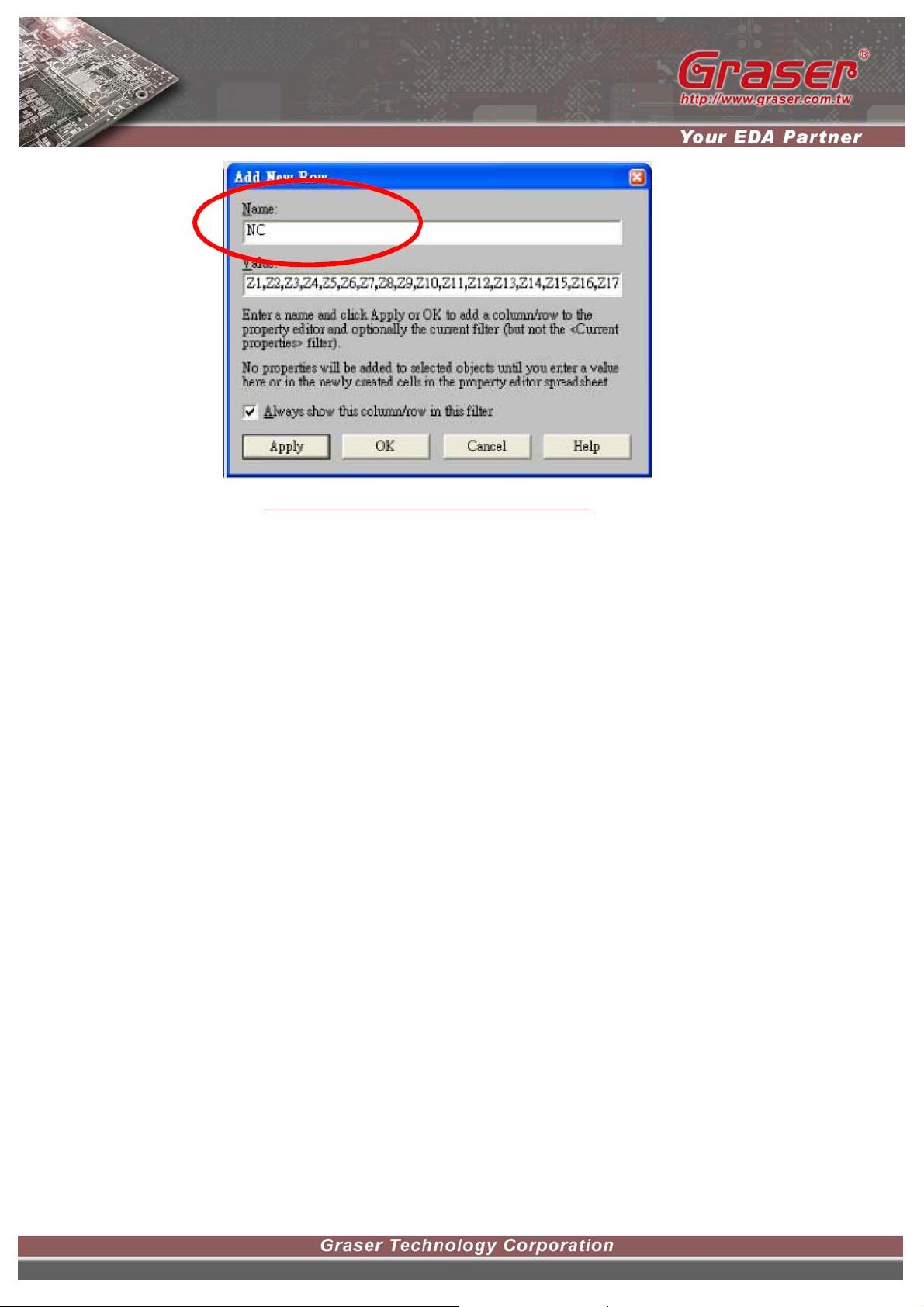

3. **约束管理器(Constraint Manager)**:这是Allegro中的一个核心组件,用于设置和管理设计规则。约束管理器可以帮助设计师定义电气、机械、热和信号完整性约束,确保设计符合规格要求。

4. **差分对(Differential Pair)**:在高速数字设计中,差分对是一种重要的信号传输方式,能减少噪声影响和提高信号质量。这一章节会详细介绍如何在Allegro中创建和管理差分对,以及如何处理相关的布线规则。

5. **异常属性(Exceptional Property)**:异常属性允许设计师为特定元件或网络设置特殊的规则,这些规则可能与全局规则不同。这在处理特殊情况或者需要特殊处理的元件时非常有用。

6. **引脚延迟(Pin Delay, XL)**:Pin Delay功能帮助设计师评估和优化信号传播时间,特别是在高速设计中,理解引脚延迟对于确保时序正确至关重要。

7. **重用功能(Reuse Function)**:重用功能允许设计师创建和保存设计模板,以便在多个项目中重复使用,从而提高效率和一致性。

8. **模块重用(Module Reuse)**:模块化设计是提高设计效率的关键,模块重用允许设计师将已验证的设计单元作为一个整体重复使用,减少设计错误和缩短开发时间。

通过深入学习和实践这些章节,设计师能够提升其在Cadence Allegro V16X中的专业技能,优化PCB设计流程,并实现更高效、高质量的电路板设计。

2018-12-04 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

RedCar

- 粉丝: 55

- 资源: 2027

最新资源

- Aspose资源包:转PDF无水印学习工具

- Go语言控制台输入输出操作教程

- 红外遥控报警器原理及应用详解下载

- 控制卷筒纸侧面位置的先进装置技术解析

- 易语言加解密例程源码详解与实践

- SpringMVC客户管理系统:Hibernate与Bootstrap集成实践

- 深入理解JavaScript Set与WeakSet的使用

- 深入解析接收存储及发送装置的广播技术方法

- zyString模块1.0源码公开-易语言编程利器

- Android记分板UI设计:SimpleScoreboard的简洁与高效

- 量子网格列设置存储组件:开源解决方案

- 全面技术源码合集:CcVita Php Check v1.1

- 中军创易语言抢购软件:付款功能解析

- Python手动实现图像滤波教程

- MATLAB源代码实现基于DFT的量子传输分析

- 开源程序Hukoch.exe:简化食谱管理与导入功能