深入解析FPGA时钟域穿越问题及其解决方案

需积分: 13 25 浏览量

更新于2024-07-24

收藏 181KB DOC 举报

在现代系统级芯片(SoC)设计中,随着集成度的提升和功能的日益复杂,数据频繁地在不同的时钟域之间进行传输,这就带来了显著的时钟域穿越(Clock Domain Crossing, CDC)问题。时钟域穿越指的是一个由一个时钟驱动的触发器(如Flop)中的数据流向另一个由不同时钟驱动的触发器的情况。这可能导致数据一致性、时序延迟、同步问题等一系列挑战。

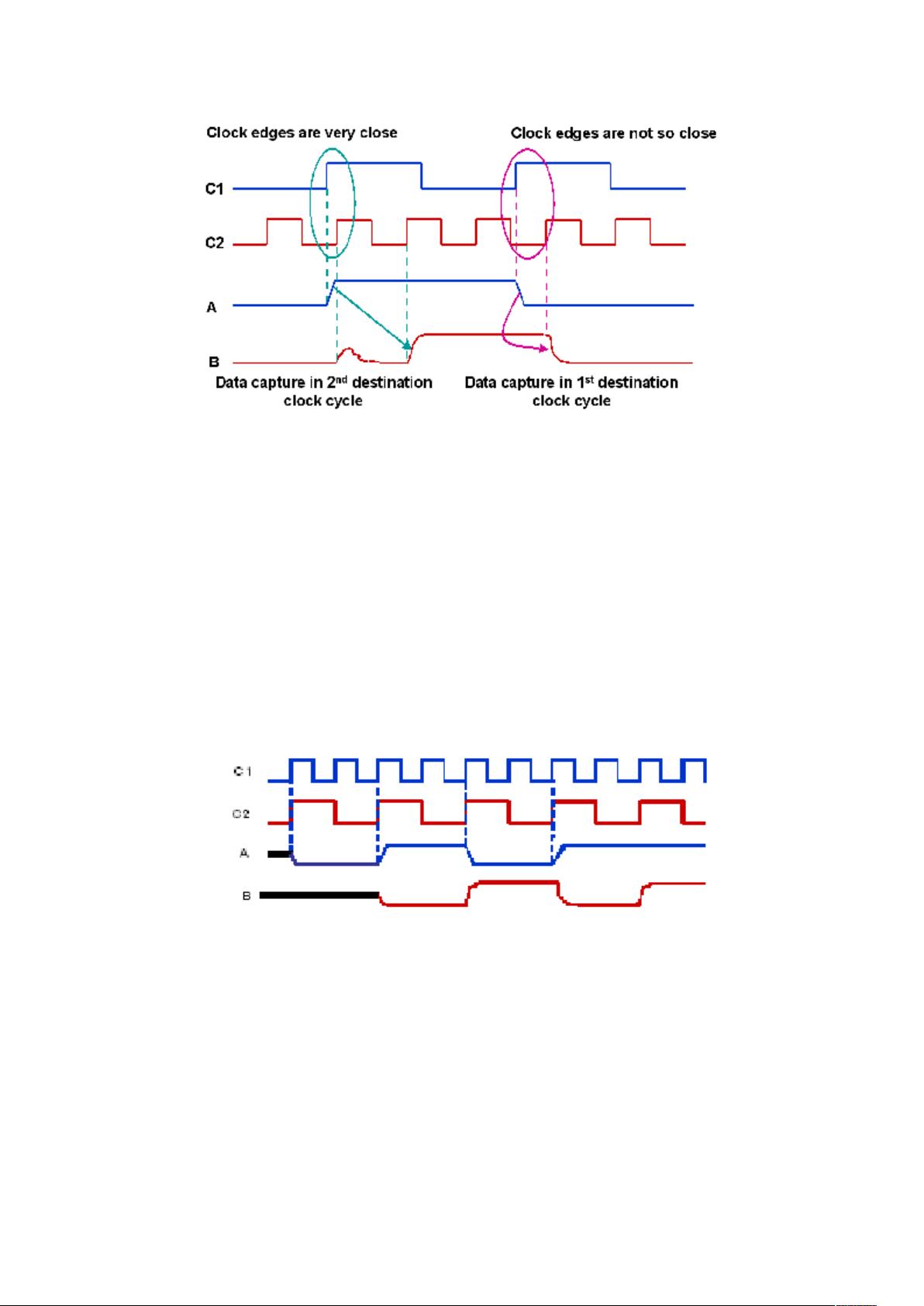

理解时钟域穿越的关键在于识别可能的问题类型及其影响。在图1所示的示例中,信号A从C1时钟域出发,需要被C2时钟域正确捕获。时钟间的相位关系对数据传输至关重要。如果两个时钟不精确同步,可能会出现以下问题:

1. **数据丢失(Data Loss)**: 如果源时钟快于目标时钟,可能会错过目标时钟的上升沿,导致数据无法正确到达目的地。

2. **数据翻转(Data Flip-Flops)**: 由于时钟边缘不匹配,可能导致数据在目标时钟域发生错误。

3. **时序违规(Timing Violations)**: 数据传输延迟超出允许范围,可能导致设计不符合设计规范。

4. **噪声敏感性增加(Increased Sensitivity to Noise)**: 不同时钟域之间的数据传输容易受到噪声的影响,尤其是在高速信号线上传输。

传统的验证方法,如基于模拟的测试和静态时序分析,可能不足以确保数据在时钟域间的一致性和可靠性。因此,为了有效解决这个问题,需要采用新的验证策略。这些策略可能包括:

- **动态时序分析**:通过实际运行电路并监测信号在时钟周期内的行为,来检测潜在的问题。

- **专用工具和IP**:利用专门针对时钟域穿越问题设计的硬件或软件工具,简化验证流程。

- **时钟域规划**:精心设计时钟网络结构,尽可能减少时钟域穿越次数,并优化时钟树结构以减小时延影响。

- **协议和接口设计**:使用同步协议(如LVDS, PCI Express等)确保数据在不同时钟域之间的正确交换。

- **自动生成验证脚本**:通过自动化工具生成针对时钟域穿越的覆盖率测试,确保所有可能路径都被覆盖。

理解和管理时钟域穿越是深入亚微米级FPGA设计中不可或缺的一部分。设计师必须考虑到时钟同步、数据传输延迟、噪声等因素,采取适当的策略和技术来确保设计的性能和可靠性。随着技术的发展,新的验证方法和技术将持续涌现,帮助工程师更有效地应对这一复杂的设计挑战。

2024-01-19 上传

2023-03-16 上传

2023-05-11 上传

2023-05-15 上传

2023-09-16 上传

2023-05-25 上传

2023-06-10 上传

2023-07-27 上传

2023-05-13 上传

fanxun

- 粉丝: 0

- 资源: 2

最新资源

- JDK 17 Linux版本压缩包解压与安装指南

- C++/Qt飞行模拟器教员控制台系统源码发布

- TensorFlow深度学习实践:CNN在MNIST数据集上的应用

- 鸿蒙驱动HCIA资料整理-培训教材与开发者指南

- 凯撒Java版SaaS OA协同办公软件v2.0特性解析

- AutoCAD二次开发中文指南下载 - C#编程深入解析

- C语言冒泡排序算法实现详解

- Pointofix截屏:轻松实现高效截图体验

- Matlab实现SVM数据分类与预测教程

- 基于JSP+SQL的网站流量统计管理系统设计与实现

- C语言实现删除字符中重复项的方法与技巧

- e-sqlcipher.dll动态链接库的作用与应用

- 浙江工业大学自考网站开发与继续教育官网模板设计

- STM32 103C8T6 OLED 显示程序实现指南

- 高效压缩技术:删除重复字符压缩包

- JSP+SQL智能交通管理系统:违章处理与交通效率提升