Red Cycloen NIOSII开发板原理图详解:四层设计与布局指南

需积分: 9 90 浏览量

更新于2024-09-08

收藏 202KB PDF 举报

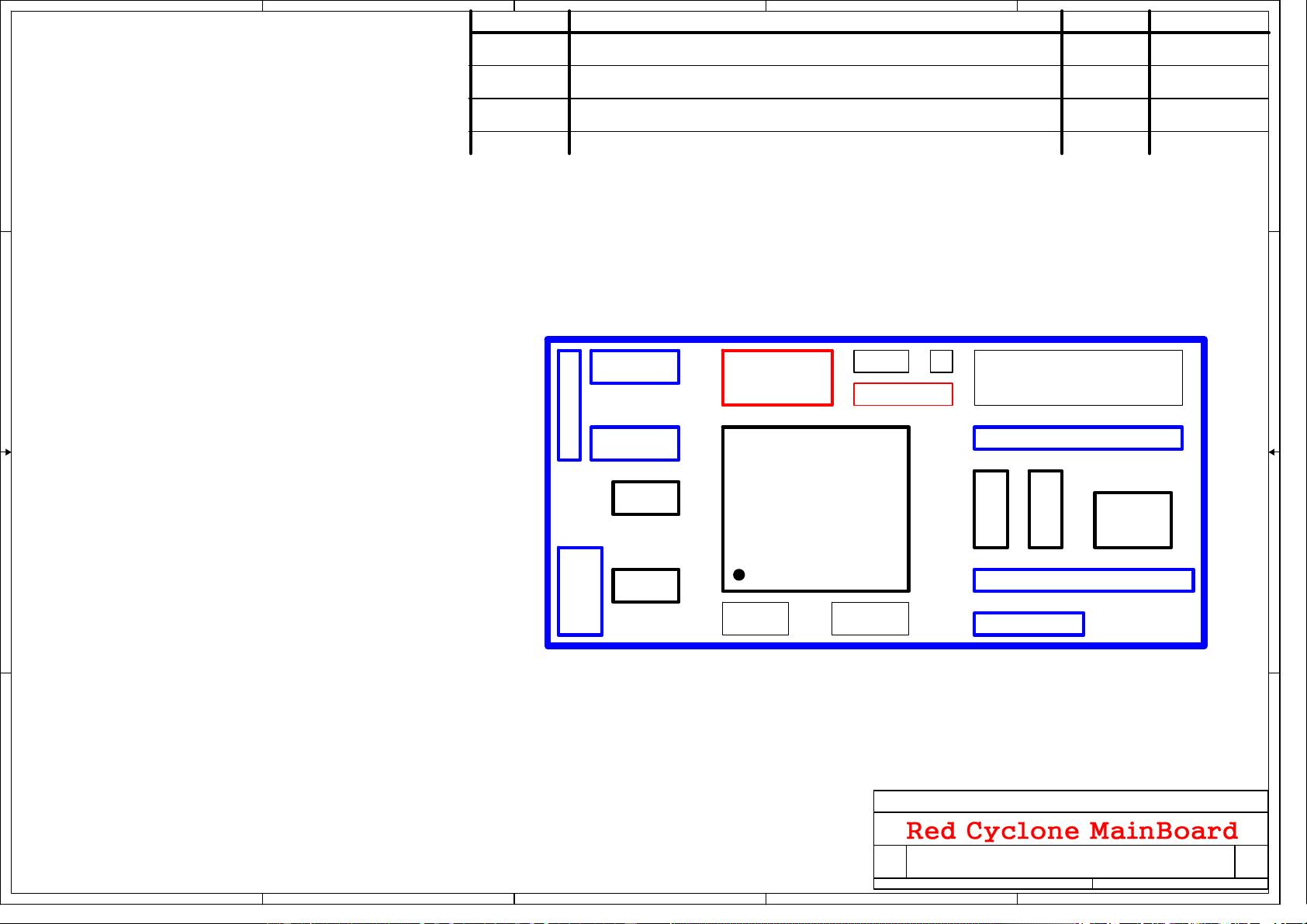

红色飓风工作室的Red Cycloen系列NIOSII开发板原理图是一份详细的电子设计文档,主要关注的是基于 Altera Cyclone FPGA 的嵌入式系统开发平台。该开发板采用四层PCB设计,旨在优化信号完整性、电源管理以及组件布局。

1. **四层设计**:开发板采用四层PCB设计,确保了良好的信号路径管理和电磁兼容性。其中一层用于接地(GROUNDPLANE1),底层和顶层分别用于信号输入/输出(TOP-SIGNALROUTING和BOTTOM-SIGNALROUTING),中间层用于放置关键电路和元器件,如内存(如0.1uF和0.01uF的去耦电容)和FPGA(CYCLONEFPGA)。

2. **SDRAM设计**:SDRAM的信号处理非常关键,强调等长原则,即确保各引脚间的长度差不超过10%,以维持时钟同步和正确的信号传输。SDCLK(系统时钟)的位置被认为是固定的,不允许改动。同时,建议50+/-5Ω的匹配电阻用于改善阻抗匹配。

3. **FPGA管脚配置**:FPGA的管脚定义允许适度调整,但需保证功能性和信号完整性,且与周围电路保持合适的间距和布局规则。

4. **电源管理**:板子包含多个电源区域,如CYCLONEPOWER,使用LT1085-3.3V和LT1585-1.5V等稳压器,提供系统所需的电压。同时,为降低噪声和提高稳定性,电源线路上部署了去耦电容。

5. **扩展接口**:开发板具有EXT_IO区域,可能包括连接器、UART、LED和其他外设接口。蓝色边框区域表示为可插拔模块,需特别注意与周边元器件的电气隔离和间距,尤其是高度限制在8mm以下。

6. **布局与规则**:设计者提供了具体的布局参考,包括最小通孔大小(12/20mil)和信号路由的要求,如在曼哈顿距离范围内布线,以减小电磁干扰。

7. **元器件规格**:如0.9V的配置接口(CONFIG_IO)、10/7/04版本日期和特定的SCH(Schematic Index)编号,以及对SRAM和Flash的具体描述。

8. **批准与状态**:设计已准备进行布局,且经过了审核和批准,表明其符合设计规范和标准。

这份原理图涵盖了从硬件设计的细节到电路性能优化的关键要素,是电子工程师进行Red Cycloen系列NIOSII开发板设计和调试的重要参考资料。

2010-04-17 上传

2022-09-19 上传

点击了解资源详情

2013-05-04 上传

2010-06-21 上传

2008-12-04 上传

2022-10-30 上传

drjiachen

- 粉丝: 172

- 资源: 2138

最新资源

- SSM Java项目:StudentInfo 数据管理与可视化分析

- pyedgar:Python库简化EDGAR数据交互与文档下载

- Node.js环境下wfdb文件解码与实时数据处理

- phpcms v2.2企业级网站管理系统发布

- 美团饿了么优惠券推广工具-uniapp源码

- 基于红外传感器的会议室实时占用率测量系统

- DenseNet-201预训练模型:图像分类的深度学习工具箱

- Java实现和弦移调工具:Transposer-java

- phpMyFAQ 2.5.1 Beta多国语言版:技术项目源码共享平台

- Python自动化源码实现便捷自动下单功能

- Android天气预报应用:查看多城市详细天气信息

- PHPTML类:简化HTML页面创建的PHP开源工具

- Biovec在蛋白质分析中的应用:预测、结构和可视化

- EfficientNet-b0深度学习工具箱模型在MATLAB中的应用

- 2024年河北省技能大赛数字化设计开发样题解析

- 笔记本USB加湿器:便携式设计解决方案