NXP Semiconductors

PN5180A0xx/C3,C4

High-performance multiprotocol full NFC frontend, supporting all NFC Forum modes

11.4 SPI Host Interface

The following description of the SPI host interface is valid for the NFC operation mode.

The Secure Firmware Download mode uses a different physical host interface handling.

Details are described in chapter 12.

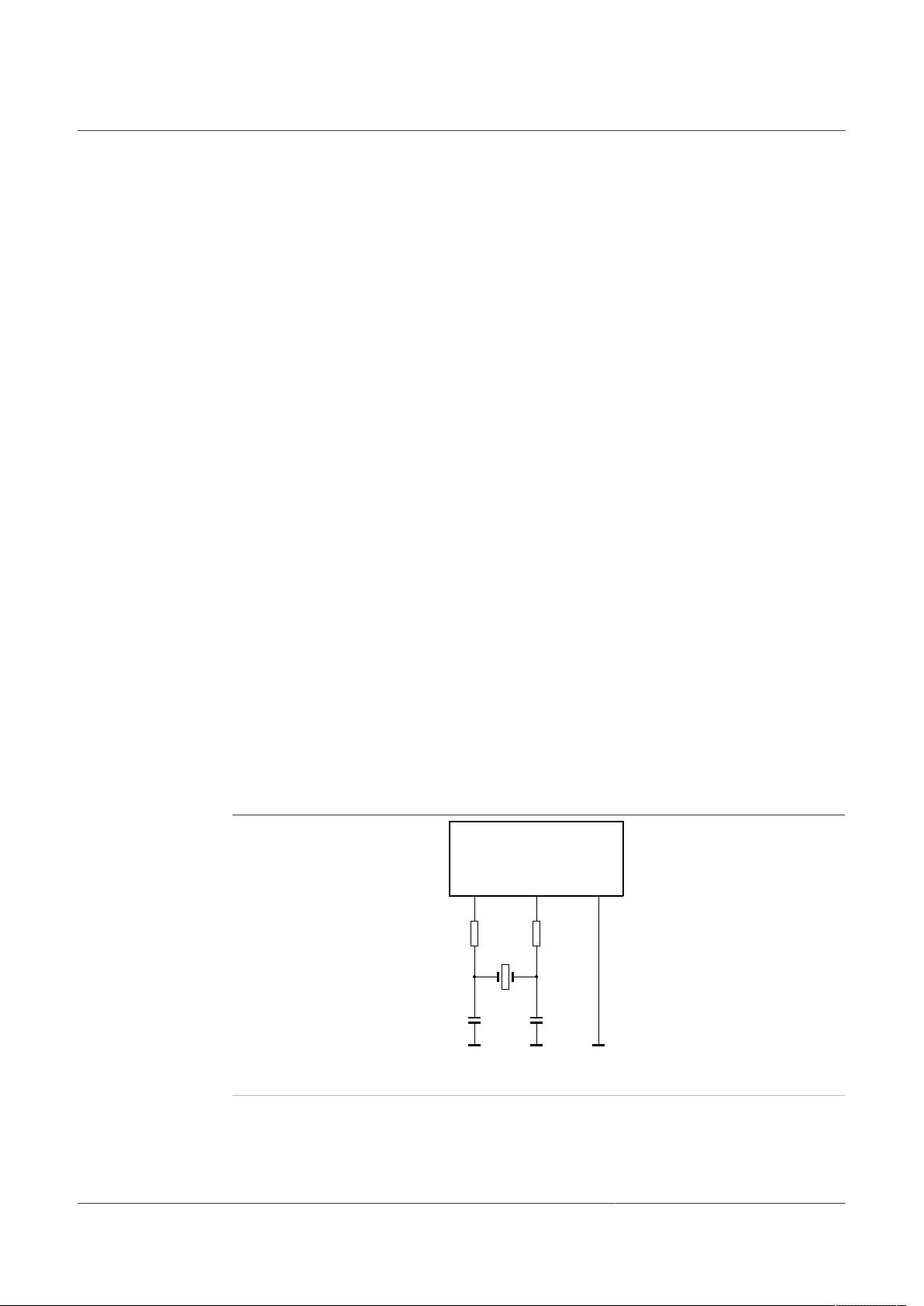

11.4.1 Physical Host Interface

The interface of the PN5180 to a host microcontroller is based on a SPI interface,

extended by signal line BUSY. The maximum SPI speed is 7 Mbit/s and fixed to CPOL

= 0 and CPHA = 0. Only a half-duplex data transfer is supported. There is no chaining

allowed, meaning that the whole instruction has to be sent or the whole receive buffer

has to be read out. The whole transmit buffer shall be written at once as well. No NSS

assertion is allowed during data transfer.

As the MISO line is per default high-ohmic in case of NSS high, an internal pull-up

resistor can be enabled via EEPROM.

The BUSY signal is used to indicate that the PN5180 is not able to send or receive data

over the SPI interface.

The host interface is designed to support the typical interface supply voltages of 1.8 V

and 3.3 V of CPUs. A dedicated supply input which defines the host interface supply

voltage independent from other supplies is available (PVDD). Only a voltage of 1.8 V or

3.3 V is supported, but no voltage in the range of 1.95 V to 2.7 V.

• Master In Slave Out (MISO)

The MISO line is configured as an output in a slave device. It is used to transfer data

from the slave to the master, with the most significant bit sent first. The MISO signal is

put into 3-state mode when NSS is high.

• Master Out Slave In (MOSI)

The MOSI line is configured as an input in a slave device. It is used to transfer data from

the master to a slave, with the most significant bit sent first.

• Serial Clock (SCK)

The serial clock is used to synchronize data movement both in and out of the device

through its MOSI and MISO lines.

• Not Slave Select (NSS)

The slave select input (NSS) line is used to select a slave device. It shall be set to low

before any data transaction starts and must stay low during the transaction.

• Busy

During frame reception, the BUSY line goes ACTIVE and goes to IDLE when

PN5180 is able to receive a new frame or data is available (depending if SET or

GET frame is issued). If there is a parameter error, the IRQ is set to ACTIVE and a

GENERAL_ERROR_IRQ is set.

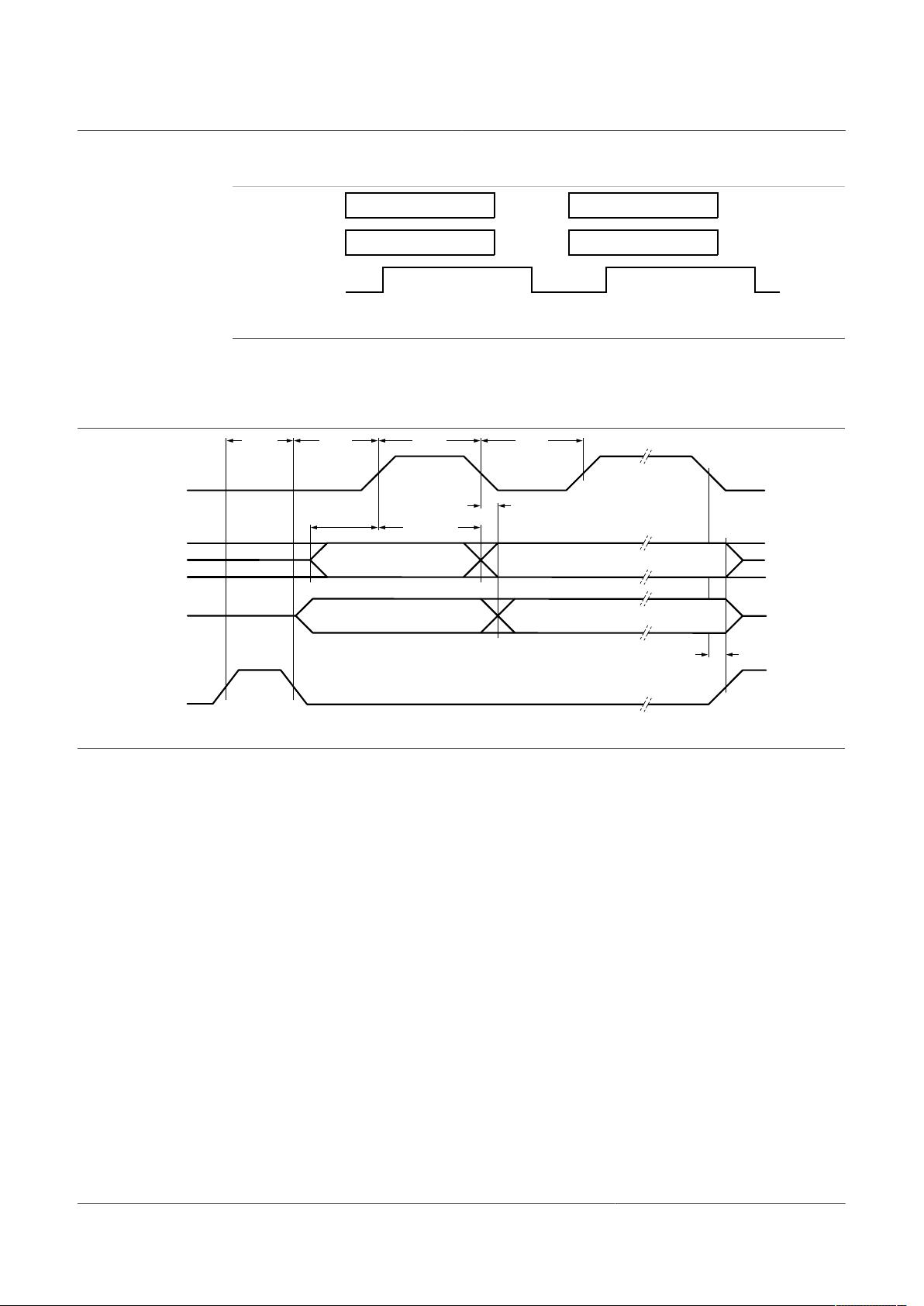

Both master and slave devices must operate with the same timing. The master device

always places data on the MOSI line a half cycle before the clock edge SCK, in order for

the slave device to latch the data.

The BUSY line is used to indicate that the system is processing data and cannot receive

any data from a host. The system handles the busy signal different for normal mode and

debug mode (test bus enabled). In the sequence below, step 3 is optional for the normal

PN5180A0xx_C3_C4 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2021. All rights reserved.

Product data sheet Rev. 3.9 — 17 November 2021

COMPANY PUBLIC 18 / 160