VHDL与Verilog实现三态门详解及仿真对比

在本文中,作者韦志恒探讨了在VHDL和Verilog HDL这两种高级硬件描述语言中实现和仿真三态门的细节。首先,他解释了什么是三态门,它是一种特殊类型的逻辑门,除了通常的高电平和低电平输出状态外,还有一种高阻(Z)状态,当使能信号EN为高时,门处于高阻状态,类似于电路断开。

在VHDL部分,作者着重介绍了同步和异步三态门的具体实现,这可能涉及到时钟同步的门控逻辑设计,以及如何在设计中正确地使用使能信号以控制门的工作状态。他还提到了在VHDL中,通过信号赋值语句和进程控制来管理三态门的行为。

在Verilog HDL方面,由于提到很多关于Verilog中三态门仿真存在模糊不清的情况,韦志恒强调了仿真中的自动化原则,避免了依赖于手工干预的Force语句。他可能解释了如何使用Verilog的模块化设计和仿真指令来实现三态门,并且可能提到了不同仿真环境中的注意事项。

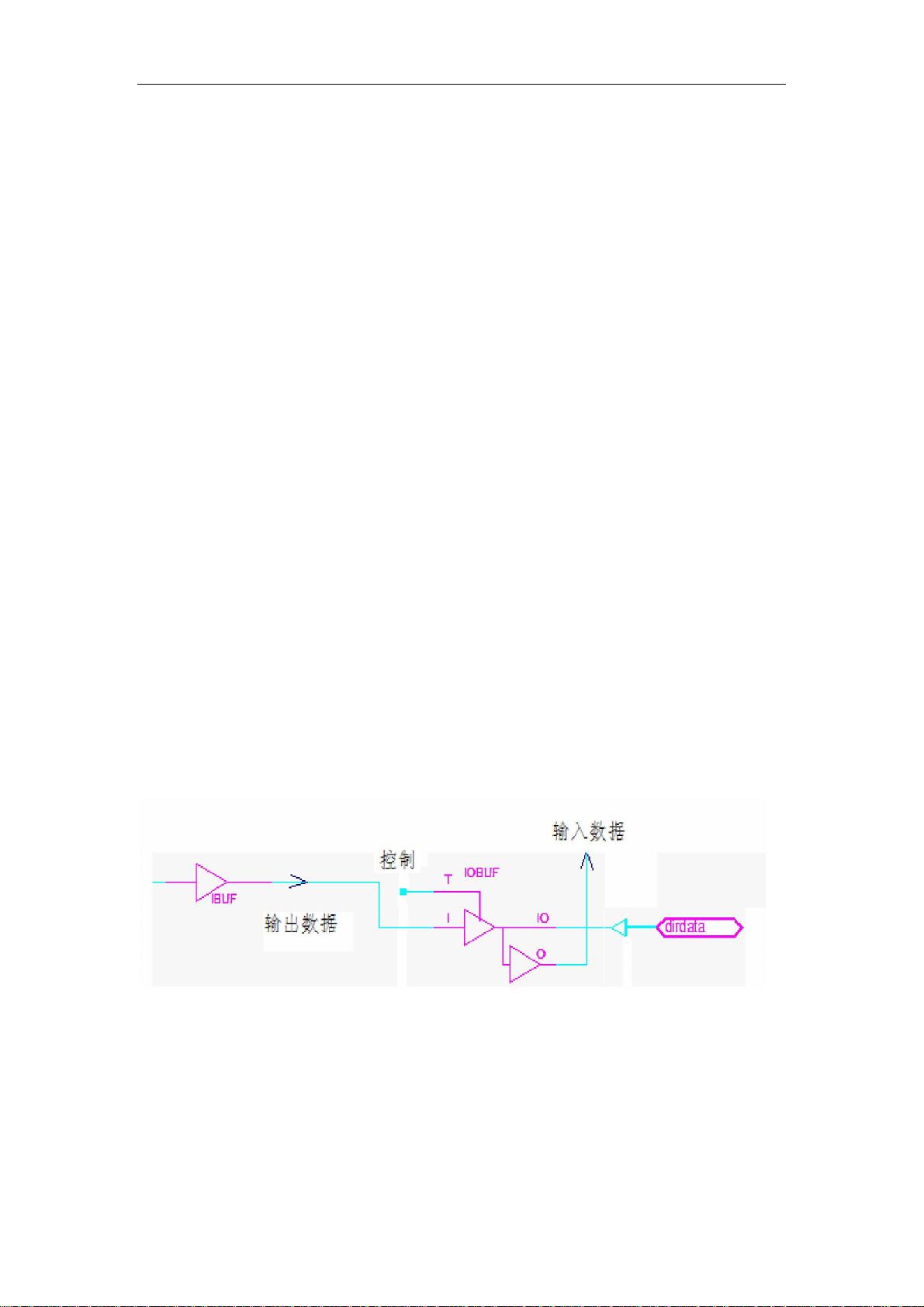

文章还提供了具体实例,如TI DSP的EMIF总线,展示了三态门在实际系统中的应用。此外,对于双向管脚INOUT,作者给出了详细描述,指出它在FPGA中作为一个输入和输出的共享端口,连接到三态输出缓冲器。

最后,韦志恒总结了VHDL和Verilog HDL在三态门仿真上的关键要点,可能会包括语言特性对仿真性能的影响,以及如何根据设计需求选择最适合的工具和方法。这篇文章不仅提供了一种技术性的教程,也强调了理解和比较不同语言在特定应用场景下的优势和局限性的重要性。

相关推荐

1993 浏览量

319 浏览量

128 浏览量

213 浏览量

165 浏览量

1894 浏览量

267 浏览量

chenyan8189

- 粉丝: 15

最新资源

- Delphi6开发者指南附赠源码与EJB技术解析

- SILLABO软件:逐步阅读文本教学工具

- 网络助手:智能化网络设备管理与拓扑图定制

- Windows 7下用VC打造Netstat功能查看端口状态

- 移动端触屏滑动切换选项卡的jQuery实现代码

- Java编程入门:99乘法表源码与技术笔记分享

- 在线界面设计系统:二等奖得主的web实现

- 深入解析CANopen协议思维导图

- JAVA源代码增添删改技巧与实践指南

- MinGW配置msys和nasm以编译X264与ffmpeg

- jBPM开发环境搭建视频教程

- Prime Solo jQuery 评估:掌握核心技能的挑战

- Java实现ZIP文件的加解密及压缩工具包教程

- Spring Security数据库集成快速使用指南

- 个人知识管理神器:nyfedit7pro

- Ajax3.0示例源码与DLL完整教程指南