Cyclone FPGA PLL使用指南

下载需积分: 10 | DOC格式 | 924KB |

更新于2024-07-29

| 38 浏览量 | 举报

"本文介绍了如何在Cyclone FPGA中使用PLL进行时钟管理,包括PLL的基本功能、硬件结构、软件配置、管脚连接、硬件功能、时钟反馈模式、板子布局、MegaWizard定制以及时序分析。"

Cyclone FPGA中的PLL是实现高效时钟管理的关键组件,它提供了时钟倍频、分频、相位偏移和可编程占空比等功能,以满足系统级的时钟需求。PLL的主要任务是同步内部和外部时钟,确保高频率的内部工作时钟与低频率的外部时钟同步,并最小化时钟延迟和偏移,优化时钟到输出(TCO)和建立(TSU)时间。

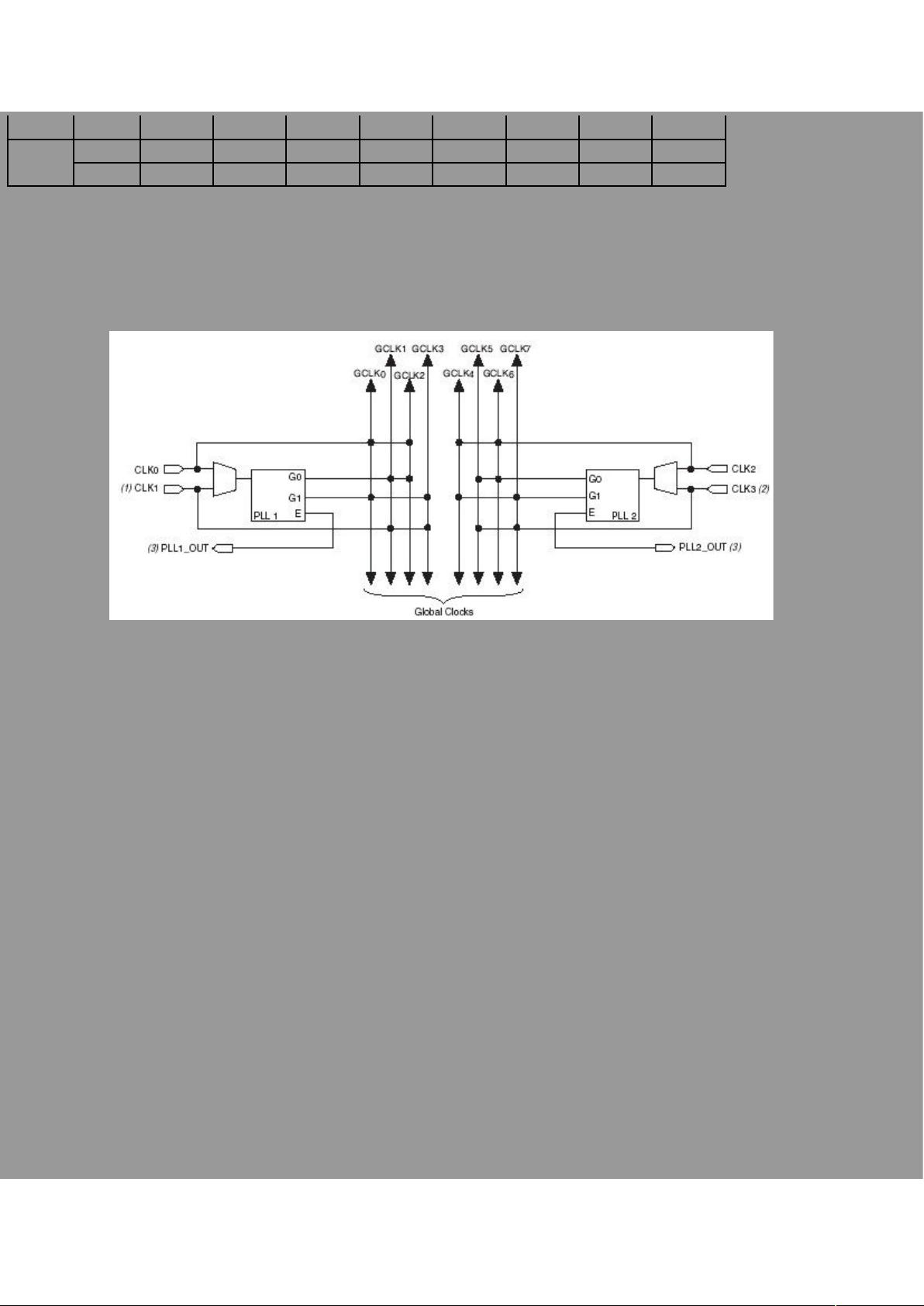

硬件结构方面,每个Cyclone FPGA可以包含多达两个PLL单元,具体数量因型号而异。PLL的特性包括但不限于:通过M/N分频器实现频率倍增或降低,最小相位偏移可达156皮秒,可编程占空比调整,以及内部和外部的时钟输出。每个PLL通常有两个内部时钟输出和一个外部时钟输出。不过,某些封装选项可能不支持所有功能,例如某些EP1C系列器件可能不支持LVDS输出或外部时钟输出。

PLL的工作原理涉及多个组件,如相位频率检测器(PFD),它比较参考输入时钟和反馈时钟的相位,产生上升或下降信号来调整压控振荡器(VCO)。VCO根据这些信号改变其频率,从而实现相位同步。PLL还包括一个低通滤波器(LPF)和一个电压控制振荡器,它们协同工作以稳定频率并减小噪声。

在软件层面,Altera的Quartus II工具使得在Cyclone FPGA中启用和配置PLL变得简单,无需额外的外部器件。用户可以通过软件设置M/N分频器的值,设定相位偏移,以及调整占空比等参数,以满足特定应用的需求。

MegaWizard是Quartus II的一部分,提供了定制PLL配置的界面,允许用户根据设计需求选择特定的PLL功能和参数。此外,良好的板子布局对于优化PLL性能至关重要,需要考虑信号完整性、电源稳定性以及噪声抑制等因素。

时序分析是设计过程中不可或缺的一环,它帮助开发者确保设计满足时序约束,避免由于时钟偏移和延迟导致的错误。Quartus II软件提供了强大的时序分析工具,可以对PLL产生的时钟路径进行深入分析,确保设计的正确性和可靠性。

Cyclone FPGA中的PLL是实现高性能、灵活的时钟管理解决方案的关键,它结合了硬件和软件工具,以适应各种复杂的数字系统需求。通过理解其工作原理和正确配置,设计师可以充分利用PLL的优势,实现高效的系统设计。

相关推荐

gary6788

- 粉丝: 0

最新资源

- Asp.net进度条实现及源码分享

- 基于蒙特卡洛的协作通信仿真研究

- 《计算机程序设计艺术》全三卷高清版解读

- HTML5实战教程:打造幽灵按钮源代码

- 掌握Scikit-Learn与TensorFlow的机器学习实战

- JSON编辑工具:HiJson 2.1.2 - 可视化结构化编辑

- 浪漫爱情主题PPT模板:小天鹅与玫瑰背景设计

- Java在线计算器实现:基础与科学版功能解析

- ES Head插件离线版使用指南

- 实现HTML页面的自动及手动轮播图效果

- aapt工具包: 多平台APK解析解决方案

- ThinkPHP5与PHP7入门实践范例

- Python脚本实现自动归类文件至指定目录

- C#生成并加密注册码源码解析

- 数据分析专用3D立体柱状图商务PPT模板下载

- Android Viewpager滑动切换图片与监听点击案例