where N is short for SerialClockNDiv. This 4-bit component can take a value from 0 to 15, so the

resulting 2

N

divisor can take a value from 1 to 32,768.

For serial-encoder protocols with an explicit clock signal, the resulting frequency is the frequency of the

clock signal that is output from the ACC-84E’s IC to the encoder. For “self-clocking” protocols without

an explicit clock signal, this frequency is the input sampling frequency, and will be 20 to 25 times higher

than the input bit rate f

bit

. Refer to the instructions for the particular protocol for details.

The component SerialTrigClockSel controls which Power PMAC clock signal causes the encoder to be

triggered. This single-bit component is set to 0, the encoder will be triggered on the phase clock; if it is set

to 1, the encoder will be triggered on the servo clock. If the encoder feedback is required for commutation

rotor angle feedback, it should be triggered on the phase clock; otherwise it can be triggered on the servo

clock.

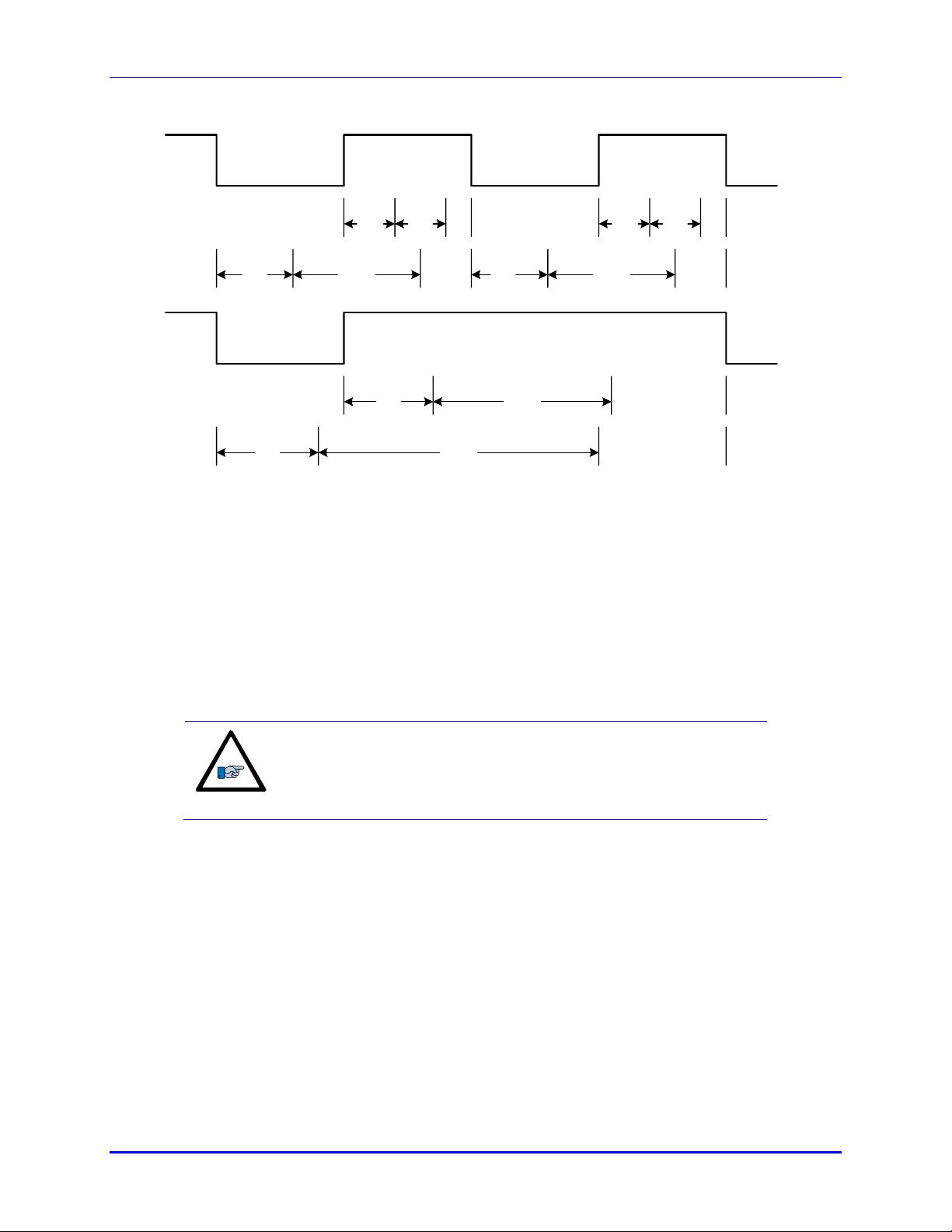

The component SerialTrigEdgeSel controls which edge of the clock signal (phase or servo) selected by

SerialTrigClockSel initiates the triggering process. If this single-bit component is set to 0, the triggering

process starts on the rising edge; if it is set to 1, the triggering process starts on the falling edge.

Power PMAC software expects to have the resulting encoder data available to it immediately after the

falling edge of the relevant phase or servo clock signal, which interrupts the processor to initiate the

activity that reads this data. Since minimum delay from trigger to use is desirable, it is better to start the

triggering on rising clock edge if the data can be fully transferred before the falling edge. If this is not

possible, the falling edge should be used to start the triggering process.

It is best to choose the edge that minimizes the delay between the triggering of the encoder and its use by

the Power/Turbo PMAC software. The software will use the received encoder value immediately after the

falling edge of the phase clock for commutation feedback, and immediately after the falling edge of the

servo clock for servo feedback.

If you are using the serial encoder data for commutation feedback, you must trigger using the phase clock

in order to get new data every phase cycle. If there is sufficient time to receive the data in one half of a

phase clock cycle, you should use the rising edge of the phase clock to trigger. For example, at the default

phase clock frequency of 9 kHz, a clock cycle is 110 µsec. If the serial encoder data can be received

within 55 µsec, the rising edge should be used. If not, the falling edge must be used.

If you are only using the serial encoder data for servo, and not commutation, feedback, the servo clock

can be used for the trigger. However, it is still advisable to use the phase clock if possible to minimize the

delay. When using the servo clock, as with the phase clock, use the rising edge if possible for the trigger,

and the falling edge only if required.

Remember that the servo clock signal is low only for one half phase clock cycle. For example, with the

default 9 kHz phase clock and 2.25 kHz servo clock, the servo clock is low for only a half of 110 µsec

phase clock cycle, and the delay from the rising edge to the next falling edge is 385 µsec.

The component SerialTrigDelay specifies the delay from the specified clock edge to the actual start of the

output signal that will trigger the encoder response, in units of the serial encoder clock. A non-zero value