华师网络学院数字电路作业解答:逻辑表达式与波形分析

版权申诉

PDF格式 | 1.53MB |

更新于2024-08-20

| 60 浏览量 | 举报

1. TTL电路及逻辑表达式与波形图

在给出的题目中,涉及到了一个TTL电路,要求根据输入A、B、C的波形,推导出输出逻辑表达式并绘制输出Y的波形图。TTL电路通常用于数字逻辑设计,其中的逻辑关系可能包括与(AND)、或(OR)、异或(XOR)等基本运算。解题时,需要根据电路的结构和TTL门的特性,分析各输入信号如何组合形成输出信号,然后依据TTL门的延迟特性画出完整的波形图。

2. 边沿D触发器的次态逻辑表达式与状态转换

边沿D触发器是一种存储电路,它根据CP(时钟脉冲)的上升沿来更新其状态。题目要求写出次态逻辑表达式,即下一个状态取决于当前状态和输入信号A。同时,根据给出的CP和A波形,需要描绘触发器的状态转移过程。

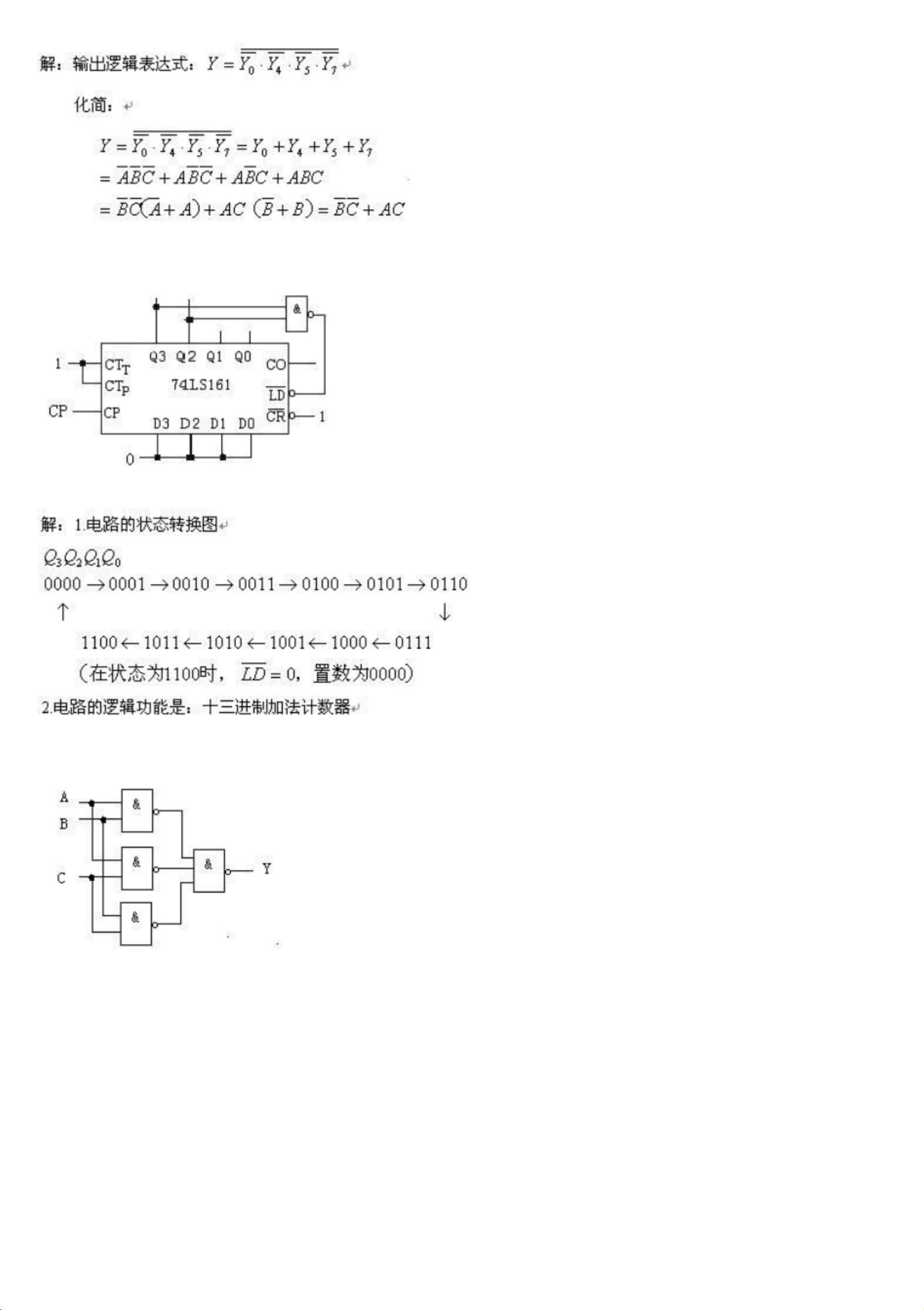

3. 译码器与非门逻辑电路的表达式

74LS138是一个8-3线译码器,它将3位输入编码成8位输出。与非门在此电路中的作用可能是组合或条件控制输出。要求写出最简的输出逻辑表达式,这需要对译码器的工作原理和逻辑功能有深入理解。

4. 同步十六进制计数器的功能与状态转换图

74LS161是一个四进制同步计数器,可以实现从0000到1111的循环计数。解题时,首先需要根据电路图确定计数规则,然后绘制状态转换图,描述每个状态到下一个状态的转移,并解释其计数功能。

5. 译码器与非门逻辑电路的逻辑表达式简化

同样,这个题目涉及的是将复杂逻辑电路简化为最简的与或式,需要对输入信号的逻辑关系进行分析,利用逻辑代数规则进行化简。

6. JK触发器的时序分析

两个JK触发器构成的时序电路,需要求出时钟方程和状态方程,这涉及到触发器的置位(J)和复位(K)输入,以及它们如何影响触发器的状态。波形图会展示输入信号和触发器状态随时间的变化。

7. ROM逻辑表达式与存储容量

对于给定的ROM(Read-Only Memory),存储容量可通过地址线数和位线数计算得出。解题时需明确存储单元的数量,然后写出Y1、Y2的逻辑表达式,考虑地址映射和数据存储的规律。

8. D触发器状态方程、状态转换图与功能

三个D触发器构成的电路,需要确定状态方程,即每个触发器的状态如何依赖于前一时刻的状态和输入信号。状态转换图描绘了状态之间的变化,而电路功能则解释了整个系统的功能和工作原理。

9. 边沿T触发器的逻辑表达式与状态波形

T触发器类似于D触发器,但只在CP的下降沿有效。题目要求写出次态逻辑表达式,并基于给定的CP波形描绘触发器的状态变化。

10. RAM的容量、地址线与位线

RAM的存储容量由地址线和位线决定,解题时需根据图示计算总存储单元数量,进而确定容量。地址线和位线的数量直接影响寻址能力和数据宽度。

11. 多输入数据选择器的输出逻辑表达式

题目提供了8选1数据选择器的电路图,要求写出输入A、B、C的逻辑关系如何决定输出。需要理解数据选择器的工作原理,根据输入信号组合规则得到输出逻辑表达式,并画出相应的输出波形。

这些题目涵盖了数字逻辑设计的基础概念,包括触发器、译码器、计数器、存储器和数据选择器等,需要结合电路结构、逻辑关系和时序分析进行解答。

相关推荐

普通网友

- 粉丝: 4

最新资源

- MFC实现鼠标精确定位与坐标输出教程

- SpringBoot多语言ORM框架示例项目解析

- TOMEXAM v2.1:跨平台免费在线考试系统

- Java实现的字母打字练习游戏代码

- Discuz! IN-CLUB模板:网页模版设计与开发指南

- VC++6.0中使用MFC实现WinSocket编程实例教程

- STM32与DS18B20温度传感器在Proteus中的仿真实践

- Bezier曲线与曲面细分技术实践

- SiteFactory奥运主题整站模板开发指南

- iOS 12.4真机调试包的下载与Xcode设置指南

- ASP.NET实现多文件上传的功能详解

- AEQC-Tools: 异构网络地震数据检索与数据库完善工具

- ASP汽车超市销售系统毕业论文与源代码详细介绍

- Bo-Blog Skin05模板:简洁网页设计的新选择

- 免费批量字符修改软件:编程与网站开发利器

- 用MapX实现地理信息系统开发教程