提升RF工程师效率:ADF4356/ADF5356 PLL器件相位校准与控制策略

154 浏览量

更新于2024-08-28

收藏 554KB PDF 举报

在现代无线通信和射频系统设计中,了解ADF4356/ADF5356这样的高性能PLL器件的相位校准和控制至关重要。锁相环(PLL)作为核心组件,通过鉴相器精确地跟踪并保持反馈信号与参考信号之间的相位一致,从而实现频率锁定。这些器件广泛应用于上变频器/下变频器(Up/Down Converters)的本地振荡器(LO),以及高速模数转换器(ADC)和数模转换器(DAC)的时钟源。

以前,由于对效率、带宽和性能要求相对较低,相位控制可能被忽视。然而,随着技术的发展,特别是对于5G、Wi-Fi和毫米波通信等高数据速率应用,对信号的相位特性要求越来越高,如信号的重复性、可预测性和可调性。在这些应用中,相位一致性直接影响信号质量、系统性能和频谱效率。

相位测量在RF工程师的工作中是关键,因为它涉及到信号间的关系。例如,使用矢量网络分析仪(VNA)测量两端口网络(如放大器)的相位,是相对于输入相位(如S21)来评估输出相位的。而PLL内部,相位测量是相对于输入参考相位进行的,理想情况下是准确的,但实际操作中会受到非线性、温度变化、电路板布局等因素的影响,可能导致微小的相位漂移。

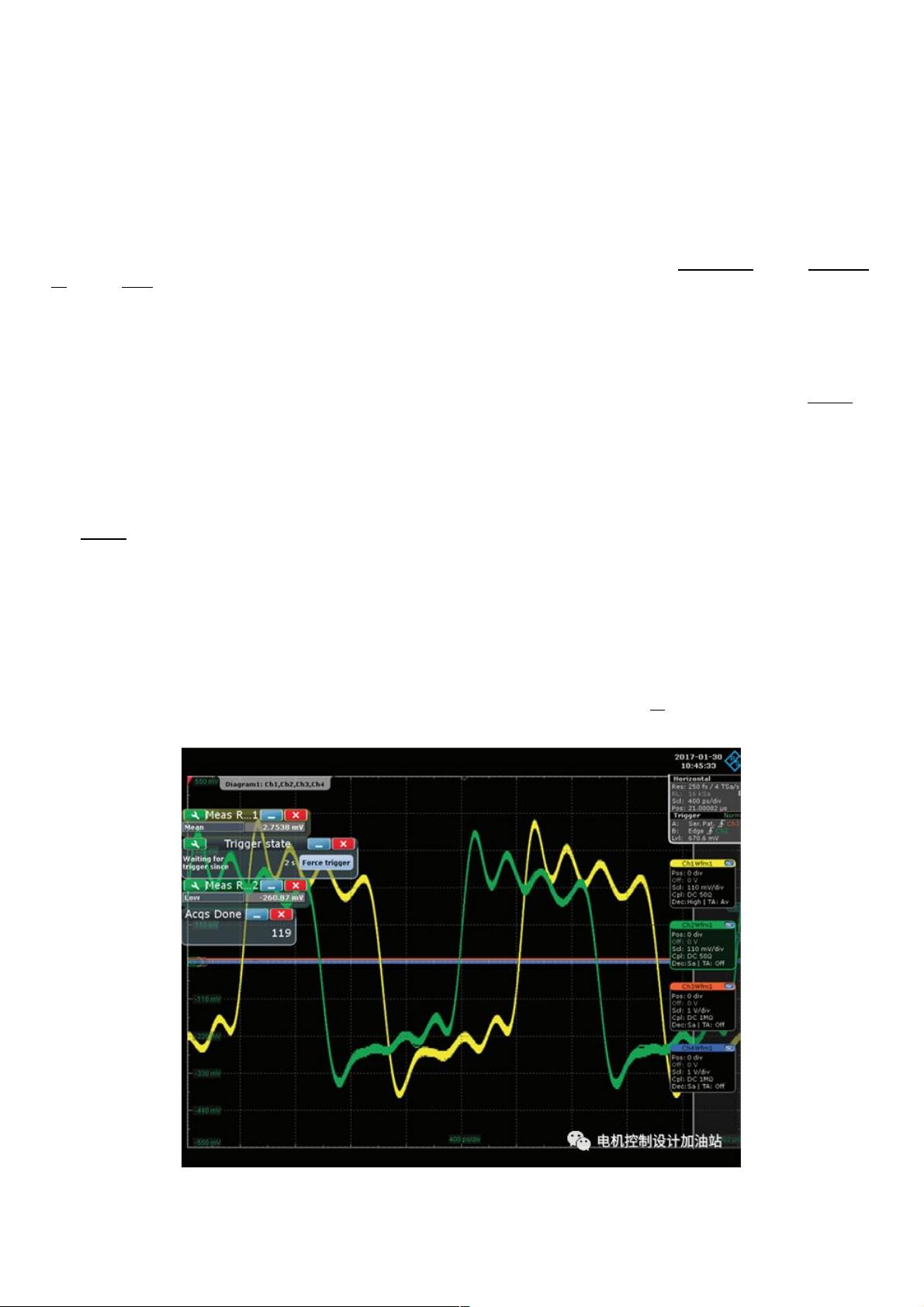

高速示波器是测量相位的一种常用工具,它能直观地比较输出相位与参考相位,但通常要求输入和输出频率满足整数倍关系,以便于解析。例如,在整数分频PLL中,输出频率是输入频率的N分之一。理解并掌握这些相位控制技巧,能够帮助RF工程师优化系统性能,提升信号稳定性,并在面对复杂环境时确保设备的稳定工作。因此,学习和熟练掌握ADF4356/ADF5356等器件的相位校准和控制是每个RF工程师必备的技能。

917 浏览量

251 浏览量

175 浏览量

207 浏览量

1410 浏览量

956 浏览量

120 浏览量

点击了解资源详情

weixin_38666785

- 粉丝: 4

- 资源: 957

最新资源

- minishift-demo:使用minishift进行本地开发的演示

- 初级java笔试题-awesome-stars:由stargazed整理的我的GitHub星星列表

- docker-plex:Ubuntu Groovy上的Plex

- jdk1.8.0_241.zip

- 商品管理

- Homitech

- DuckCreekAutomation:DuckCreekAutomation

- 首尔大卖场观感:从顾客需求出发提升服务

- prelude-ls:prelude.ls是一个面向功能的实用程序库-功能强大且灵活,几乎所有功能都可以使用。 它是用http编写的,并且是http的推荐基础库

- java笔试题算法-lbfgsb_wrapper:FortranL-BFGS-B算法的Java包装器

- JavaScriptViewEngine-master.zip

- 2019 5G+智能工厂网络及应用白皮书精品报告2020.rar

- malves0

- 销售点管理系统简介——卖场管理

- Công Cụ Đặt Hàng Của Vận Tải Hoa Kiều-crx插件

- gdblib:Go库,用于使用MI接口与gdb调试器接口