数字逻辑电路:触发器的工作原理与分类

需积分: 50 117 浏览量

更新于2024-07-23

收藏 3.04MB PPT 举报

"数字逻辑电路-CH4.PPT 涵盖了数字逻辑电路的第四章内容,重点讨论了组合逻辑电路和时序逻辑电路,特别是时序逻辑电路中的触发器,包括其特点、分类、工作原理、逻辑功能以及波形图。文件还涉及了同步触发器和边沿触发器的细节,并列出了考核内容和讲解思路。"

在数字逻辑电路中,组合逻辑电路和时序逻辑电路是两个关键概念。组合逻辑电路的特点是输入信号改变会立即引起输出信号的相应变化,但无法保存信息。而时序逻辑电路则可以存储信息,它具有反馈机制,能够根据输入信号改变输出并保持某种状态。

时序逻辑电路的核心组件是触发器,它有以下几个关键特点和要求:

1. 触发器有两个稳定状态,通常用0和1表示,用于存储信息。

2. 能够接收输入信号,保存当前状态(现态),并根据输入产生新的状态(次态)。

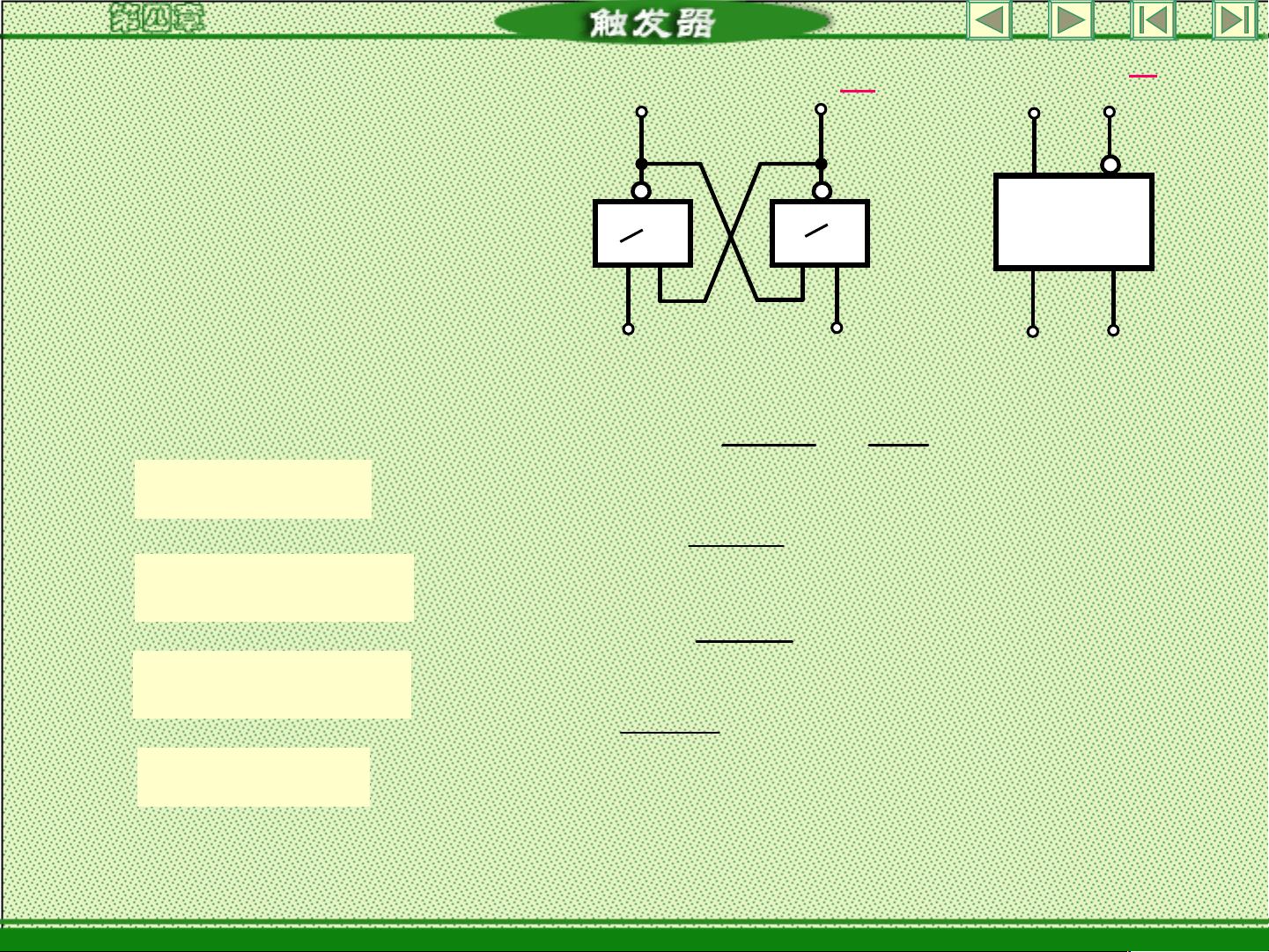

触发器按照电路结构和工作特点可分为基本触发器、同步触发器和边沿触发器;按照逻辑功能则分为RS、JK、D和T触发器等。其中,RS触发器是最基础的一种,由与非门组成。

RS触发器的电路结构包含两个与非门,有输入端R(Reset)和S(Set),以及输出端Q。其工作特点和原理如下:

- 当R为1且S为0时,触发器被“复位”,Q输出为0,即处于0态。

- 当R为0且S为1时,触发器被“置位”,Q输出为1,即处于1态。

- 如果R和S同时为1,则触发器处于不确定状态,因为没有明确的输入指令来决定Q的下一个状态。

- R和S先后撤销时,Q的下一个状态取决于哪个信号先撤销,R先撤销时保持1态,S先撤销时保持0态。

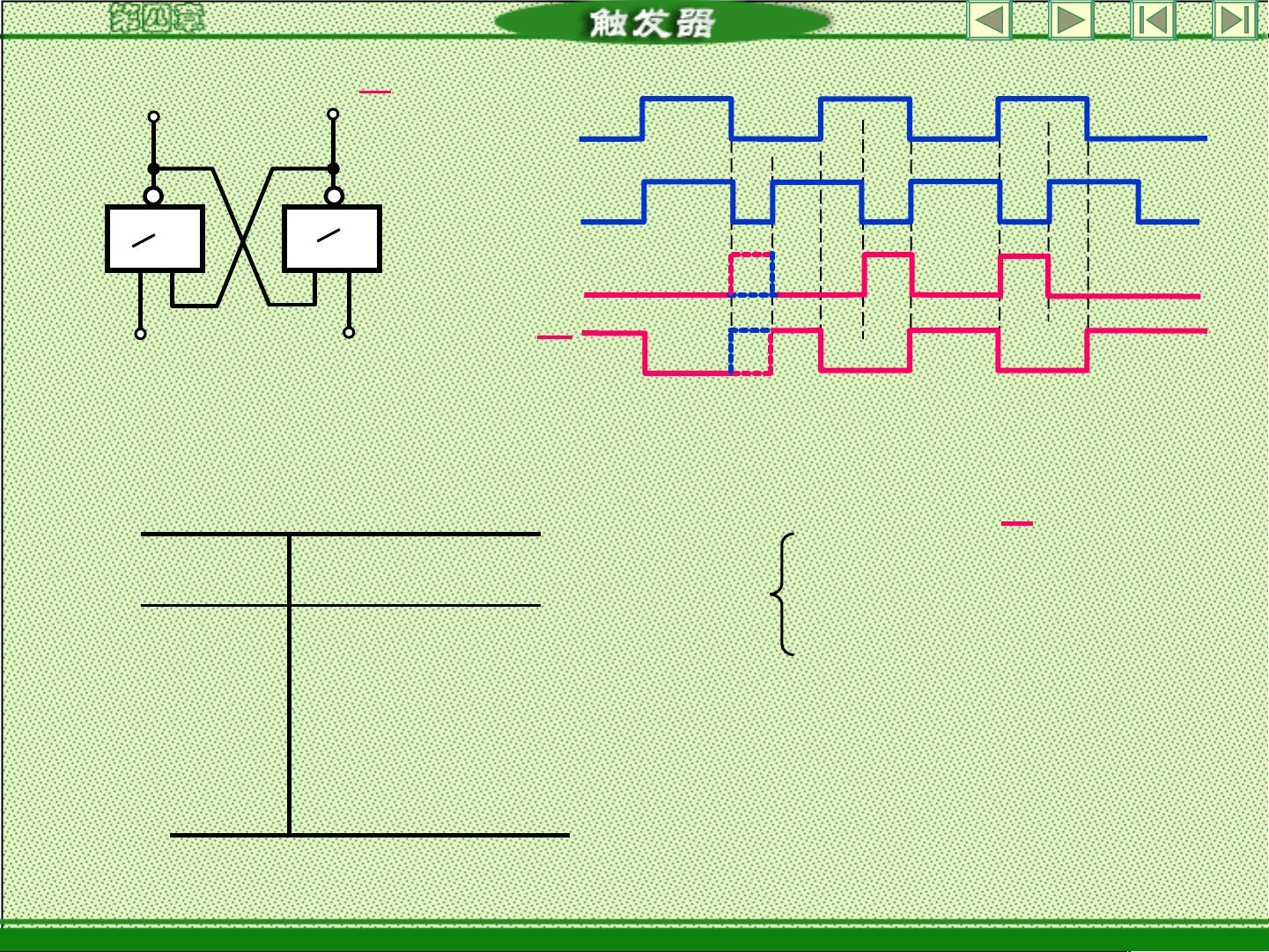

在实际应用中,为了消除不确定状态,通常避免R和S同时为1的情况。RS触发器的简化波形图展示了输出状态随输入信号变化的过程,包括输出电平的转换和可能存在的延迟。

此外,特性表和特性方程是描述触发器行为的重要工具,它们可以用来总结触发器的所有可能状态和状态转移情况。例如,RS触发器的特性表显示了RS输入组合与输出Q之间的关系。

同步触发器和边沿触发器的讲解则更深入地探讨了电路的同步工作方式,即所有触发器在同一时钟信号控制下更新状态,以及基于时钟边沿(上升沿或下降沿)进行状态转换的特性,这些在高级的时序逻辑设计中至关重要。

考核内容可能包括对边沿触发器的电路结构、工作特点、逻辑功能的理解,以及绘制波形图和解析特性方程的能力。讲解思路可能引导学生从电路结构入手,理解工作原理,通过分析波形图来掌握触发器的行为模式,最后通过特性方程来加深对触发器功能的理解。

2021-08-16 上传

2022-06-17 上传

2017-08-10 上传

2009-03-09 上传

2021-08-11 上传

2009-03-06 上传

MINGMINGFEI33

- 粉丝: 0

- 资源: 2

最新资源

- JHU荣誉单变量微积分课程教案介绍

- Naruto爱好者必备CLI测试应用

- Android应用显示Ignaz-Taschner-Gymnasium取消课程概览

- ASP学生信息档案管理系统毕业设计及完整源码

- Java商城源码解析:酒店管理系统快速开发指南

- 构建可解析文本框:.NET 3.5中实现文本解析与验证

- Java语言打造任天堂红白机模拟器—nes4j解析

- 基于Hadoop和Hive的网络流量分析工具介绍

- Unity实现帝国象棋:从游戏到复刻

- WordPress文档嵌入插件:无需浏览器插件即可上传和显示文档

- Android开源项目精选:优秀项目篇

- 黑色设计商务酷站模板 - 网站构建新选择

- Rollup插件去除JS文件横幅:横扫许可证头

- AngularDart中Hammock服务的使用与REST API集成

- 开源AVR编程器:高效、低成本的微控制器编程解决方案

- Anya Keller 图片组合的开发部署记录