硬布线与微程序设计:8位CPU实现与状态图详解

本篇文档介绍了如何通过硬布线和微程序控制器两种方法设计一个满足特定规范的简单CPU。设计目标是一个能够访问64字存储器(每字8位),并具有基本指令集的CPU。以下是关键知识点的详细说明:

1. **CPU规格**:

- 字长:8位数据寄存器D[7~0]

- 寻址范围:6位地址寄存器AR(通过A[5~0]提供地址)

- 指令集:

- COM(取反):操作码00XXXXXX

- JREL(相对转移):PC递增并跳转到新地址

- OR(或运算):操作码10AAAAAA

- SUB1(减一后与):操作码11AAAAAA

2. **寄存器**:

- 累加器AC:8位,用于处理数据

- 地址寄存器AR:6位,存储当前指令地址

- 程序计数器PC:6位,指示下一条指令地址

- 数据寄存器DR:8位,接收和发送数据

- 指令寄存器IR:2位,存放操作码

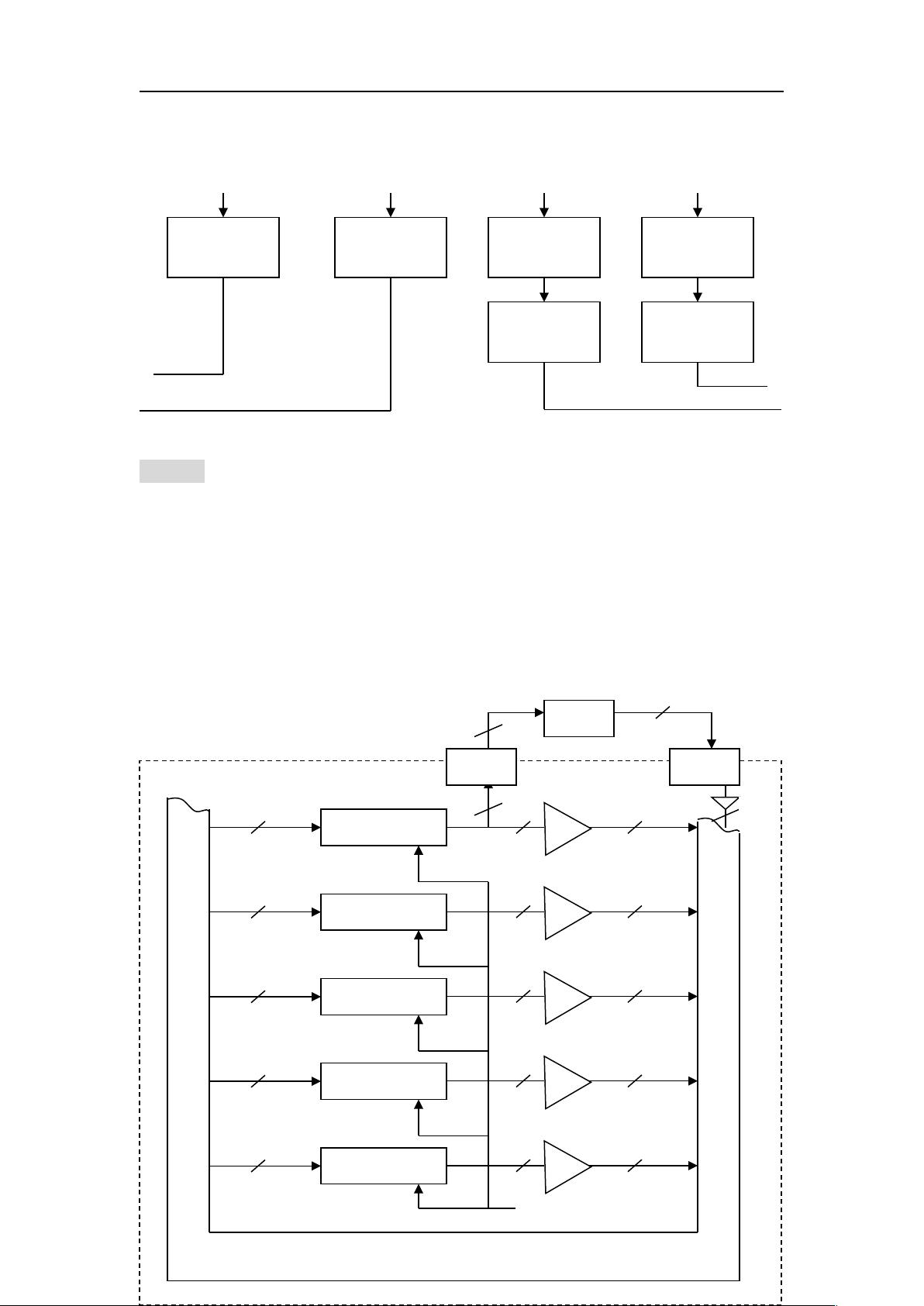

3. **状态转换流程**(硬布线方法):

- FETCH1:PC内容复制到AR,准备读取内存

- FETCH2:读取内存到DR,更新PC指向下一指令

- FETCH3:将DR的高两位到IR,低6位到AR

4. **指令译码**:

- 微观上,根据IR的内容执行不同的操作:COM(00)对应取反操作,JREL(01)进行相对跳转,OR(10)执行逻辑或,SUB1(11)执行减一与操作。

5. **指令执行**:

- 对于每条指令,CPU执行相应操作,例如COM指令对累加器AC执行取反操作。

在硬布线设计中,CPU的状态机会直接映射到硬件电路,每一步操作都是物理连接的结果。而在微程序控制器设计中,CPU包含一个控制单元,它会执行预先编码的微程序序列来完成指令的处理,这种方法通常更灵活,但也更为复杂。

这个课程设计任务要求学生深入理解CPU的基本结构和工作原理,通过设计实现一个简单的CPU,不仅涉及到逻辑门级的硬件设计,也涵盖了指令集架构和指令执行流程的理解。无论是硬布线还是微程序控制器,设计过程中都需要考虑时序逻辑、数据通路以及指令的执行路径。这是一项涉及计算机体系结构基础的重要实践任务。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2011-03-07 上传

2017-05-12 上传

2012-12-27 上传

2021-02-09 上传

2009-12-04 上传

2020-07-19 上传

huhushengcai

- 粉丝: 4

- 资源: 1

最新资源

- LettersAnimationLayout:具有悬浮效果的三重面板布局中的分布式字母动画

- xproPage:desarrollo de la pagina de xpro cnc

- Artificial-Intelligence:“真正的问题不是人工智能的生存威胁。相反,它在于道德人工智能系统的发展。” ——拉娜·埃尔·卡利乌比

- Thingifly-crx插件

- C:C语言初学者基础程序

- Audio_Mixe2028551122006.zip

- workos_ruby:Ruby应用程序示例,它将利用Google OAuth登录用户

- Wencor.com order status check button-crx插件

- Unity内嵌入网页插件 ZFBrowser

- electron-v8.5.5-win32-x64.zip

- 行业分类-设备装置-不同基底硬度体外细胞培养平台的建立方法.zip

- 神经网络

- rskclitools:用于RSK和以太坊区块链WIP的命令行工具

- 国外潮流菜单导航自带谷歌优化特效代码

- mkvtoolnix-batch-tool:批处理视频和字幕处理程序,可帮助您从视频库中添加或删除字幕

- 可自动缩放的列表视图