"CS1804_U201814755_彭子晨_5段流水CPU设计报告"

需积分: 0 64 浏览量

更新于2024-01-17

收藏 4.96MB DOCX 举报

2021计算机组成原理课程设计报告

本课程设计报告是对计算机组成原理课程进行的一次全面实践与总结,旨在帮助学生深入理解计算机各个部件的组成与原理,并通过设计与实践加深对课程知识的理解与掌握。本报告以5段流水CPU设计为题,由华中科技大学计算机科学与技术专业CS1804班级U201814755号学生彭子晨完成。

一、课程设计概述

1.1 课设目的

本课程设计旨在通过实践操作与理论学习相结合,加深学生对计算机组成原理课程知识的理解与掌握,提高学生的动手能力和实际应用能力。

1.2 设计任务

本课程设计的主要任务是设计一款5段流水CPU,并通过Verilog硬件描述语言(HDL)进行实现,最终在FPGA开发板上进行验证与测试。

1.3 设计要求

基于RISC-V指令集架构设计一款简化的5段流水CPU,要求能够正确执行RISC-V指令集中的常见指令,包括算术逻辑运算、数据传输、分支跳转、访存操作等。

二、设计过程与方法

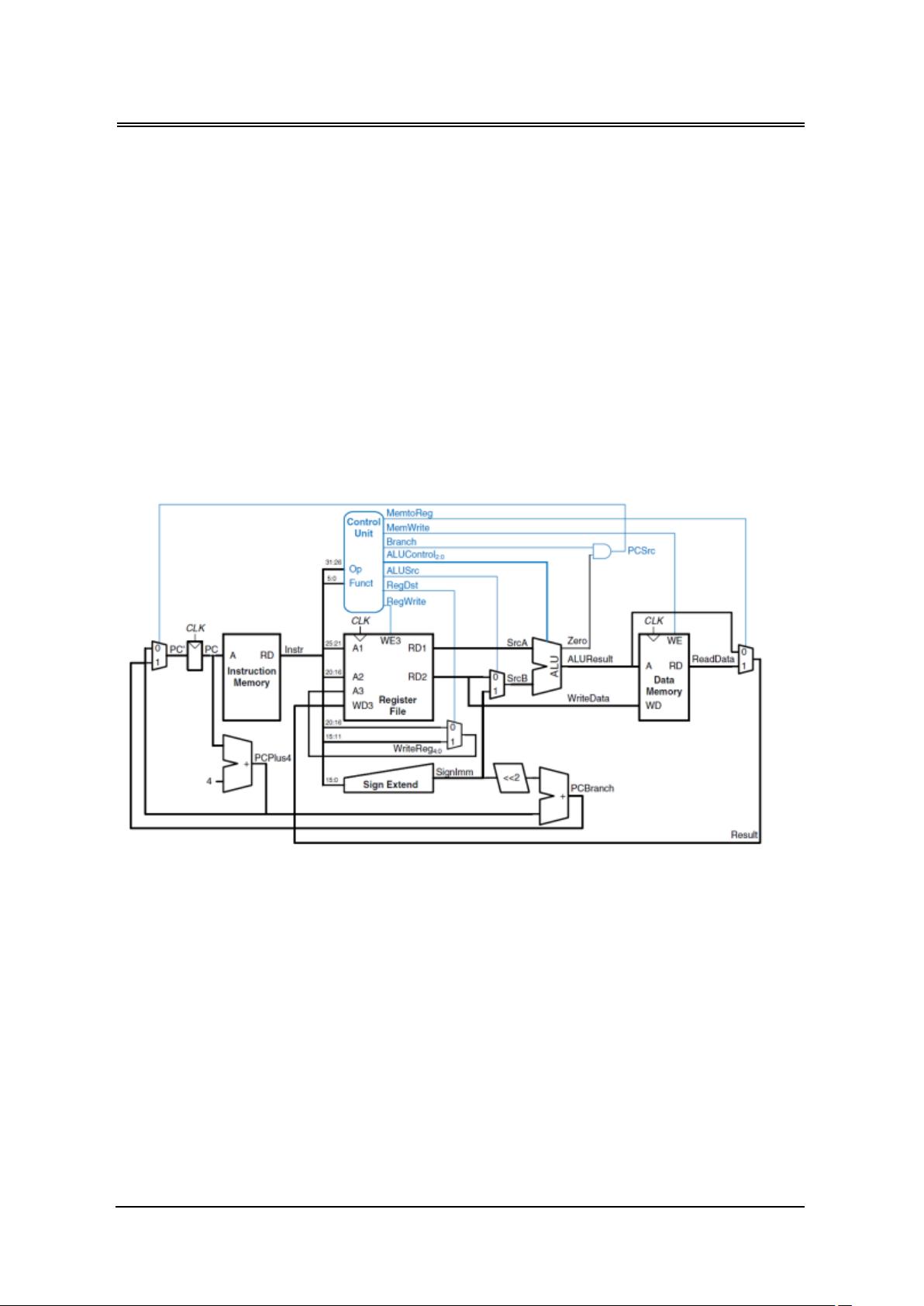

2.1 CPU整体结构设计

根据RISC-V指令集架构,设计CPU的整体结构,包括指令寄存器、程序计数器、控制逻辑等模块,并利用Verilog HDL进行描述。

2.2 流水线模块划分

将CPU设计为5段流水线结构,包括取指、译码、执行、访存和写回五个阶段,通过合理的模块划分和数据传递方式实现流水线数据的传输与处理。

2.3 指令集实现与优化

根据RISC-V指令集要求,对CPU进行指令集实现,并优化指令执行的效率和延迟,以提高CPU的整体性能。

2.4 Verilog HDL实现

采用Verilog HDL进行CPU的硬件描述,并利用FPGA开发板进行逻辑综合和验证,确保CPU的正确性与稳定性。

三、设计实现与测试验证

3.1 CPU功能验证

通过编写汇编程序,并将其烧录到FPGA开发板上,验证CPU能够正确执行程序并输出预期的结果。

3.2 性能测试与优化

利用性能测试工具对CPU进行性能测试,并根据测试结果进行优化,提高CPU的运行效率和稳定性。

3.3 功耗与面积优化

通过对CPU的逻辑综合和功耗测试,对CPU的功耗与面积进行优化,以提高CPU的整体性价比。

四、课程设计总结

4.1 设计成果与展望

通过本次课程设计,成功设计并实现了一款5段流水CPU,并在FPGA开发板上进行了验证与测试。对于课程设计的成果表示满意,并对未来的深入研究与拓展表现出浓厚的兴趣。

4.2 学习收获与感想

通过课程设计的过程,加深了对计算机组成原理知识的理解与掌握,提高了对Verilog HDL的应用技能,培养了解决实际问题的能力与动手能力。

4.3 感谢与致谢

在课程设计过程中,得到了老师与同学们的大力支持与帮助,在此表示由衷的感谢与感激。

五、参考文献

1. 《计算机组成与设计:硬件/软件接口》(David A. Patterson, John L. Hennessy 著)

2. 《计算机体系结构:量化研究方法》(John L. Hennessy, David A. Patterson 著)

总之,通过本次课程设计,彭子晨同学在计算机组成原理课程中得到了全面的实践锻炼与知识总结,成功设计并实现了一款5段流水CPU,取得了令人满意的成果。期待彭子晨同学在今后的学习与科研道路上能够不断努力,取得更加辉煌的成就!

2022-07-05 上传

2022-08-08 上传

2022-08-08 上传

点击了解资源详情

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

深层动力

- 粉丝: 26

- 资源: 318

最新资源

- 中国项目管理师培训讲义——费用管理

- SWF:一些用于处理SWF文件的python脚本

- 作品集:专为展示我的所有作品而创建的项目

- neural_network_projects:这是一些基本的神经网络

- STSensNet_Android:“ ST BLE StarNet” Android应用程序源代码-Android application source code

- SLIC-ImageSegmentation:基于SLIC图像分割算法实现一个比PS魔棒工具还方便的抠图工具

- yet-another-istanbul-mocha-no-coverage

- 四卡功能

- android 一个杀进程 程序分享,包含源代码-网络攻防文档类资源

- babel_pug_project:通过babel,pug,node,express进行Web服务器教育.....

- 爱普生7710 7720l免芯片固件刷rom附安装说明

- GenericInstsBenchmark

- AK_Lab2

- MADSourceCodes:“使用Android移动应用程序开发”课程源代码-Android application source code

- themeweaver:使用设计标记在浏览器中创建kick-ass IDE主题!

- oo-way-getonboard中的战舰:GitHub Classroom创建的oo-way-getonboard中的战舰