VHDL上机指南:基于Xilinx ISE的工程创建与仿真

需积分: 9 78 浏览量

更新于2024-09-20

收藏 238KB DOC 举报

"VHDL上机手册,主要讲解如何基于Xilinx ISE进行VHDL设计,包括软件运行、工程创建、VHDL代码编写、仿真及Testbench的建立和输入波形设置等步骤。"

VHDL是硬件描述语言(Hardware Description Language)的一种,常用于数字电路设计,特别是在FPGA(Field-Programmable Gate Array)开发中。Xilinx ISE是一款集成开发环境,用于设计、仿真和实现基于Xilinx FPGA和 CPLD 的VHDL项目。

1. **ISE软件的运行**

Xilinx ISE软件提供了从设计输入、编译、仿真到硬件编程的完整工作流程。启动软件通常是通过点击“开始”菜单中的相应程序快捷方式,选择Xilinx ISE 7.1的"Project Navigator"。

2. **创建一个新工程**

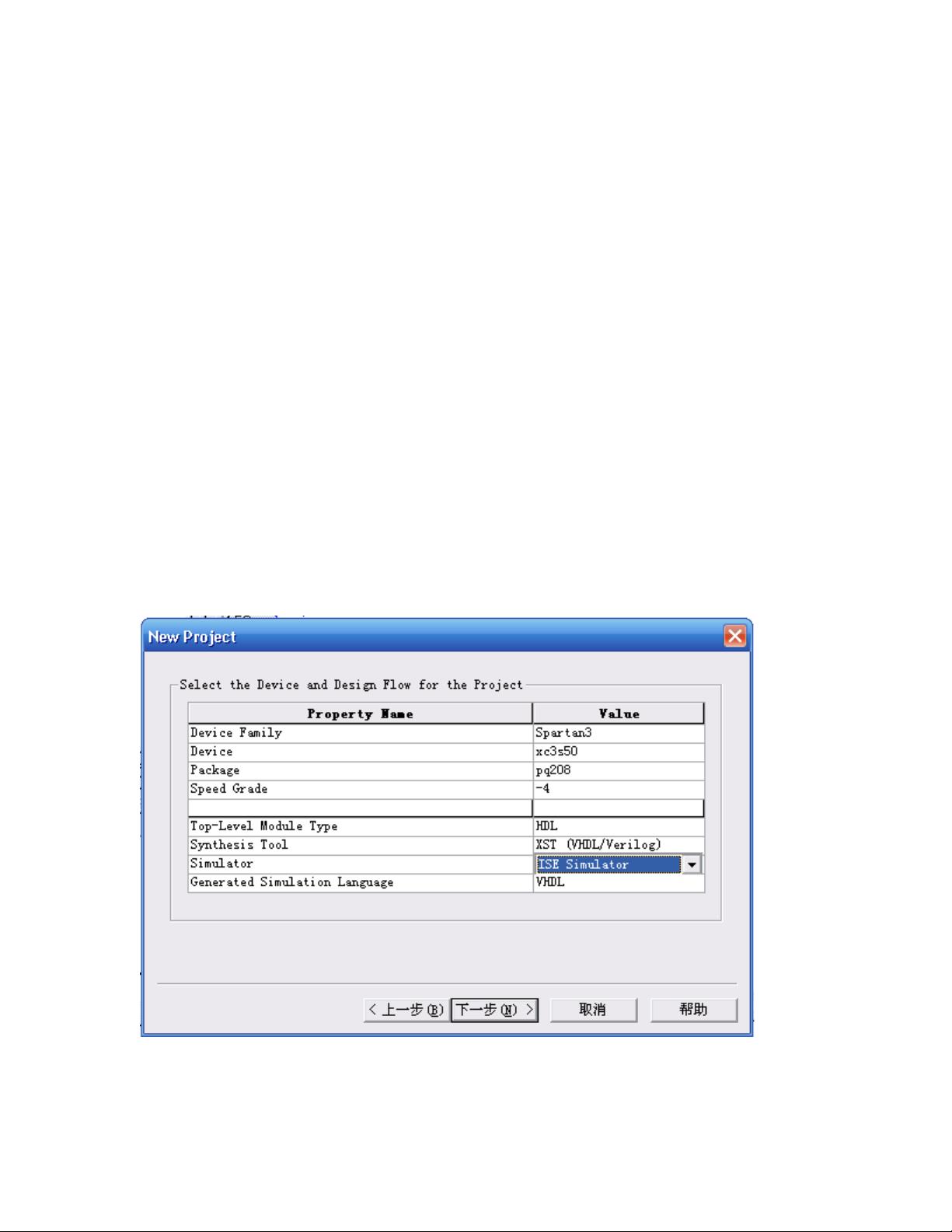

创建新工程是VHDL设计的第一步。在ISE中,用户需要选择"File"菜单,然后点击"New Project…"。在弹出的对话框中,选择工程存储的位置,并输入工程名称。默认情况下,系统会根据工程名创建一个同名的目录。选择HDL作为顶层模块类型,这表示设计将以VHDL代码的形式存在。

3. **创建一个VHDL源文件框架**

在工程中,VHDL源文件是实现逻辑功能的核心。用户可以使用ISE的文本编辑器来创建新的VHDL文件,输入描述电路逻辑的VHDL代码。

4. **输入VHDL程序**

VHDL程序由实体、结构体、包、配置等组成。实体描述外部接口,结构体描述内部逻辑。用户需要按照VHDL语法规则编写代码,定义信号、组件、过程和函数,以实现所需的功能。

5. **仿真**

为了验证VHDL代码的功能,需要进行仿真。在ISE中,可以使用ISim仿真工具。首先,将VHDL代码编译成网表,然后设置仿真参数,包括时间范围、激励信号和观察变量。最后运行仿真,观察波形图以验证设计是否满足预期。

6. **创建Testbench波形源文件**

Testbench是用于模拟设计输入和检查输出的虚拟测试环境。它通常包含一组进程,模拟实际应用中的激励信号,并通过边界扫描接口与设计的实体交互。在ISE中,创建一个单独的VHDL源文件来编写Testbench代码。

7. **设置输入仿真波形**

在仿真前,需要定义Testbench中信号的初始值和变化序列。这可以通过设置波形数据(waveform data)来实现,这些数据将在仿真过程中驱动设计的输入信号。

通过以上步骤,用户可以逐步完成一个完整的VHDL设计流程,从概念到实现,再到功能验证。理解并熟练掌握这些步骤对于使用Xilinx ISE进行VHDL设计至关重要。在实际操作中,可能还需要涉及其他高级特性,如时序分析、约束设置、IP核集成以及硬件编程等,这些都是VHDL和ISE综合应用的重要组成部分。

109 浏览量

2012-03-14 上传

2023-06-09 上传

743 浏览量

179 浏览量

134 浏览量

103 浏览量

697 浏览量

普通网友

- 粉丝: 2099

最新资源

- ASP.NET集成支付宝即时到账支付流程详解

- C++递推法在解决三道经典算法问题中的应用

- Qt_MARCHING_CUBES算法在面绘制中的应用

- 传感器原理与应用课程习题解答指南

- 乐高FLL2017-2018任务挑战解析:饮水思源

- Jquery Ui婚礼祝福特效:经典30款小型设计

- 紧急定位伴侣:蓝光文字的位置追踪功能

- MATLAB神经网络实用案例分析大全

- Masm611: 安全高效的汇编语言调试工具

- 3DCurator:彩色木雕CT数据的3D可视化解决方案

- 聊天留言网站开发项目全套资源下载

- 触摸屏适用的左右循环拖动展示技术

- 新型不连续导电模式V_2控制Buck变换器研究分析

- 用户自定义JavaScript脚本集合分享

- 易语言实现非主流方式获取网关IP源码教程

- 微信跳一跳小程序前端源码解析