Au cours de ce chapitre, les différentes étapes de l’exploration architecturale des systèmes

intégrés sur puce ont été brièvement présentées. Nous avons décrit une des méthodes de modé-

lisation du matériel, et de déploiement du logiciel sur le matériel. Nous avons ensuite identifié

le problème de la durée de l’exploration architecturale qui devient excessive en raison du grand

nombre de paramètres du système.

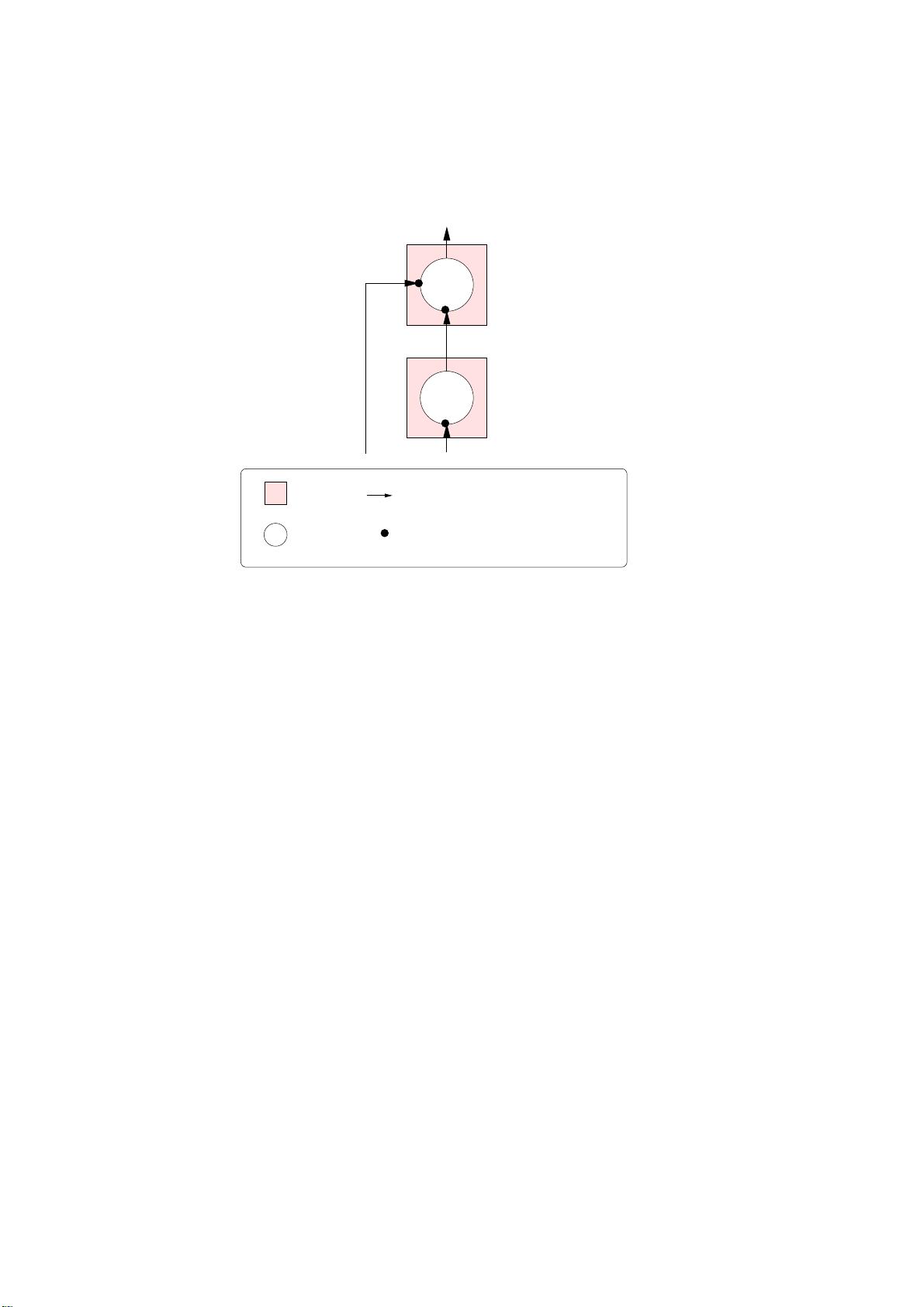

Étant donné que la durée de l’exploration architecturale dépend de la vitesse de la simulation

architecturale, le problème revient à accélérer l’exécution de la simulation. Nous avons discerné

deux facteurs majeurs : le niveau d’abstraction des modules et le moteur de simulation.

Le niveau de modélisation qui nous intéresse est le niveau CABA. La restriction quant au

niveau de modélisation permet d’envisager l’emploi d’un simulateur spécialisé orienté vers la

simulation rapide.

Nous avons identifié alors l’ordonnancement statique des processus comme étant une bonne

source d’accélération. Cette accélération peut être obtenue à condition d’enrichir les modèles

avec des informations explicitant les relations de dépendance entre les signaux d’entrée/sortie

d’un même module. Si ces informations sont partielles ou incorrectes, le déterminisme de la si-

mulation est compromis. Nous avons alors discerné deux besoins. Le premier besoin est d’établir

une méthode de modélisation où les dépendances entre les signaux d’entrée/sortie apparaissent

clairement. Le second besoin est de vérifier les relations de dépendance fournies.

L’exploration architecturale est limitée par la disponibilité des modèles de simulation rapide.

Or, nous avons constaté que les modèles RTL synthétisables sont très répandus. La génération

automatique de modules CABA à partir de ces modèles RTL est donc un enjeu important.

Au cours de ce chapitre, nous avons soulevé les questions suivantes auxquelles nous essaie-

rons de répondre :

0

第1章问题

0

在工业界存在许多可综合的RTL级别模型。由于这些模型是为逻辑综合而设计的,因此在模拟速度方面性能非常

差。从RTL版本手动编写CABA模型可能会很耗时且繁琐。人为错误经常发生。通过工具的自动化生成可以减少转

换时间和错误风险。因此,我们对从可综合RTL模型自动生成CABA级别模拟模型感兴趣。这项工作是本论文的一

个贡献之一。

0

1.3.5生成用于快速模拟的模型

0

在本章中,我们简要介绍了片上系统的架构探索的不同阶段。我们描述了一种硬件建模和软件部署的

方法之一。然后,我们确定了由于系统参数的数量庞大,架构探索的持续时间变得过长的问题。由于

架构探索的持续时间取决于架构模拟的速度,问题归结为加速模拟执行。我们确定了两个主要因素:

模块的抽象级别和模拟引擎。我们感兴趣的建模级别是CABA级别。建模级别的限制使得可以考虑使

用面向快速模拟的专用模拟器。然后,我们确定了静态进程调度作为加速的良好来源。只有在模型中

丰富了关于同一模块的输入/输出信号之间依赖关系的信息时,才能实现这种加速。如果这些信息是

部分的或不正确的,模拟的确定性将受到威胁。然后,我们确定了两个需求。第一个需求是建立一种

建模方法,其中输入/输出信号之间的依赖关系清晰可见。第二个需求是验证所提供的依赖关系。架

构探索受快速模拟模型的可用性限制。然而,我们发现可综合的RTL模型非常普遍。因此,从这些RT

L模型自动生成CABA模块是一个重要的问题。在本章中,我们提出了以下问题,我们将尝试回答:

0

1.4结论