FPGA实现的三线制同步串行通信控制器设计及其应用

44 浏览量

更新于2024-08-30

收藏 291KB PDF 举报

本文主要探讨了在EDA/PLD技术中,如何通过FPGA实现高效且简洁的三线制同步串行通信控制器的设计。该设计目标旨在简化应用系统的接口,减少硬件体积,降低功耗。文章首先概述了三线制同步串行通信的基本原理,这种通信方式因其线路少、操作简便和速度快而在航天工程等场景中广泛应用。

设计者利用FPGA作为核心硬件平台,结合VHDL硬件描述语言,构建了三线制同步串行通信控制器的功能框架,详细介绍了各个组成部分的功能和工作流程。这包括接收器、发送器、时钟管理模块、数据缓冲器以及状态机等关键模块,每个模块都在设计中起到了关键作用。

控制器IP核的接口信号被精心设计和定义,以确保与外部设备的兼容性和互操作性。在实际开发过程中,作者使用Xilinx ISE工具进行综合,而ModelSim SE则用于功能仿真,验证控制器性能的准确性和可靠性。

文章强调了三线制同步串行通信在微控制器和微处理器中的普遍应用,尤其是在需要与外围串行设备高效数据交换的场景中。然而,现有的微控制器和微处理器中较少有内置这种接口,这就促使设计者通过FPGA进行扩展,以适应特定的需求。

FPGA的优势在于其高速度、可配置性和灵活性,使得设计者能够定制化地实现三线制同步串行通信控制器,满足高速、易调试和配置灵活的要求。通过Xilinx FPGA器件,设计师成功地构建了这个IP软核,优化了硬件资源的使用,从而显著地减少了系统的体积,缩短了开发周期。

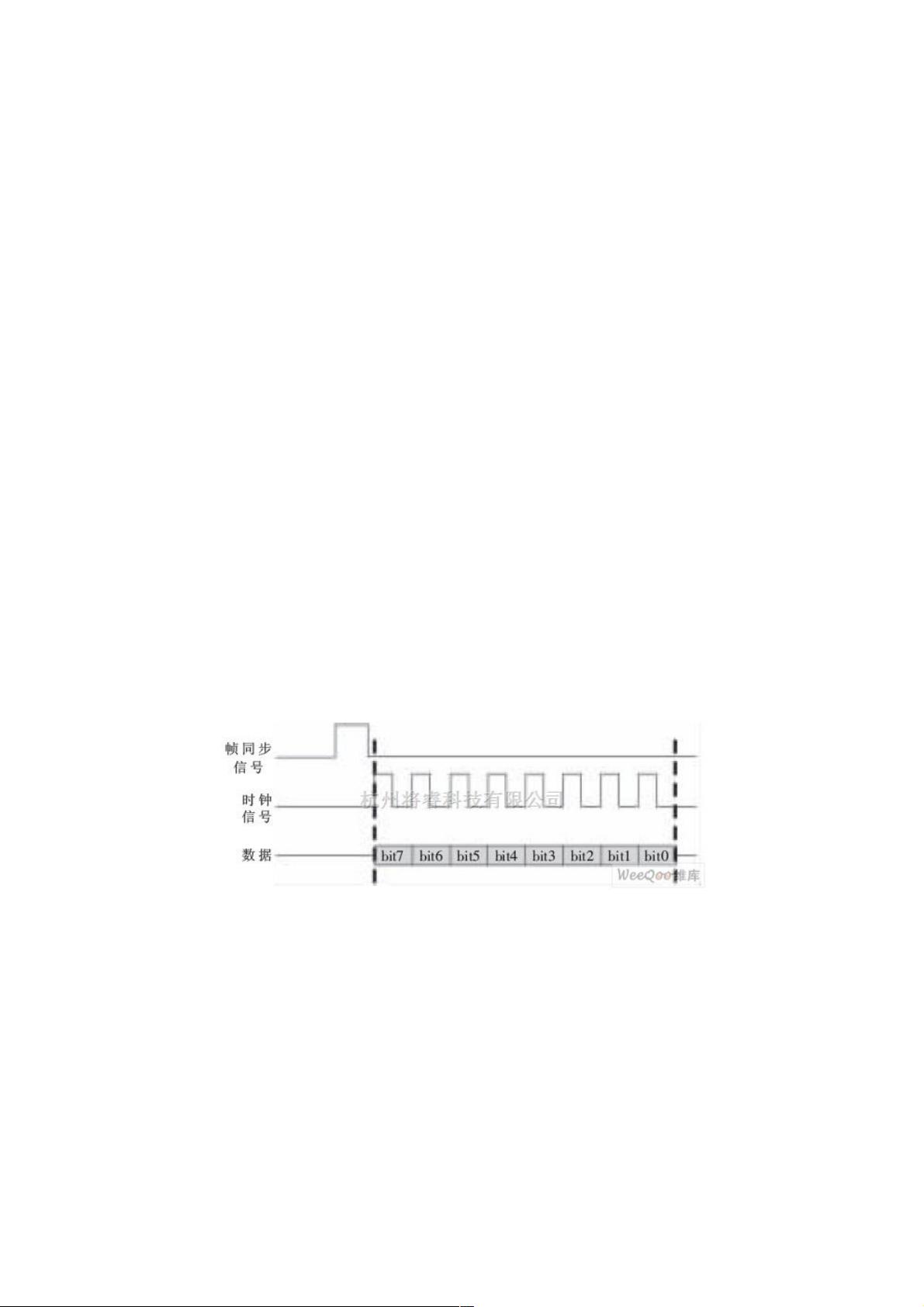

具体到技术细节,文中提到了三线制同步串行通信机制,即数据在一条数据线上按照固定的时钟顺序逐位传输,这与传统的并行通信形成了对比。在设计中,接收器负责接收来自数据线的单位数据,发送器负责将数据串行化,时钟管理确保数据传输的同步,而数据缓冲器则起到暂存和处理数据的作用。

总结来说,本文的核心内容是基于FPGA的三线制同步串行通信控制器设计方法,展示了如何通过硬件描述语言VHDL进行系统级的设计和验证,以及如何利用FPGA的特性来优化通信效率和系统性能。这对于从事嵌入式系统、通信协议设计和FPGA应用的工程师来说,是一篇实用的技术参考文献。

点击了解资源详情

133 浏览量

点击了解资源详情

231 浏览量

210 浏览量

126 浏览量

268 浏览量

130 浏览量

110 浏览量

weixin_38553381

- 粉丝: 1

最新资源

- VB通过Modbus协议控制三菱PLC通讯实操指南

- simfinapi:R语言中简化SimFin数据获取与分析的包

- LabVIEW温度控制上位机程序开发指南

- 西门子工业网络通信实例解析与CP243-1应用

- 清华紫光全能王V9.1软件深度体验与功能解析

- VB实现Access数据库数据同步操作指南

- VB实现MSChart绘制实时监控曲线

- VC6.0通过实例深入访问Excel文件技巧

- 自动机可视化工具:编程语言与正则表达式的图形化解释

- 赛义德·莫比尼:揭秘其开创性技术成果

- 微信小程序开发教程:如何实现模仿ofo共享单车应用

- TrueTable在Windows10 64位及CAD2007中的完美适配

- 图解Win7搭建IIS7+PHP+MySQL+phpMyAdmin教程

- C#与LabVIEW联合采集NI设备的电压电流信号并创建Excel文件

- LP1800-3最小系统官方资料压缩包

- Linksys WUSB54GG无线网卡驱动程序下载指南