CPLD实现RS-232串口通信:PC与嵌入式系统数据传输解决方案

27 浏览量

更新于2024-08-31

收藏 427KB PDF 举报

"EDA/PLD中的基于CPLD的RS-232串口通信实现"

本文探讨了在EDA(电子设计自动化)/PLD(可编程逻辑器件)领域中,如何利用CPLD(复杂可编程逻辑器件)实现RS-232串口通信。RS-232C是一种广泛使用的串行通信协议,它允许设备间的长距离通信,常用于PC机与嵌入式系统的数据交互。

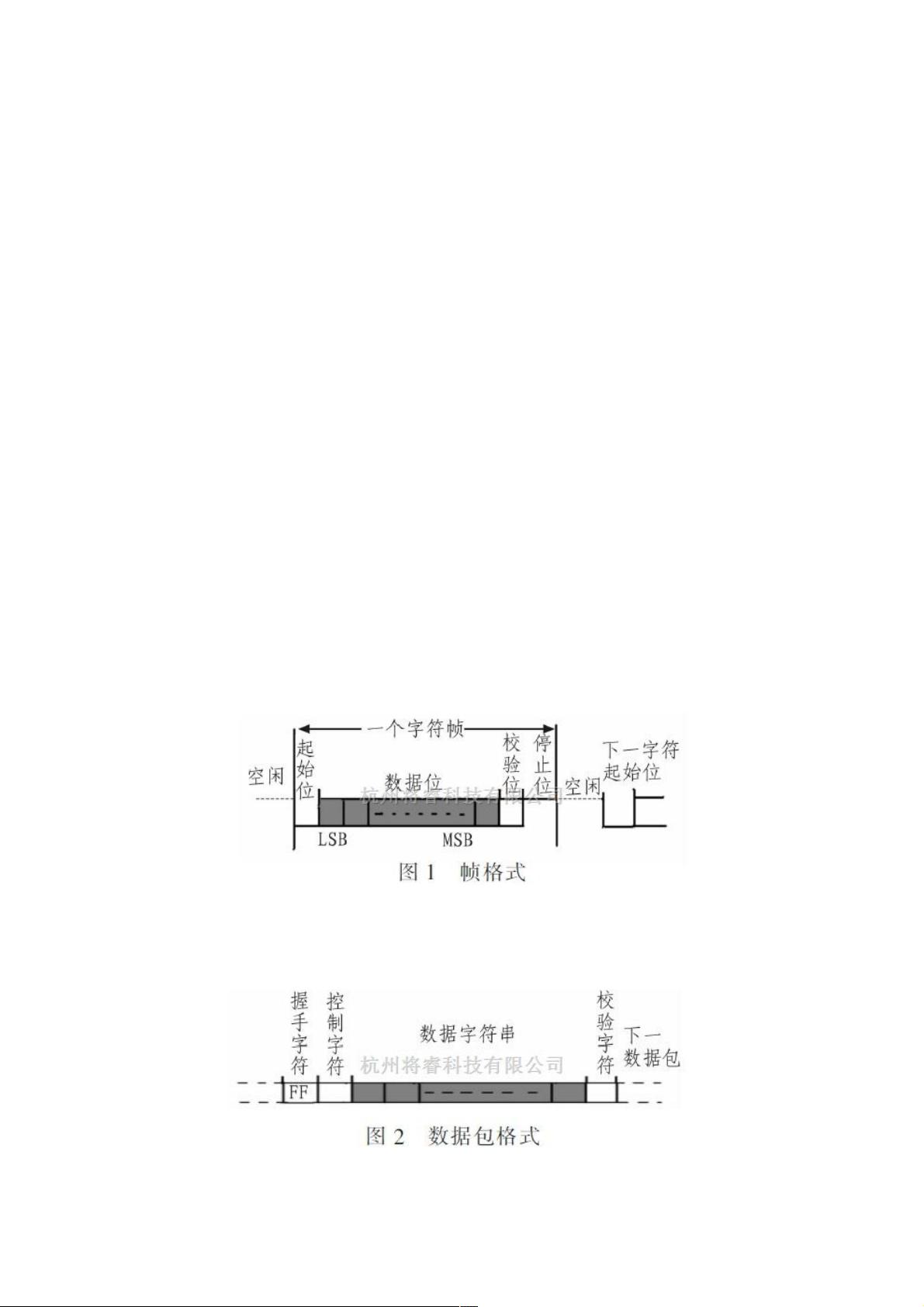

在设计中,首先对RS-232C通信协议进行了深入分析,了解其帧结构和通信规则。为了确保有效通信,作者自定义了数据包传输格式,这通常包括起始位、数据位、奇偶校验位和停止位,以适应特定应用需求。此外,针对UART(通用异步收发传输器)模块的工作状态多样性,采用了有限状态机(FSM)的编程方法,这是一种有效的状态控制和管理手段,能够处理UART在不同状态下的转换逻辑。

为了提高通信的可靠性,文中提到应用16倍频技术来设置波特率。这种方法可以提高信号的传输速率,从而在保持较高数据传输速率(如9600bit/s)的同时降低误码率。这种高速传输能力对于实时性和数据量大的应用场景至关重要。

设计实现过程中,利用了Altera公司的Quartus II软件平台,这是一个强大的EDA工具,支持用Verilog HDL(硬件描述语言)进行逻辑设计和编程。Verilog HDL是一种广泛应用的硬件描述语言,可以方便地描述数字逻辑系统的行为和结构。在Quartus II上完成设计后,通过VC(Visual C++)编写的程序进行数据传输验证,确保了设计的正确性和实用性。

CPLD作为一种可编程逻辑器件,其优势在于它的连续连接结构,使得延迟可预测,这对于电路仿真和性能优化非常有利。CPLD通常包含大量的宏单元,可以灵活配置以满足各种数字逻辑设计需求。在成本和资源利用率的考虑下,当嵌入式系统需要一个定制化的UART功能时,使用CPLD构建模拟UART模块成为一种有效解决方案。

总结而言,这项研究提供了一种利用CPLD实现RS-232串口通信的方法,解决了PC机与嵌入式系统间数据传输的问题。通过自定义数据包格式、FSM编程、16倍频技术以及Verilog HDL的实现,该方案在满足高速、低误码率通信的同时,也展现了CPLD在设计灵活度和成本控制上的优势。这对于工程实践中的嵌入式系统设计具有很高的参考价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-12-10 上传

2020-11-08 上传

2020-12-06 上传

2020-11-06 上传

2020-12-10 上传

2020-12-10 上传

weixin_38699302

- 粉丝: 2

- 资源: 922

最新资源

- html5:第五科技,分享一些自己做的html5源码!

- 双基地模糊度函数:计算双基地雷达的模糊度函数-matlab开发

- 61IC_S2647,c语言-15的源码,c语言

- perfume-master.zip

- github-project-try:我的学生的简单github测试

- 串口接收试验_单片机C语言实例(纯C语言源代码).zip

- dropwizardapp:玩dropwizard

- 50project50days-blank:Project Starter文件

- code,c语言编写系统源码,c语言

- HTML5-CSS3-Cookbook:HTML5和CSS3实例教程-原始

- 液晶12864并行2_单片机C语言实例(纯C语言源代码).zip

- Django3ByExample

- love-running:基于都柏林的跑步社区的网站

- zlib-1.2.2,c语言网卡驱动源码,c语言

- 体育馆

- JavaPractice:Java实践程序