16位单周期CPU设计详解与实现

需积分: 10 95 浏览量

更新于2024-09-16

收藏 1.03MB DOCX 举报

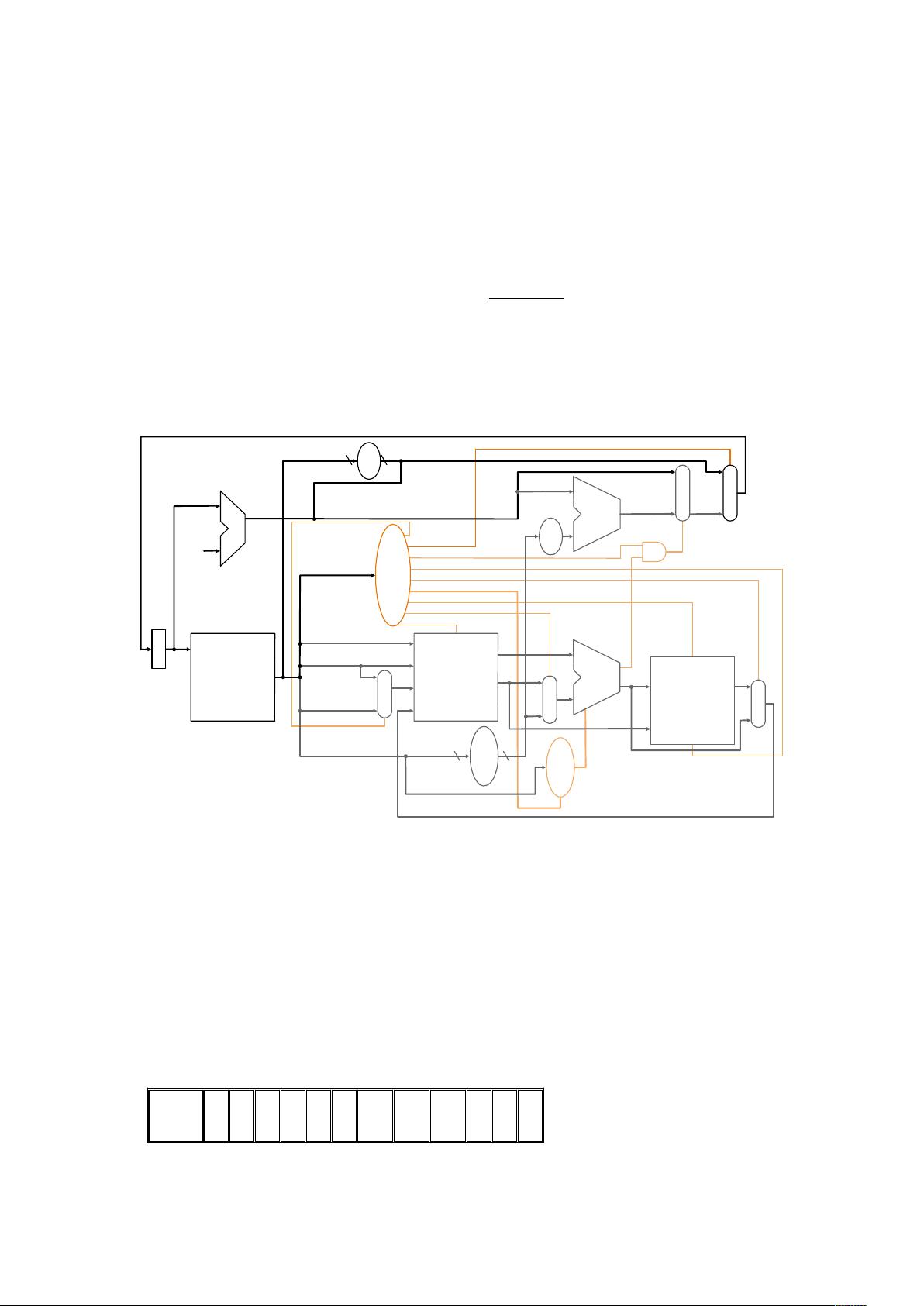

本文档详细介绍了作者自己开发的一个16位单周期CPU项目,旨在通过实践学习和深化对计算机组成原理的理解。CPU的核心部分包括原理图设计、指令编码、ALU控制器和主控制器。

1. 设计目的:

该项目的目标是构建一个16位的单时钟周期处理器,以便更好地理解处理器内部结构,如寄存器、数据和指令存储器的工作原理,以及它们如何处理数据和执行指令。设计者利用Logisim工具来进行这一实验性项目。

2. 设计原理:

- 原理图:

与32位CPU原理图类似,但重点在于16位设计,这意味着内部组件的宽度调整为处理16位数据。

- 指令编码:

指令集采用半字编码,每个指令字长为16位,包括R-type指令,如Jump、Beq(条件转移)、Bne(非等价条件转移)等。这些指令的执行依赖于ALU,如进行或(or)、与(and)、加(add)和减(sub)操作。Jump指令使用12位的伪绝对地址,Beq和Bne指令则涉及带符号的相对偏移量计算。

- ALU控制器:

控制器设计考虑到了指令多样性,通过三位信号量区分R型指令和非R型指令。R型指令的funct字段用于确定特定的ALU操作,而非R型指令的低两位作为控制信号。

- 主控制器:

主控制器负责解析指令并设置必要的操作,例如指定寄存器作为数据源(RegDst)、ALU源(ALUSrc)以及内存操作目标(MentoR)。指令执行前,主控制器会根据指令编码表设置操作码和其他参数。

- 内存管理:

数据和指令存储器采用独立设计,内存以半字为单位编址,不同于MIPS架构中的字节编址。加载内存内容通常通过将hex文件装载到Logisim的RAM和ROM模块中。

3. 工具运用:

利用Logisim库中的现成组件进行硬件设计,并通过文件导入(LoadImage)功能加载预定义的十六进制数据。

这个项目不仅提供了深入理解CPU工作原理的实际平台,还展示了设计者如何将理论知识应用到实际设计中,对于其他希望了解和动手实践CPU设计的学生或开发者来说,是一个有价值的资源。通过阅读和研究这个项目,读者可以学习到关于指令集架构、数据路径、控制逻辑以及硬件编程的宝贵经验。

2022-12-05 上传

点击了解资源详情

2021-05-12 上传

2021-09-10 上传

2022-09-23 上传

2022-09-24 上传

LOVE1215225

- 粉丝: 0

- 资源: 1