Tutorial

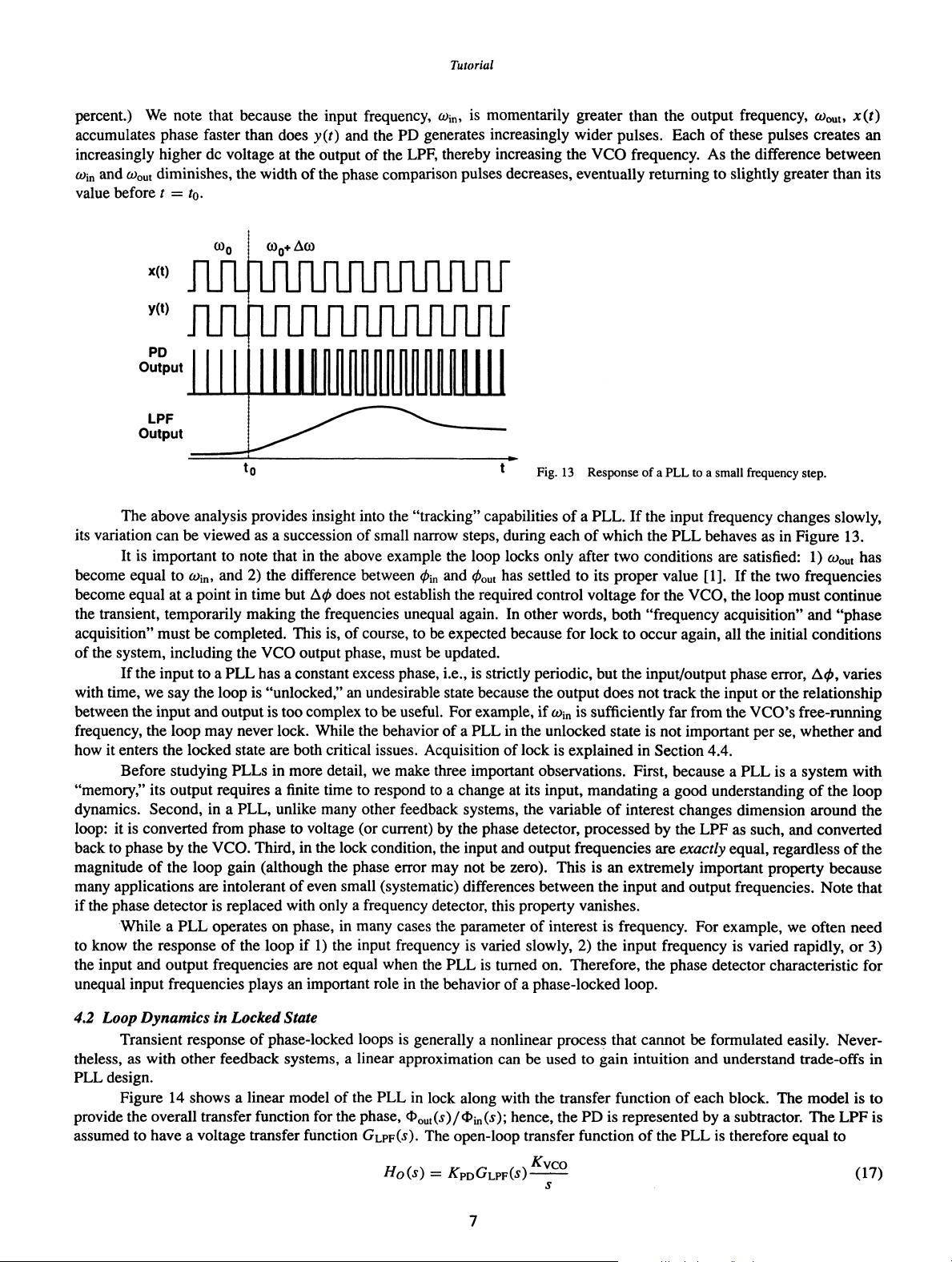

percent.) We note that because the input frequency,

Win,

is momentarily greater than the output frequency,

WoUh

x(t)

accumulates phase faster than does

y(t)

and the PO generates increasingly wider pulses. Each

of

these pulses creates an

increasingly higher de voltage at the output of the LPF, thereby increasing the

veo

frequency. As the difference between

Win and

Wout

diminishes, the width of the phase comparison pulses decreases, eventually returning to slightly greater than its

value before

t = to.

x(t)

y{t)

PO

Output

LPF

Output

Fig. 13 Response of a PLL to a small frequency step.

The above analysis provides insight into the "tracking" capabilities of a PLL. If the input frequency changes slowly,

its variation can be viewed as a succession of small narrow steps, during each of which the PLL behaves as in Figure 13.

It is important to note that in the above example the loop locks only after two conditions are satisfied: 1)

Wout

has

become equal to

Win,

and 2) the difference between (j>in and (j>out has settled to its proper value [1]. If the two frequencies

become equal at a point in time but

~(j>

does not establish the required control voltage for the

YeO,

the loop must continue

the transient, temporarily making the frequencies unequal again. In other words, both "frequency acquisition" and "phase

acquisition" must be completed. This is, of course, to be expected because for lock to occur again, all the initial conditions

of the system, including the

veo

output phase, must be updated.

If the input to a PLL has a constant excess phase, i.e., is strictly periodic, but the input/output phase error,

~l/J,

varies

with time, we say the loop is "unlocked," an undesirable state because the output does not track the input or the relationship

between the input and output is too complex to be useful. For example, if

Win is sufficiently far from the

YeO's

free-running

frequency, the loop may never lock. While the behavior of a PLL in the unlocked state is not important per se, whether and

how it enters the locked state are both critical issues. Acquisition of lock is explained in Section 4.4.

Before studying PLLs in more detail, we make three important observations. First, because a PLL is a system with

"memory," its output requires a finite time to respond to a change at its input, mandating a good understanding

of

the loop

dynamics. Second, in a PLL, unlike many other feedback systems, the variable

of

interest changes dimension around the

loop: it is converted from phase to voltage (or current) by the phase detector, processed by the LPF as such, and converted

back to phase by the

Yeo.

Third, in the lock condition, the input and output frequencies are exactly equal, regardless

of

the

magnitude

of

the loop gain (although the phase error may not be zero). This is an extremely important property because

many applications are intolerant of even small (systematic) differences between the input and output frequencies. Note that

if the phase detector is replaced with only a frequency detector, this property vanishes.

"Whilea

PLL

operates on phase, in many cases the parameter of interest is frequency. For example, we often need

to know the response of the loop if 1) the input frequency is varied slowly, 2) the input frequency is varied rapidly, or 3)

the input and output frequencies are not equal when the PLL is turned on. Therefore, the phase detector characteristic for

unequal input frequencies plays an important role in the behavior of a phase-locked loop.

4.2 Loop Dynamics in LockedState

Transient response of phase-locked loops is generally a nonlinear process that cannot be formulated easily. Never-

theless, as with other feedback systems, a linear approximation can be used to gain intuition and understand trade-offs in

PLL design.

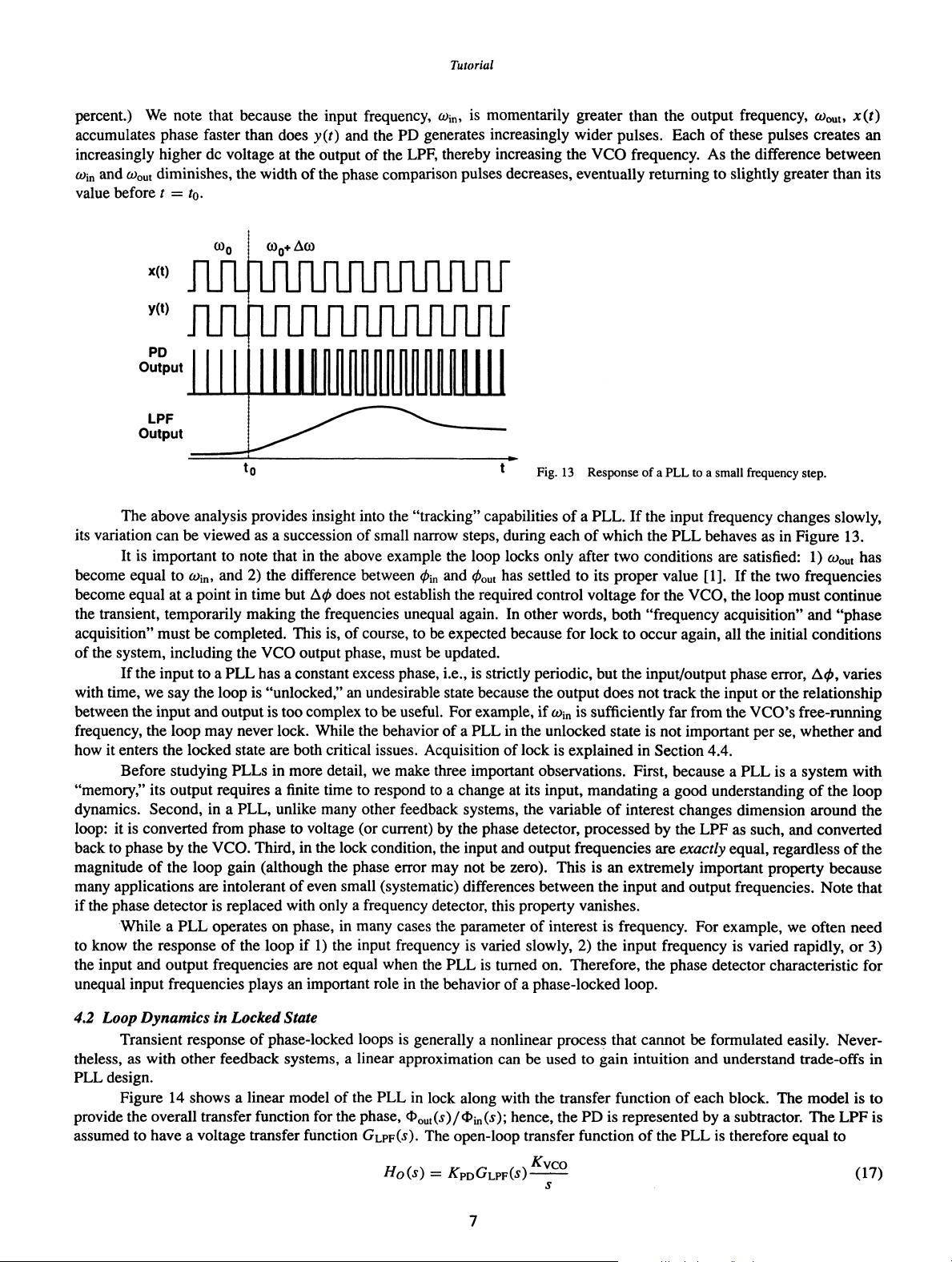

Figure 14 shows a linear model of the PLL in lock along with the transfer function

of

each block. The model is to

provide the overall transfer function for the phase,

<I>

out

(s)

/

<I>

in

(s);

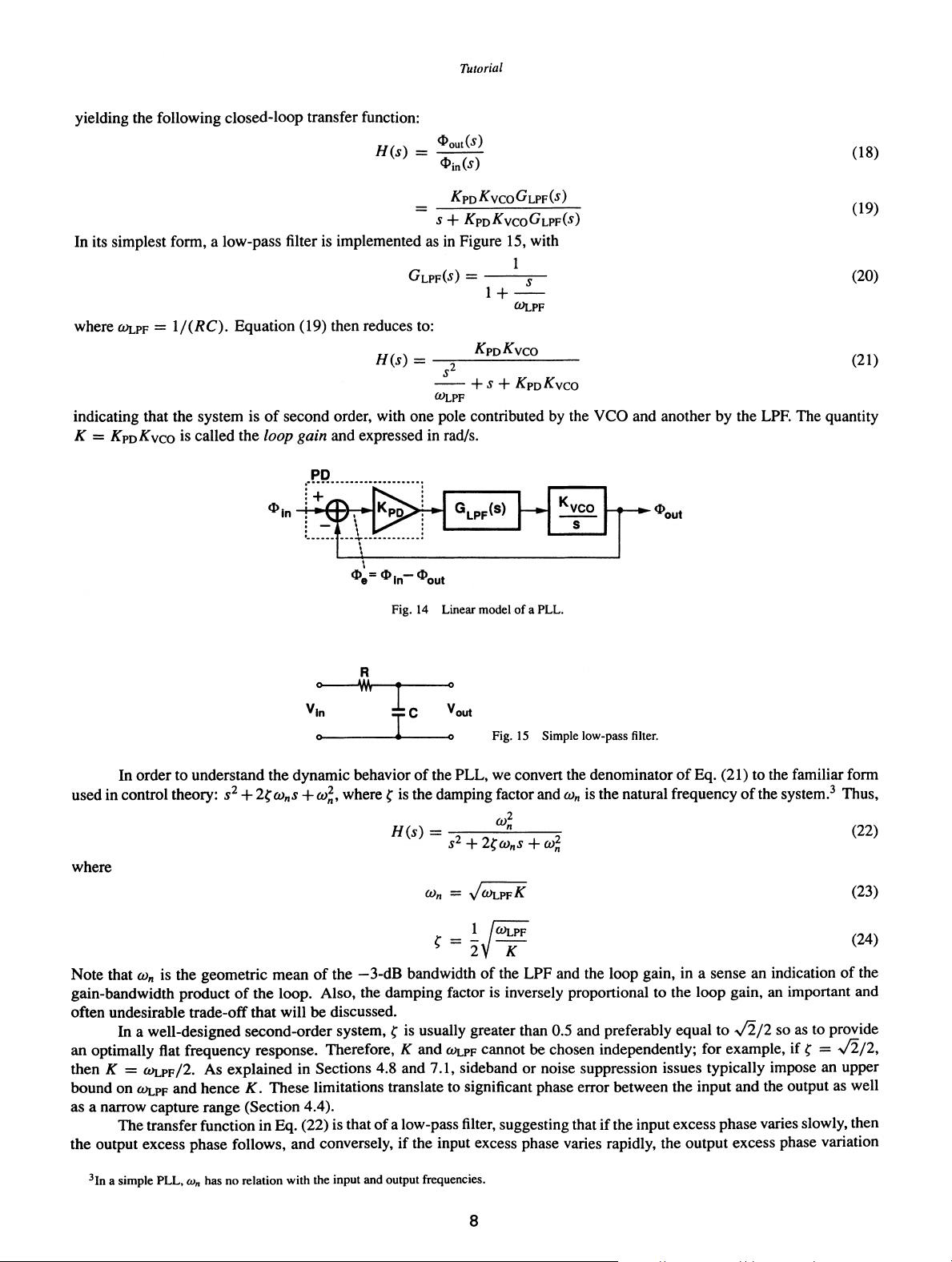

hence, the PD is represented by a subtractor. The LPF is

assumed to have a voltage transfer function

GLPF(S). The open-loop transfer function of the PLL is therefore equal to

Kvco

Ho(s)

=

KpOGLPF(S)--

(17)

S

7

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

信息提交成功

信息提交成功