ModelSim仿真教程:从入门到实践

"modelsim教程"

Modelsim是一款广泛使用的硬件描述语言(HDL)仿真器,支持Verilog和VHDL等语言,适用于数字系统的验证。本教程将指导您如何使用ModelSim进行基本操作,包括下载安装、创建项目、编译代码以及进行仿真。

### 准备事项

1. **ModelSim试用版下载**:

在开始使用Modelsim之前,您需要从官方网站或授权渠道下载适合您操作系统的试用版。不同版本如ModelSim PE(Professional Edition)、LE(Learning Edition)和SE(Standard Edition)在功能和许可上有差异。PE版提供最全面的功能,而LE和SE版则针对教育和学习场景,可能在某些高级特性上有所限制。

2. **范例程序**:

可以选择斯坦福大学Viterbi解码器项目作为实践案例,该项目包含多个Verilog程序。或者,您可以使用其他简单的Verilog(如add4.v和add4test.v)或VHDL(如adder.vhd和testadder.vhd)示例开始。

### 快速上手

#### 1. 建立新的Project

1-1 **启动ModelSim**:

首次使用时,可以通过“开始”菜单中的“程序集”找到ModelSimSE目录下的ModelSim应用程序,或直接点击桌面快捷方式启动。

1-2 **创建Project**:

- 选择`File` -> `New` -> `Project`。

- 输入项目名称和位置,并点击`OK`。系统会在指定路径下创建一个名为“work”的默认子目录,同时生成Viterbi相关的配置文件(如Viterbi.cr.mti和Viterbi.mpf)。

- 在工作区的“Project”标签下,您会看到新创建的项目,初始为空。

#### 2. 引进HDL Files

- 将范例程序(Verilog或VHDL源文件)导入到项目中。这通常通过拖放文件至工作区或使用`File` -> `Add/Remove Sources`完成。

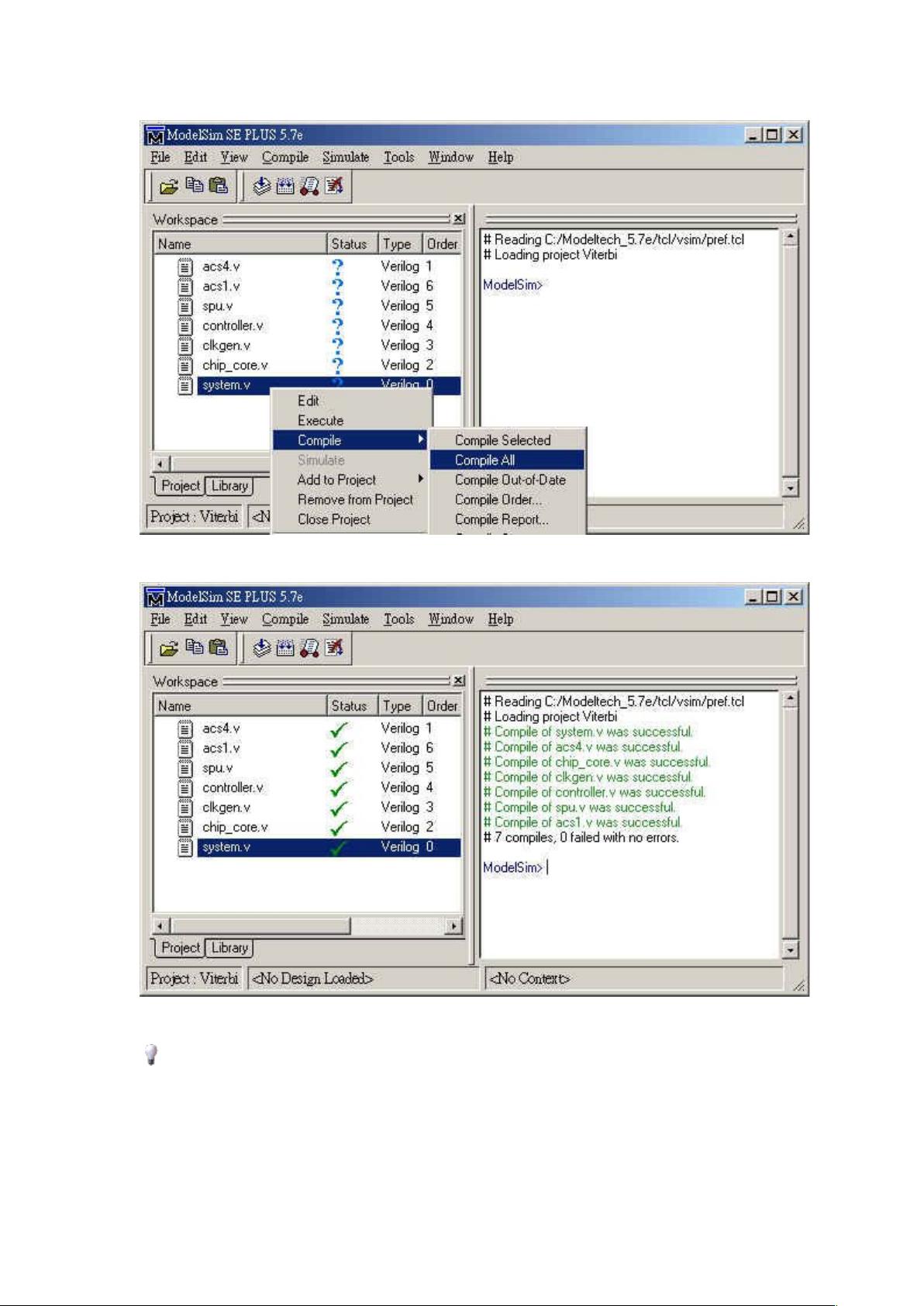

#### 3. Compile

- 对项目中的所有源文件进行编译。这可以通过右键单击文件并选择`Compile`,或使用菜单栏的`Compile` -> `Compile Current File`来实现。编译过程会检查语法错误和设计问题。

#### 4. 模拟 (Simulate/Loading and Run)

- 创建一个新的仿真会话:选择`Simulate` -> `Start New Simulation`。

- 加载编译好的设计:选择`Load` -> `Design Units`,然后选择你的top-level模块。

- 设置仿真时间范围:在命令行输入`run <time>`,其中`<time>`是你希望模拟的时间单位(如`10ns`)。

- 观察结果:在波形窗口(Waveform Viewer)中,你可以添加信号进行观察,通过运行仿真查看信号变化。

### 进阶使用

除了基础操作,ModelSim还提供了丰富的调试工具,如设置断点、单步执行、查看变量值等。对于更复杂的项目,可以使用工程管理器(Project Manager)组织和管理源文件,以及使用脚本语言(如Tcl)自动化仿真流程。

在理解了这些基本步骤之后,您就可以进一步探索ModelSim的高级功能,进行更深入的系统验证和调试。无论是学习数字电路设计还是进行专业的工作,掌握ModelSim的使用都将极大地提升您的工作效率。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2009-06-13 上传

2011-12-07 上传

2009-05-13 上传

点击了解资源详情

点击了解资源详情

wangbang01

- 粉丝: 0

- 资源: 1

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍