忆阻器交叉阵列实现卷积神经网络电路优化设计

需积分: 50 37 浏览量

更新于2024-08-06

8

收藏 10.43MB PDF 举报

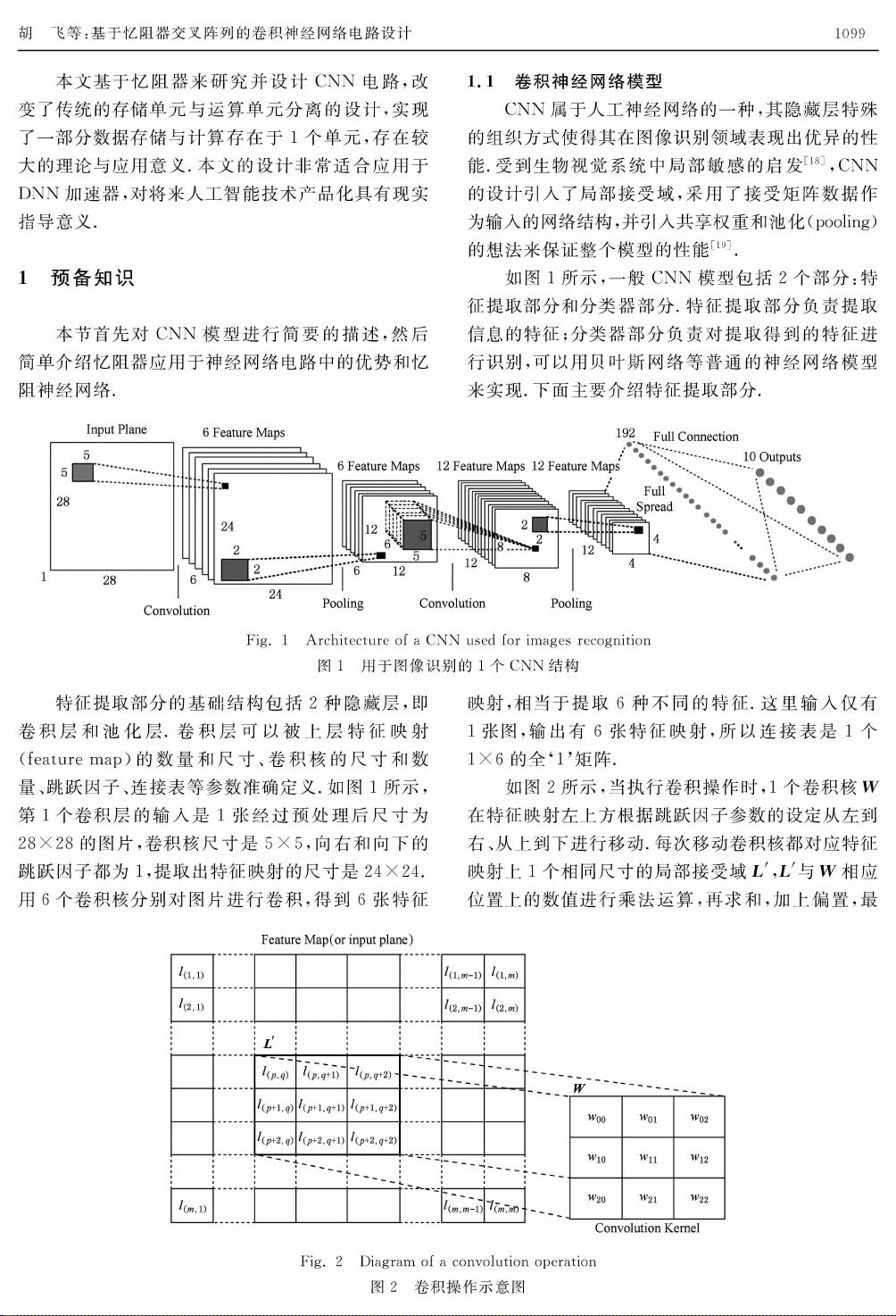

"忆阻器交叉阵列在神经形态计算中的应用越来越受到关注,本文提出了一种改进的忆阻器交叉阵列电路设计,用于实现卷积神经网络(CNN)的功能。该电路能够准确存储权重和偏置,并执行点积运算,适应于CNN的卷积层、池化层和分类器。设计的忆阻卷积神经网络结构在减少模数-数模转换次数的同时,提高了运算性能。实验结果显示,该芯片在0.8525cm²的面积上,运算速度比计算机快1770倍,性能较之前的设计提升了7.7倍,且识别误差增加微小,具有良好的容错性。"

基于忆阻器交叉阵列的卷积神经网络电路设计是一项创新技术,其核心在于利用忆阻器的特性来模拟神经网络的计算过程。忆阻器,全称为记忆电阻器,是一种非易失性存储元件,能够根据通过它的电流历史改变自身的电阻状态,这种特性使其成为实现神经网络硬件加速的理想选择。

在传统的忆阻器交叉阵列中,忆阻器被排列成矩阵形式,其中每一行和每一列的交叉点对应一个存储单元,可以用来存储神经网络的权重。本文提出的改进设计提高了存储精度,确保了权重和偏置的精确表示。这种改进的忆阻器交叉阵列可以执行点积操作,这是神经网络中关键的乘加运算,尤其在卷积神经网络的卷积层中。

卷积神经网络(CNN)是深度学习的重要组成部分,常用于图像识别和处理任务。在本文设计的忆阻器CNN结构中,卷积操作的结果以模拟形式直接存储,跳过了通常的模数-数模转换步骤,从而减少了计算延迟和能量消耗。这一设计充分利用了CNN的高容错性,即使存在轻微的硬件误差,也能保持较高的识别准确性。

实验结果证明了该忆阻器CNN电路的高效性和实用性。在与计算机比较时,其运算速度提高了1770倍,而在相似的芯片面积下,性能提升约7.7倍。此外,尽管存在微小的识别误差开销,但与软件运行结果相比,当每个忆阻器存储6位或8位信息时,平均识别误差仅增加了0.039%和0.012%,这显示了设计的健壮性。

忆阻器交叉阵列在卷积神经网络电路设计中的应用展示了巨大的潜力,不仅提高了计算效率,而且降低了功耗,为实现高性能、低能耗的神经网络硬件平台提供了新的思路。随着忆阻器技术的进一步发展,这种电路设计有望在未来的嵌入式和边缘计算系统中发挥重要作用。

2022-12-01 上传

2015-10-13 上传

2021-09-26 上传

2021-09-25 上传

2021-09-26 上传

2021-02-25 上传

2021-09-26 上传

weixin_38537541

- 粉丝: 6

- 资源: 892

最新资源

- NIST REFPROP问题反馈与解决方案存储库

- 掌握LeetCode习题的系统开源答案

- ctop:实现汉字按首字母拼音分类排序的PHP工具

- 微信小程序课程学习——投资融资类产品说明

- Matlab犯罪模拟器开发:探索《当蛮力失败》犯罪惩罚模型

- Java网上招聘系统实战项目源码及部署教程

- OneSky APIPHP5库:PHP5.1及以上版本的API集成

- 实时监控MySQL导入进度的bash脚本技巧

- 使用MATLAB开发交流电压脉冲生成控制系统

- ESP32安全OTA更新:原生API与WebSocket加密传输

- Sonic-Sharp: 基于《刺猬索尼克》的开源C#游戏引擎

- Java文章发布系统源码及部署教程

- CQUPT Python课程代码资源完整分享

- 易语言实现获取目录尺寸的Scripting.FileSystemObject对象方法

- Excel宾果卡生成器:自定义和打印多张卡片

- 使用HALCON实现图像二维码自动读取与解码