Camera Link接口异步FIFO设计:解决亚稳态与控制信号

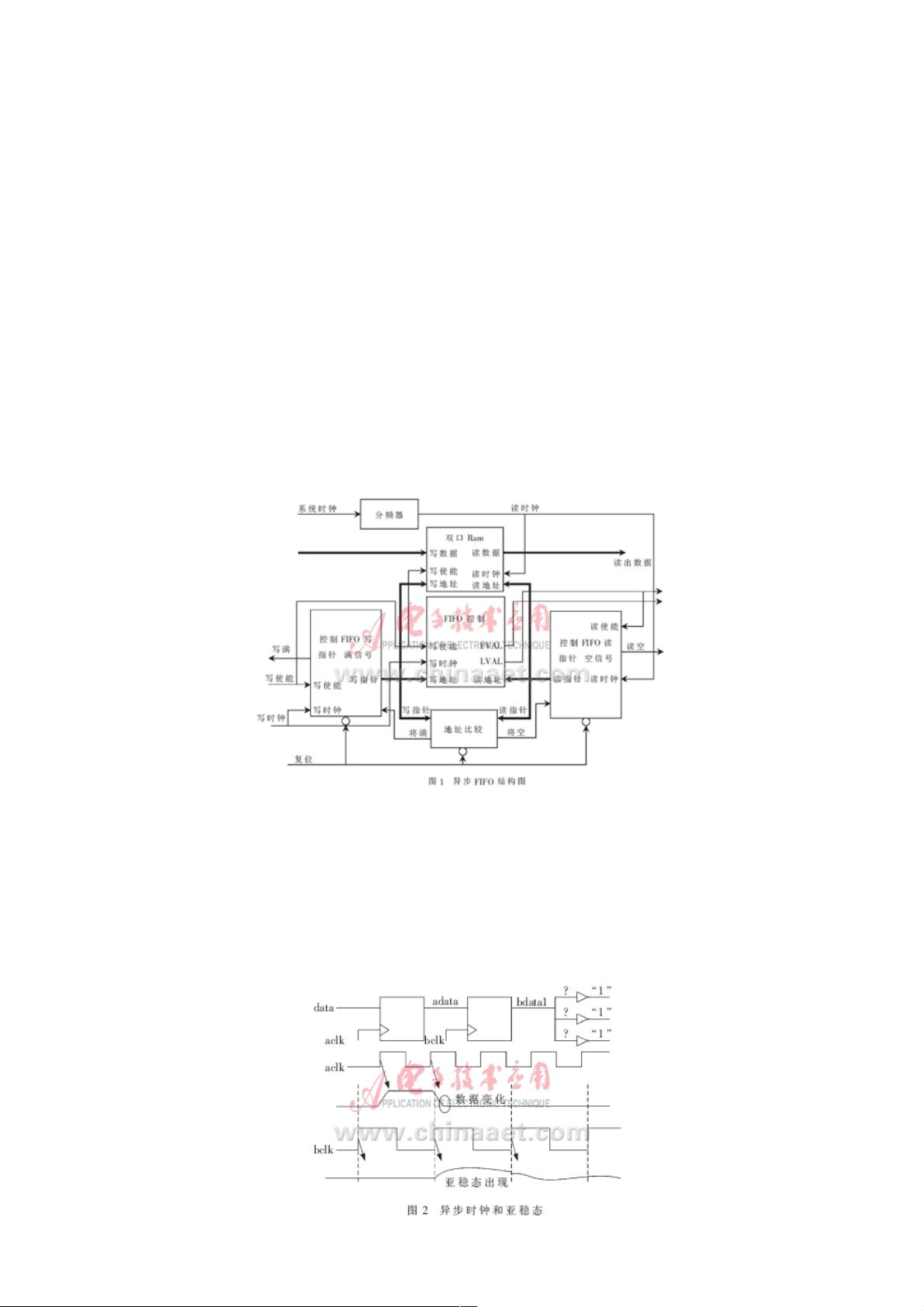

"本文主要探讨了在Camera Link接口中异步FIFO的设计与实现,针对Camera Link接口的帧有效信号FVAL和行有效信号LVAL,设计了一个能够处理这些控制信号的异步FIFO,旨在解决FPGA设计中的亚稳态问题以及生成控制信号的挑战。" 在计算机硬件和图像处理领域,Camera Link接口是一种广泛使用的高速数字图像传输标准,它允许高效地传输高分辨率的视频数据。在这个接口中,异步FIFO扮演着至关重要的角色,因为它能够处理不同时钟域之间的数据流,从而确保数据传输的稳定性和同步性。 异步FIFO的设计主要面临两个关键问题。首先,由于FPGA内部存在不同的时钟域,可能会导致亚稳态现象,这会影响数据的正确传输。亚稳态是指在信号转换过程中,由于时钟边沿检测不准确,可能导致短暂的不确定状态。为了降低亚稳态出现的概率,设计者需要采用适当的同步技术,如两级寄存器或D Flip-Flops,来稳定信号,确保数据在传递过程中的完整性。 其次,异步FIFO需要能够生成有效的控制信号,如空(nempty_n)和满(nfull_n)标志,这些信号用于指示FIFO的状态,以便于正确地管理读写操作。在Camera Link接口中,FIFO不仅要缓冲数据,还需要根据FVAL和LVAL信号来同步控制图像数据的时序。这就需要在设计中包含额外的逻辑来监测和生成这些同步控制信号。 文中提到的异步FIFO设计采用了Verilog HDL语言,这是一种广泛使用的硬件描述语言,用于描述数字系统的逻辑功能。设计中,FIFO被划分为四个主要部分:主控模块、读地址及空标志产生模块、写地址及满标志产生模块和异步比较模块。每个模块都有其特定的功能,协同工作以实现异步数据传输和控制信号的生成。 主控模块是FIFO的核心,负责管理双口RAM的读写操作。读地址及空标志产生模块根据读时钟信号和行同步信号LVAL生成读地址和空标志,确保在正确的时间读取数据。写地址及满标志产生模块则在写时钟域内工作,响应写使能信号,更新写地址并检测FIFO是否即将填满。异步比较模块则比较读写地址,以生成将满和将空的信号,帮助系统实时监控FIFO的状态。 尽管有现成的FIFO解决方案,但它们往往不能直接适应Camera Link接口的特殊需求,因此需要定制化设计。这个设计展示了如何通过理解接口标准和FPGA的工作原理,来克服设计挑战,实现一个既能满足接口要求,又能提供稳定视频数据和控制信号的异步FIFO。 异步FIFO在Camera Link接口中的设计和实现是一项复杂但必要的任务,它需要对FPGA设计、同步技术、时钟域管理和视频信号处理有深入的理解。通过这样的设计,可以极大地提高图像数据传输的效率和可靠性,这对于高精度的图像处理和分析应用至关重要。

下载后可阅读完整内容,剩余3页未读,立即下载

- 粉丝: 5

- 资源: 943

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- Unity UGUI性能优化实战:UGUI_BatchDemo示例

- Java实现小游戏飞翔的小鸟教程分享

- Ant Design 4.16.8:企业级React组件库的最新更新

- Windows下MongoDB的安装教程与步骤

- 婚庆公司响应式网站模板源码下载

- 高端旅行推荐:官网模板及移动响应式网页设计

- Java基础教程:类与接口的实现与应用

- 高级版照片排版软件功能介绍与操作指南

- 精品黑色插画设计师作品展示网页模板

- 蓝色互联网科技企业Bootstrap网站模板下载

- MQTTFX 1.7.1版:Windows平台最强Mqtt客户端体验

- 黑色摄影主题响应式网站模板设计案例

- 扁平化风格商业旅游网站模板设计

- 绿色留学H5模板:科研教育机构官网解决方案

- Linux环境下EMQX安装全流程指导

- 可爱卡通儿童APP官网模板_复古绿色动画设计

信息提交成功

信息提交成功