Verilog设计:第六讲 - FSM有限状态机解析

版权申诉

"电子电路设计训练 - 数字部分(Verilog):第六讲 FSM有限状态机,主要讨论了如何利用Verilog设计有限状态机(FSM),以实现精确的数据流动控制和逻辑系统的有序操作。"

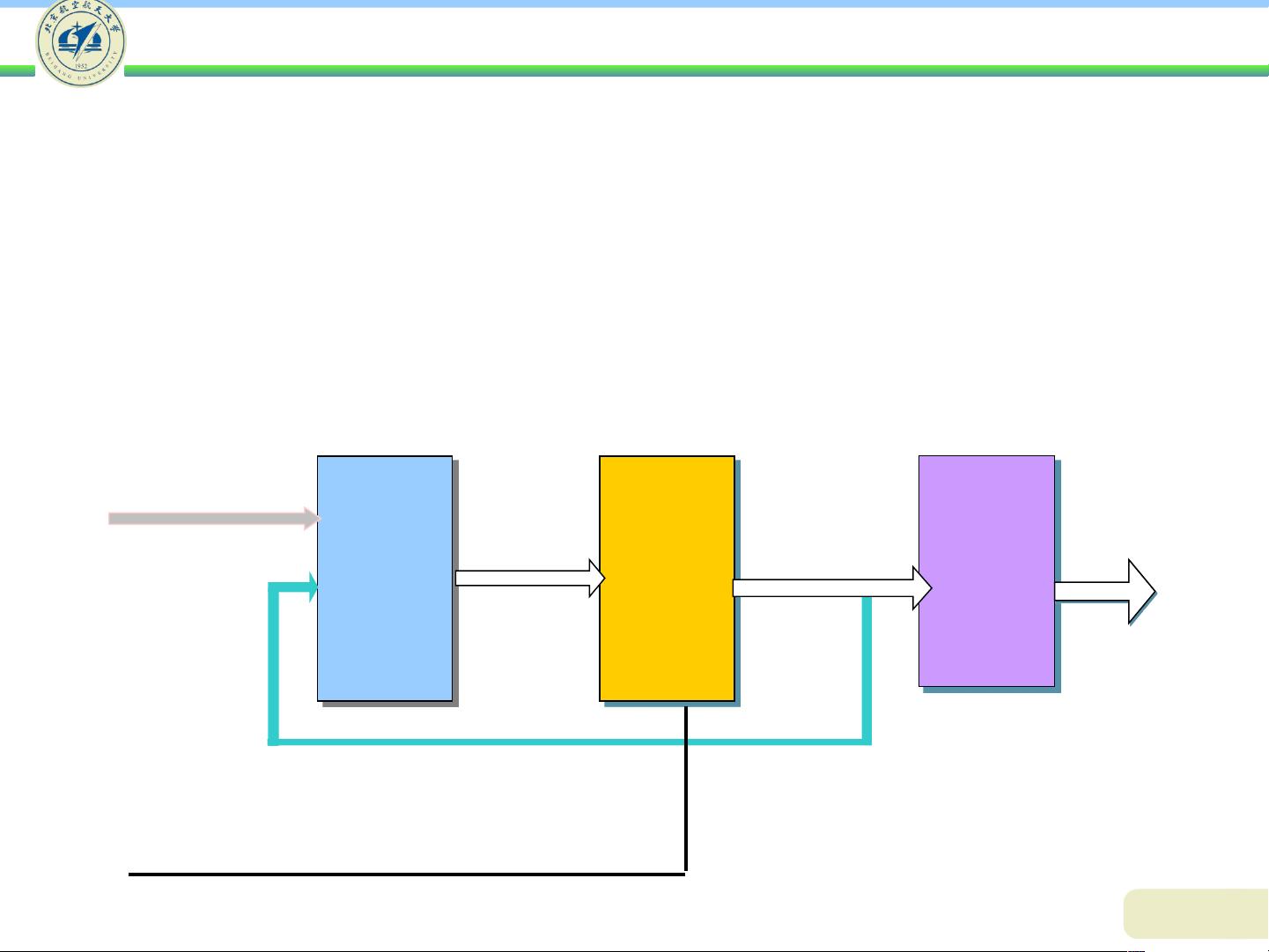

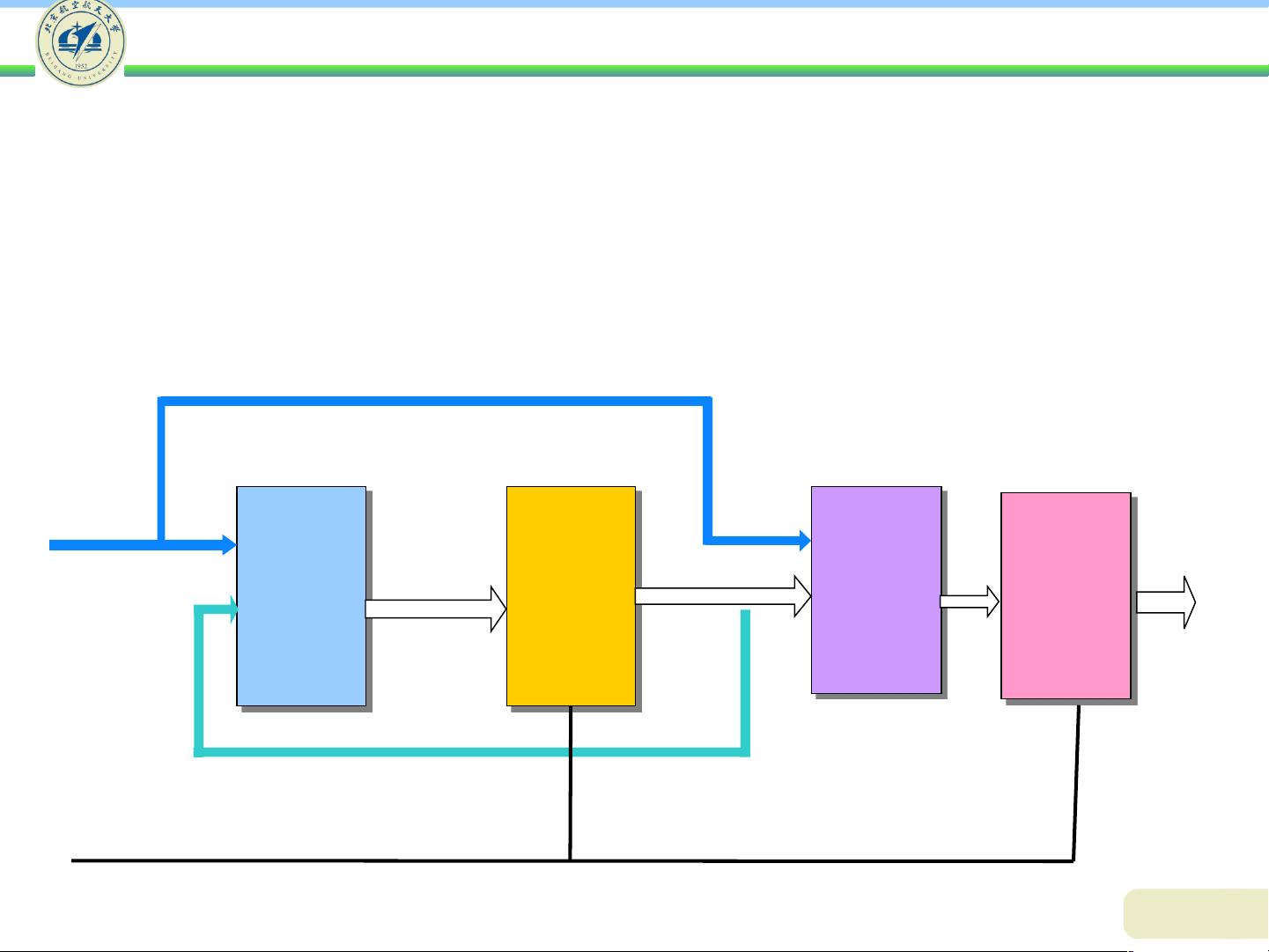

在电子电路设计中,有限状态机(Finite State Machine, FSM)是一种重要的时序逻辑电路,常用于控制序列的生成和复杂逻辑操作的管理。第六讲重点讲解了FSM的基本概念和设计方法,以解决如何在数字系统中准确地控制数据在寄存器和逻辑电路之间的流动。

首先,FSM的关键在于数据流动控制,这通常依赖于时钟信号。时钟是系统中的同步信号,确保所有操作在同一时钟周期内同步进行,从而避免数据冒险和竞争现象,有效解决时延问题。例如,要将寄存器C的值准确无误地存入寄存器A,就需要精确控制数据在时钟边缘的传输。

设计一个有效的FSM,需要以下要素:

1. 能够记忆当前状态的存储元件,通常是寄存器。

2. 状态变化仅在时钟脉冲的上升沿或下降沿发生,保证了状态转换的确定性。

3. 当满足特定输入条件时,FSM在时钟边沿触发状态转移,同时更新存储元件以记录新状态;若条件不满足,状态保持不变。

4. 不同状态对应不同的操作,通过状态决定开关逻辑阵列的行为。

FSM的设计通常采用状态转移图表示,这是一种图形化工具,用于描绘状态间的转移逻辑。在Verilog中,可以编写RTL级( Register Transfer Level)的代码来实现FSM,这样的代码不仅直观,而且可综合,可以直接转化为硬件描述语言。

掌握FSM设计方法对于理解数字系统的工作原理至关重要。通过结合基本电路知识和对数据处理流程的深入理解,设计师可以避免由逻辑延迟引起的“竞争冒险”问题,构建出高效、可靠的复杂数字逻辑系统。Verilog作为一种强大的硬件描述语言,提供了灵活的工具来创建和实现各种复杂的FSM设计。在数字电路设计中,FSM的应用广泛,包括控制器、协议解析器、计数器等多个领域,是理解和设计现代数字系统的基础之一。

2021-09-21 上传

2021-10-07 上传

2022-06-17 上传

点击了解资源详情

2022-06-17 上传

2021-10-07 上传

2021-10-03 上传

2021-10-11 上传

2022-06-16 上传

智慧安全方案

- 粉丝: 3820

- 资源: 59万+

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率