OMAP3 530/25 Applications Processor

SPRS507D – FEBRUARY 2008 – REVISED MAY 2009

www.ti.com

pulldown resistors can be enabled or disabled via software.

Note: The pullup/pulldown drive strength is equal to 100 µ A except for CBB balls P27, P26, R27, and

R25 and CUS balls N22, N21, N20, and P24, which the pulldown drive strength is equal to 1.8 k Ω .

13. IO CELL: IO cell information.

Note: Configuring two pins to the same input signal is not supported as it can yield unexpected results.

This can be easily prevented with the proper software configuration.

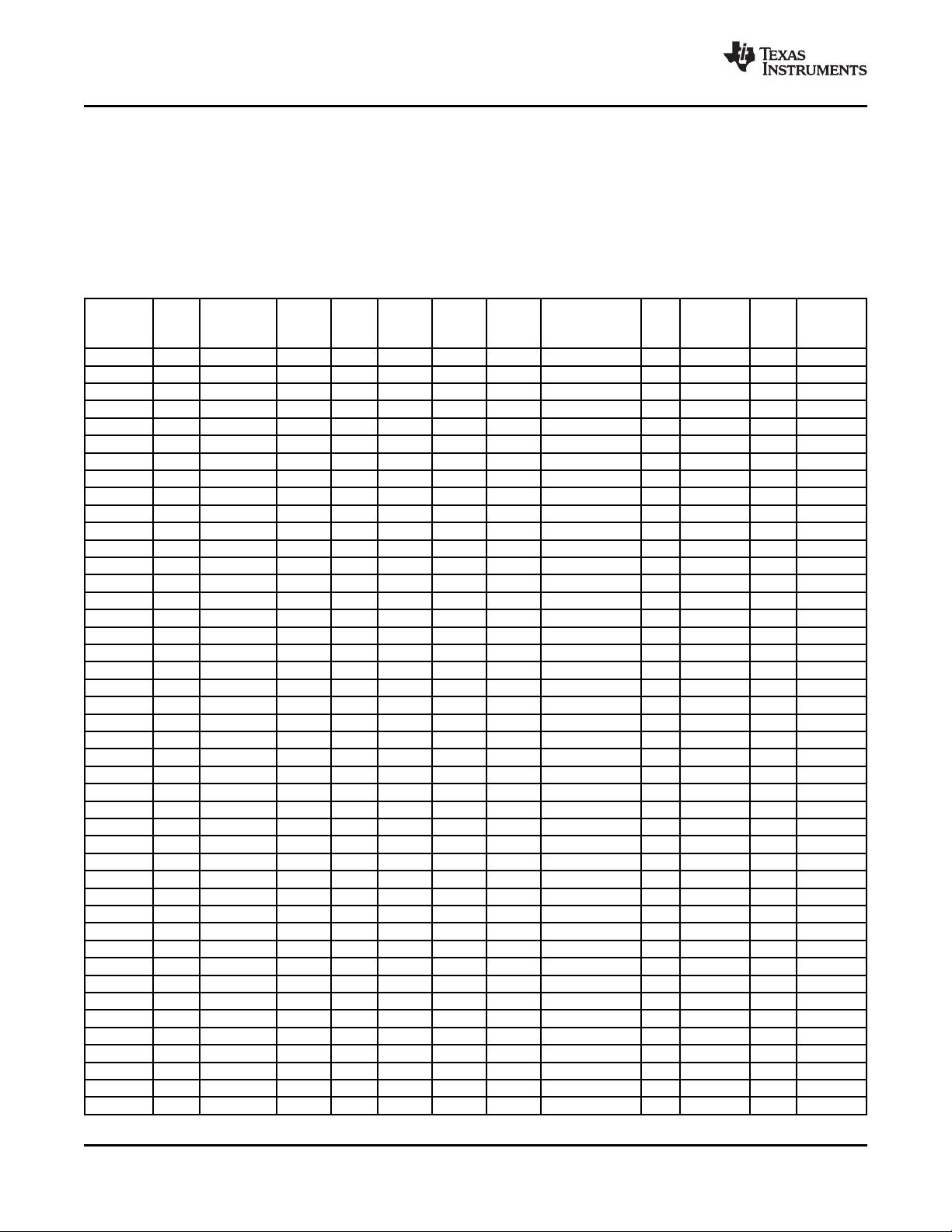

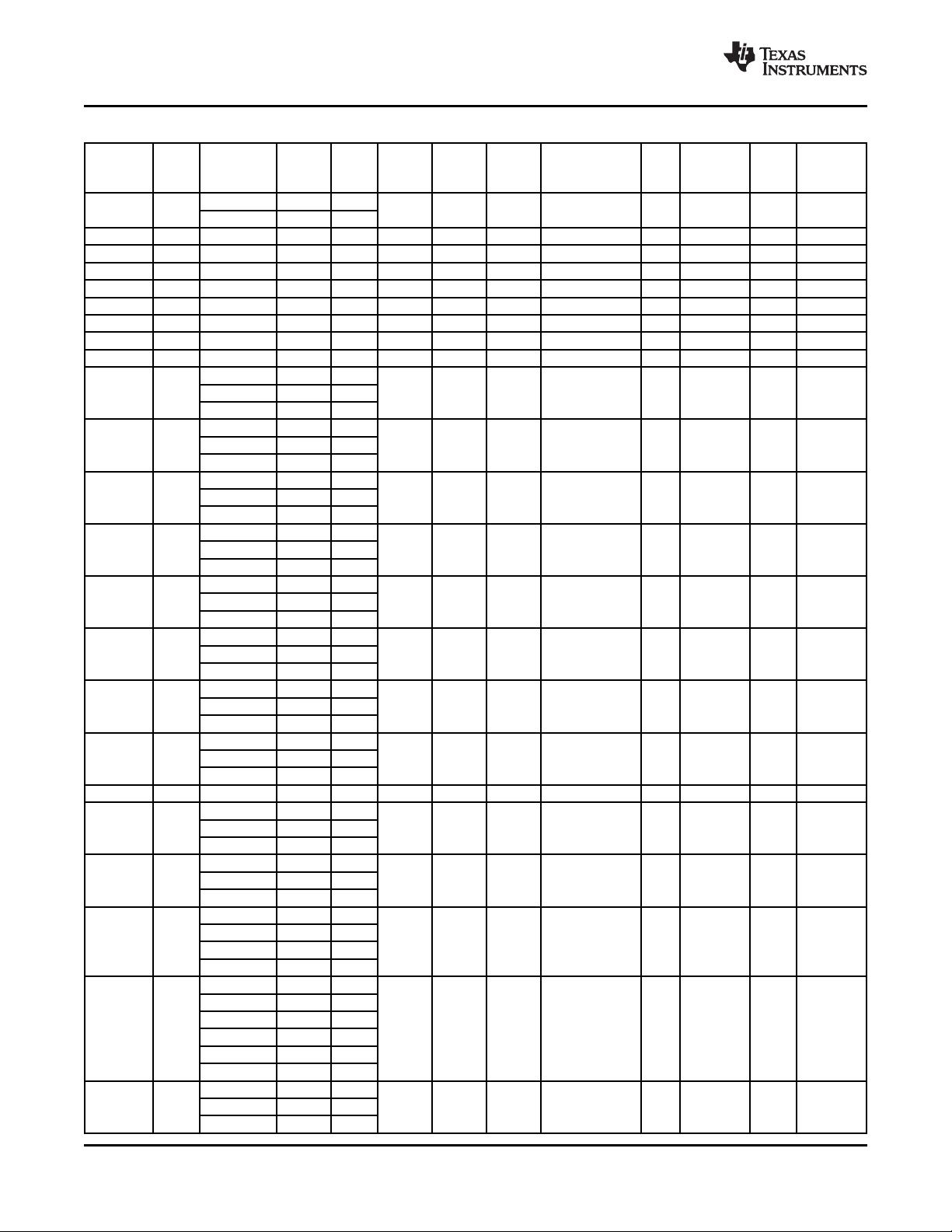

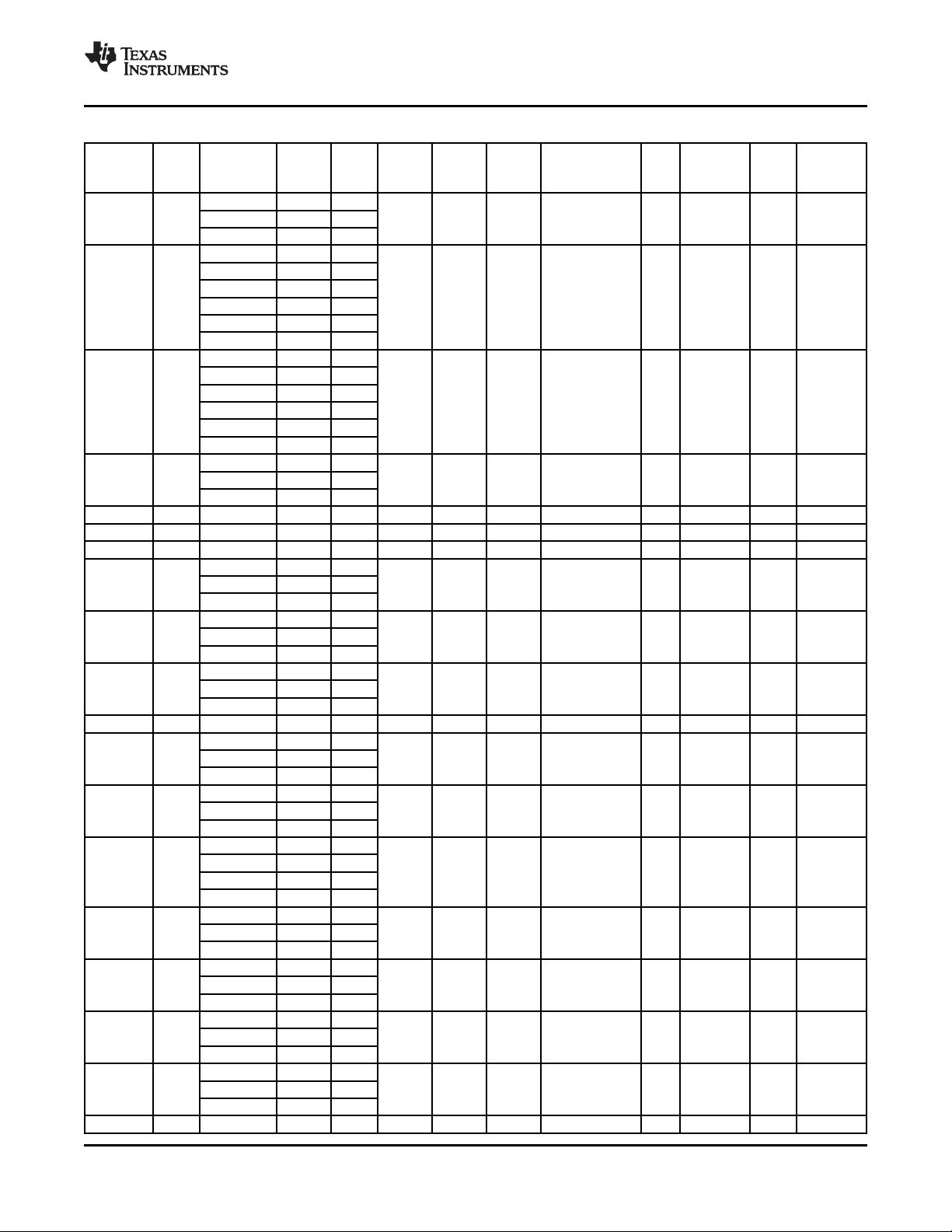

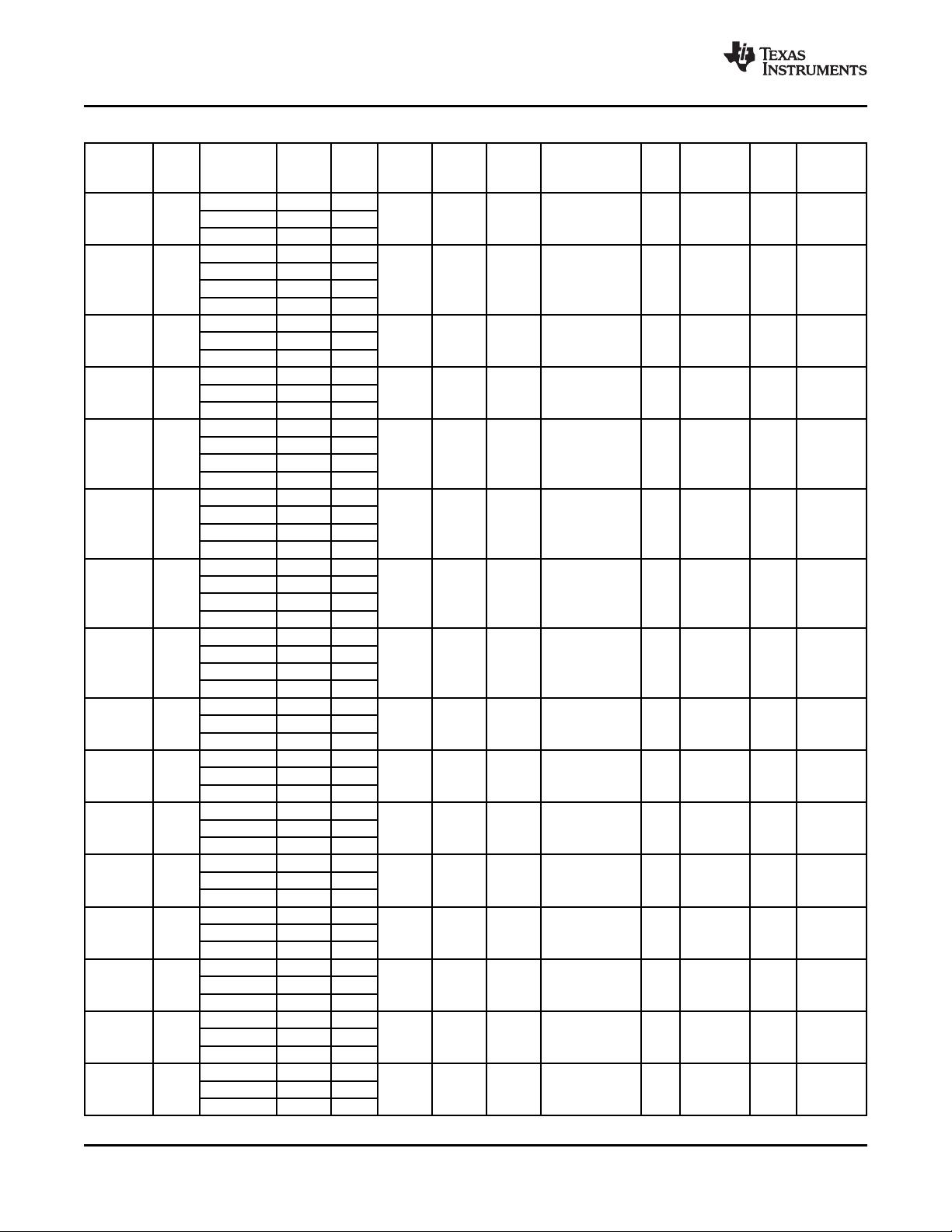

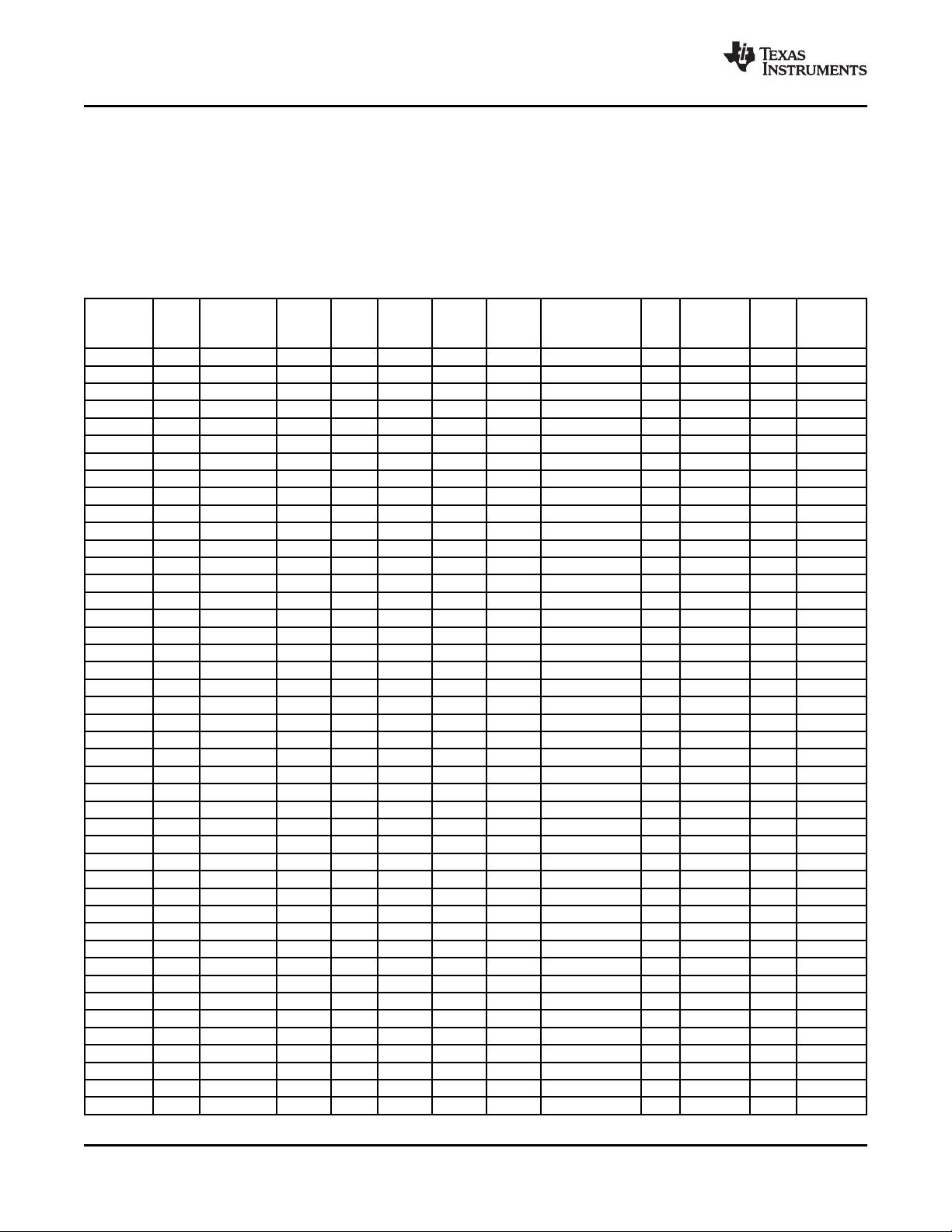

Table 2-1. Ball Characteristics (CBB Pkg.)

(1)

BALL BALL PIN MODE [4] TYPE [5] BALL BALL RESET POWER [9] HYS BUFFER PULL IO

BOTTOM [1] TOP [2] NAME [3] RESET RESET REL. [10] STRENGTH U/D CELL [13]

STATE [6] REL. MODE [8] (mA) [11] TYPE

STATE [7] [12]

D6 J2 sdrc_d0 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

C6 J1 sdrc_d1 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

B6 G2 sdrc_d2 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

C8 G1 sdrc_d3 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

C9 F2 sdrc_d4 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

A7 F1 sdrc_d5 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

B9 D2 sdrc_d6 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

A9 D1 sdrc_d7 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

C14 B13 sdrc_d8 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

B14 A13 sdrc_d9 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

C15 B14 sdrc_d10 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

B16 A14 sdrc_d11 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

D17 B16 sdrc_d12 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

C17 A16 sdrc_d13 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

B17 B19 sdrc_d14 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

D18 A19 sdrc_d15 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

D11 B3 sdrc_d16 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

B10 A3 sdrc_d17 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

C11 B5 sdrc_d18 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

D12 A5 sdrc_d19 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

C12 B8 sdrc_d20 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

A11 A8 sdrc_d21 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

B13 B9 sdrc_d22 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

D14 A9 sdrc_d23 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

C18 B21 sdrc_d24 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

A19 A21 sdrc_d25 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

B19 D22 sdrc_d26 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

B20 D23 sdrc_d27 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

D20 E22 sdrc_d28 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

A21 E23 sdrc_d29 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

B21 G22 sdrc_d30 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

C21 G23 sdrc_d31 0 IO L Z 0 VDDS_ MEM Yes 4 PU/ PD LVCMOS

H9 AB21 sdrc_ba0 0 O 0 0 0 VDDS_ MEM No 4 NA LVCMOS

H10 AC21 sdrc_ba1 0 O 0 0 0 VDDS_ MEM No 4 NA LVCMOS

A4 N22 sdrc_a0 0 O 0 0 0 VDDS_ MEM No 4 NA LVCMOS

B4 N23 sdrc_a1 0 O 0 0 0 VDDS_ MEM No 4 NA LVCMOS

B3 P22 sdrc_a2 0 O 0 0 0 VDDS_ MEM No 4 NA LVCMOS

C5 P23 sdrc_a3 0 O 0 0 0 VDDS_ MEM No 4 NA LVCMOS

C4 R22 sdrc_a4 0 O 0 0 0 VDDS_ MEM No 4 NA LVCMOS

D5 R23 sdrc_a5 0 O 0 0 0 VDDS_ MEM No 4 NA LVCMOS

C3 T22 sdrc_a6 0 O 0 0 0 VDDS_ MEM No 4 NA LVCMOS

C2 T23 sdrc_a7 0 O 0 0 0 VDDS_ MEM No 4 NA LVCMOS

C1 U22 sdrc_a8 0 O 0 0 0 VDDS_ MEM No 4 NA LVCMOS

D4 U23 sdrc_a9 0 O 0 0 0 VDDS_ MEM No 4 NA LVCMOS

(1) NA in this table stands for Not Applicable.

TERMINAL DESCRIPTION16 Submit Documentation Feedback