FPGA入门实验:VGA驱动详解

需积分: 10 160 浏览量

更新于2024-07-31

收藏 1.92MB PDF 举报

"FPGA设计资料、例程"

在FPGA设计领域,QUARTUS 9设计软件和CYCLE2 208芯片是常见的工具和硬件平台。FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种集成电路,允许用户根据需求自定义逻辑电路。QUARTUS 9是Altera公司(现Intel FPGA)开发的一款强大的FPGA设计软件,用于实现逻辑设计、仿真、综合、适配和编程等步骤。

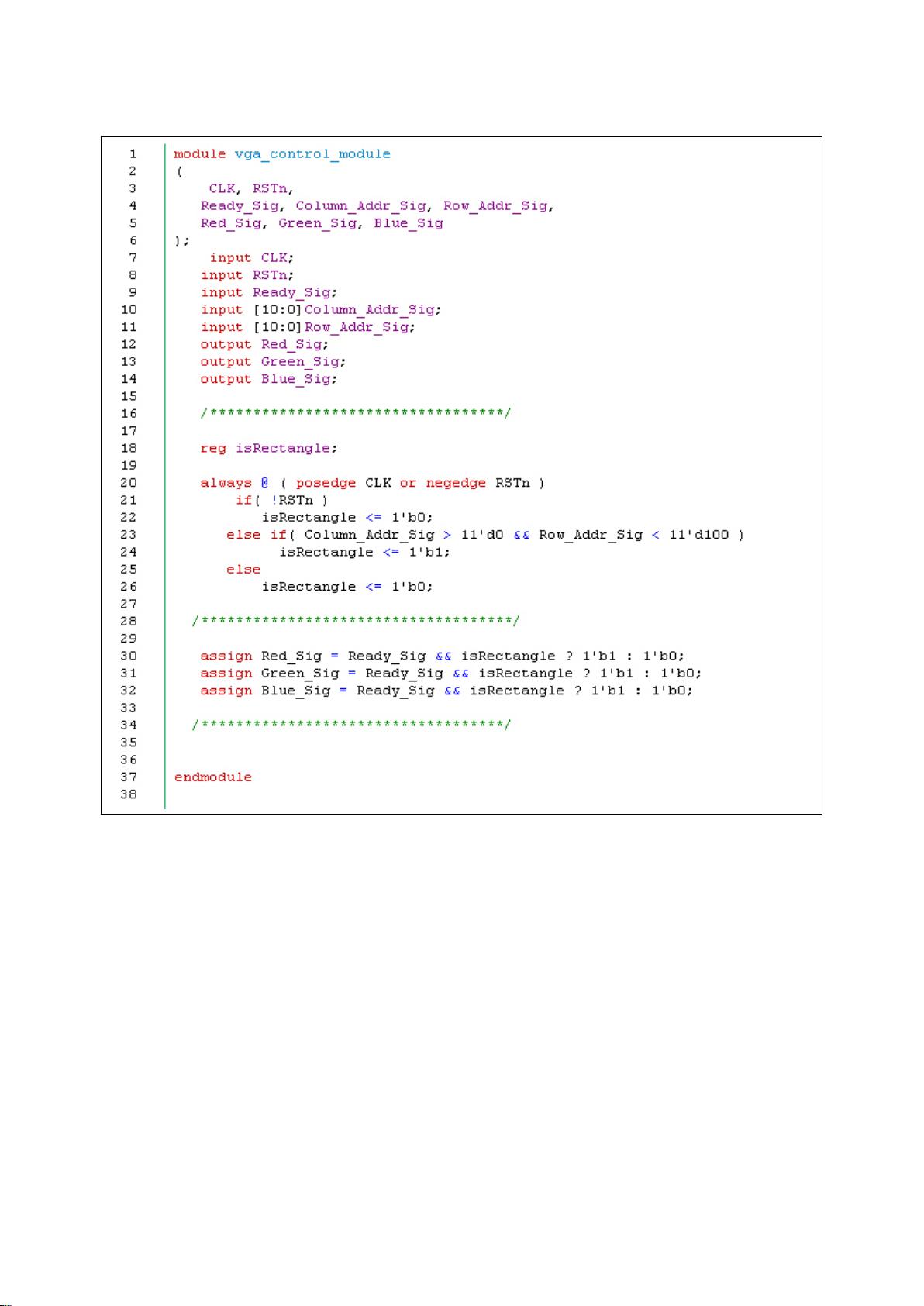

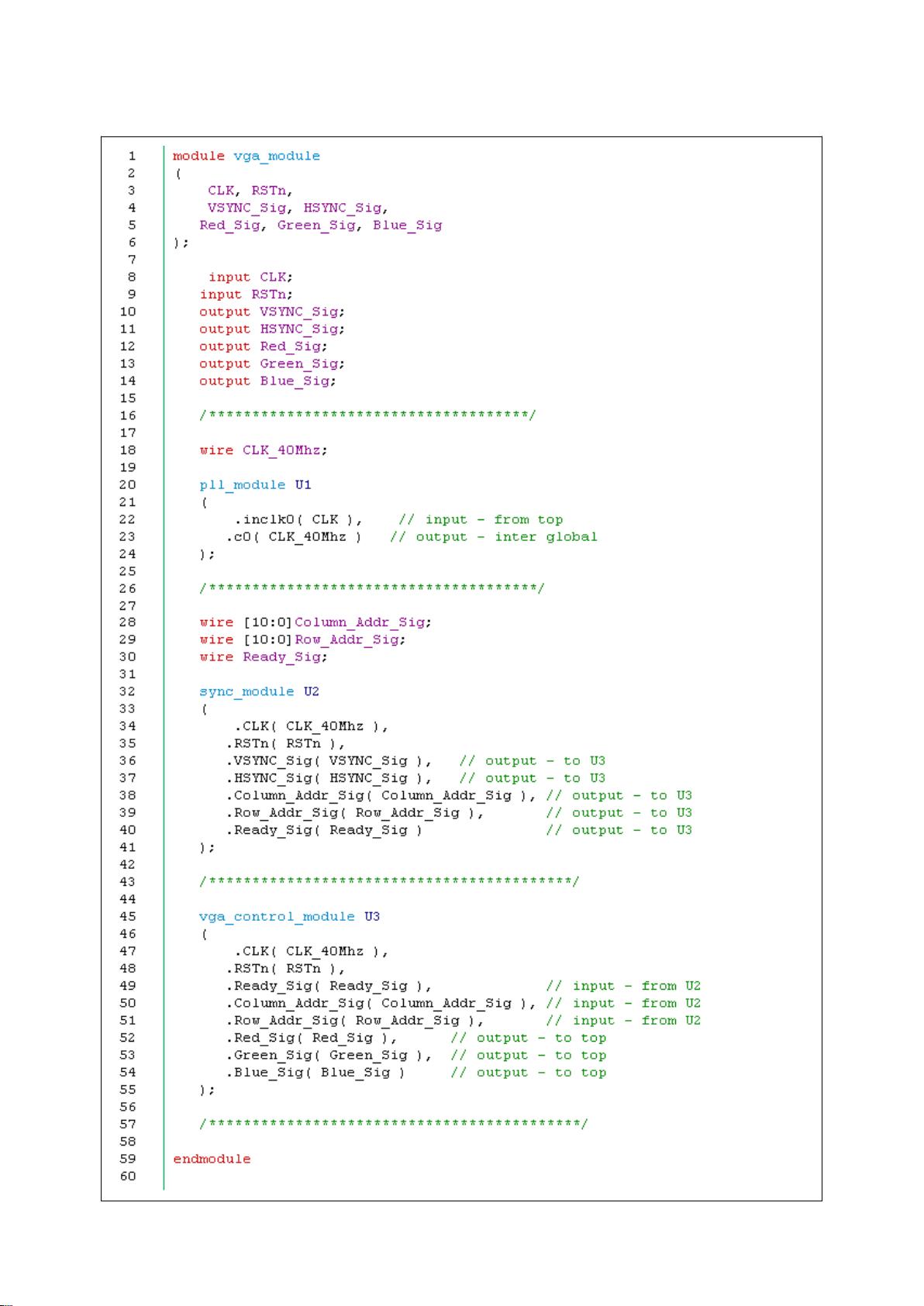

实验九涉及到的是VGA(Video Graphics Array)驱动设计,这是FPGA学习者常用来练习的一个经典实验。VGA是一种模拟视频接口,广泛应用于显示器与计算机之间的连接。在FPGA中实现VGA驱动,可以帮助开发者深入理解时序控制和数字信号处理。

VGA硬件接口包括了HSYNC(水平同步信号)、VSYNC(垂直同步信号)和RGB(红绿蓝)颜色信号。HSYNC指示显示器何时开始读取新的一行数据,VSYNC则指示开始新的一帧。RGB信号则传输像素的颜色信息。

VGA协议的核心是其时序。一帧图像由固定的行数(例如600行)和列数(例如800列)组成,并以特定的刷新率(如60Hz)进行刷新。在800x600x60Hz的显示标准下,每一行的扫描包括了超过800个列像素,每一帧则包含超过600行扫描。HSYNC和VSYNC信号控制着这种扫描过程。HSYNC的同步段、后廊段、激活段和前廊段共同定义了有效数据传输的边界。VSYNC则类似,通过行同步信号控制显示器开始新的帧。

HSYNC的同步段(a段)拉低,表示行扫描的开始;后廊段(b段)拉高,用于提供额外的间隔;激活段(c段)是真正传输图像数据的部分;前廊段(d段)再次拉高,作为下一行扫描的准备。VSYNC信号的工作方式类似,但控制的是帧的开始。

VGA驱动实验对于初学者来说具有一定的挑战性,因为它要求精确控制时序以确保图像正确显示。通过这个实验,设计师能够掌握如何在FPGA中生成这些复杂的时序信号,以及如何用硬件描述语言(如VHDL或Verilog)来描述和实现这样的逻辑。

这个资源提供了关于FPGA设计和VGA驱动的实践知识,对于想要深入理解和应用FPGA技术的人来说是非常有价值的。通过学习和实践这些例程,开发者不仅能提升FPGA设计技能,还能对数字系统设计有更深入的理解。

2018-12-27 上传

2019-12-26 上传

2023-03-09 上传

2023-09-24 上传

2024-01-31 上传

2024-12-19 上传

2023-05-16 上传

2023-11-26 上传