"FIR IP核使用与特性总览"

需积分: 5 20 浏览量

更新于2024-03-12

1

收藏 2.39MB PDF 举报

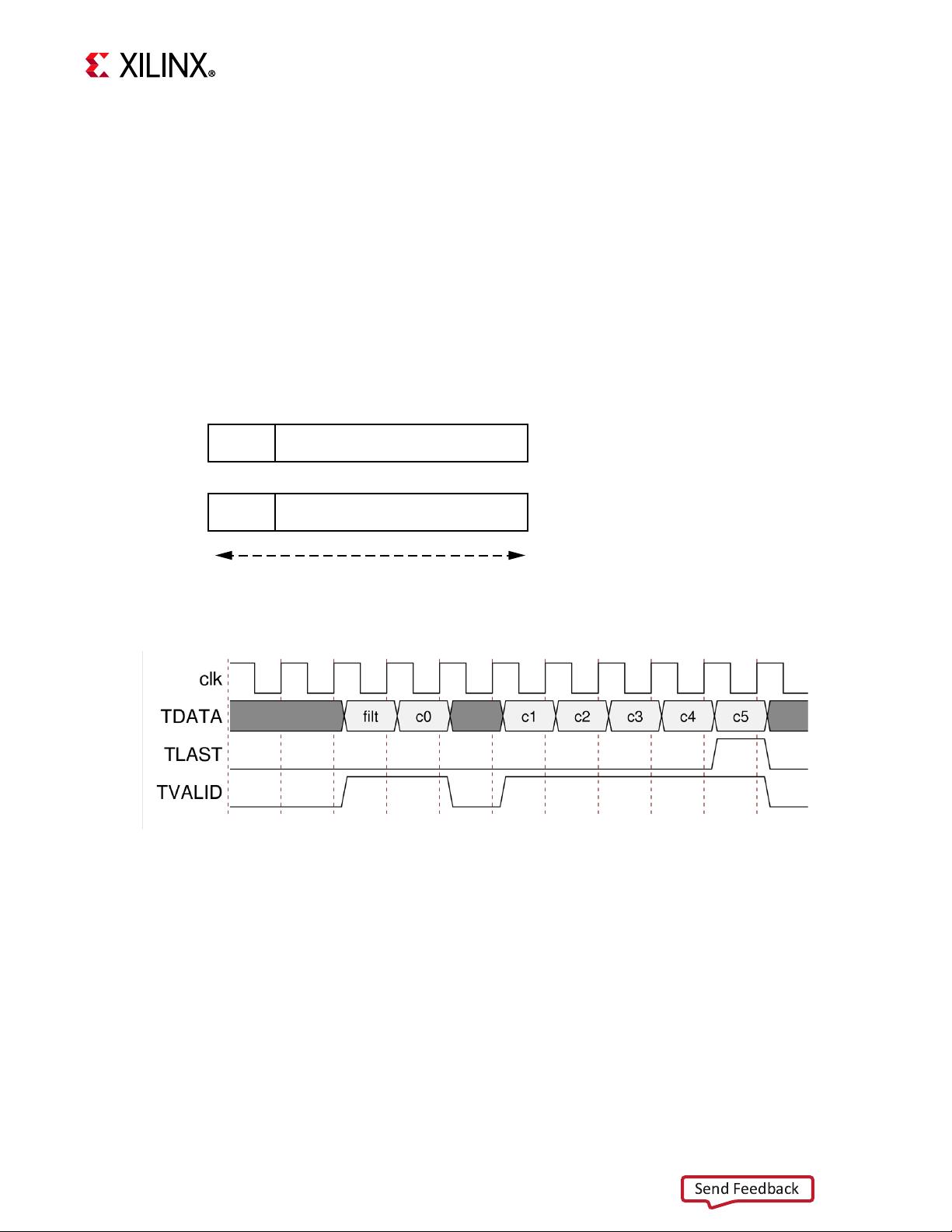

The FIR IP核 (Finite Impulse Response Intellectual Property core) is a customizable digital filter IP core developed by Xilinx. It is designed to be used with Xilinx's ISE and Vivado Design Suite tools for FPGA and SoC designs. The FIR Compiler v7.2 LogiCORE IP Product Guide provides comprehensive information on the capabilities and features of the FIR IP core.

The FIR IP core supports various types of digital filters, including high-pass, low-pass, band-pass, and band-stop filters, enabling users to implement a wide range of signal processing applications. It offers flexibility in terms of filter order, coefficients, and input/output data widths, allowing for customization to meet specific design requirements.

The IP Product Guide provides detailed guidance on how to navigate the content based on the design process, helping users effectively utilize the FIR IP core in their designs. It also includes information on the features and capabilities of the FIR IP core, as well as best practices for incorporating it into FPGA and SoC designs.

Overall, the FIR IP core is a versatile and efficient solution for implementing digital filtering in FPGA and SoC designs. Its customizable nature and support for various filter types make it a valuable tool for signal processing applications, offering users the flexibility and performance needed to achieve their design goals.

1380 浏览量

122 浏览量

210 浏览量

1824 浏览量

2011-10-27 上传

342 浏览量

3103 浏览量

Gate_coding

- 粉丝: 10

- 资源: 17

最新资源

- 中国项目管理师培训讲义——费用管理

- SWF:一些用于处理SWF文件的python脚本

- 作品集:专为展示我的所有作品而创建的项目

- neural_network_projects:这是一些基本的神经网络

- STSensNet_Android:“ ST BLE StarNet” Android应用程序源代码-Android application source code

- SLIC-ImageSegmentation:基于SLIC图像分割算法实现一个比PS魔棒工具还方便的抠图工具

- yet-another-istanbul-mocha-no-coverage

- 四卡功能

- android 一个杀进程 程序分享,包含源代码-网络攻防文档类资源

- babel_pug_project:通过babel,pug,node,express进行Web服务器教育.....

- 爱普生7710 7720l免芯片固件刷rom附安装说明

- GenericInstsBenchmark

- AK_Lab2

- MADSourceCodes:“使用Android移动应用程序开发”课程源代码-Android application source code

- themeweaver:使用设计标记在浏览器中创建kick-ass IDE主题!

- oo-way-getonboard中的战舰:GitHub Classroom创建的oo-way-getonboard中的战舰