AL-RUBAYE AND REBEIZ: ANALYSIS AND DESIGN OF WIDEBAND I/Q CMOS 100–200 Gb/s MODULATORS 2373

a wideband quadrature signal generator, wideband buffers,

and two current-combined DC-100 GHz low-noise double-

balanced mixers. The I/Q modulator achieves 200 Gb/s

in 16-QAM (50 Gbaud/s), while consuming 200 mW, resulting

in a record 1-pJ/bit modulation efficiency. In addition to

backhaul links, the modulator is an attractive and cost-effective

alternative to short-range optical links for data center intercon-

nects (DCI) applications. Future work may include increasing

the modulator output power to alleviate the need for an

additional power amplifier stage.

A

CKNOWLEDGMENT

The authors would like to thank Keysight for the

M8196 AWG and for technical support and Integrand for the

EMX simulation software.

R

EFERENCES

[1] A. Boveda and J. I. Alonso, “A 0.7-3 GHz GaAs QPSK/QAM direct

modulator,” IEEE J. Solid-State Circuits, vol. 28, no. 12, pp. 1340–1349,

Dec. 1993.

[2] Y. Baeyens et al., “A wideband SiGe BiCMOS transceiver chip-set

for high-performance microwave links in the 5.6–43.5 GHz range,”

in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), Jun. 2017,

pp. 376–379.

[3] H. Al-Rubaye and G. M. Rebeiz, “W-band direct-modulation >20-Gb/s

transmit and receive building blocks in 32-nm SOI CMOS,” IEEE J.

Solid-State Circuits, vol. 52, no. 9, pp. 2277–2291, Sep. 2017.

[4] K. Khalaf et al., “Digitally modulated CMOS polar transmitters for

highly-efficient mm-wave wireless communication,” IEEE J. Solid-State

Circuits, vol. 51, no. 7, pp. 1579–1592, Jul. 2016.

[5] L. Anttila, P. Handel, and M. Valkama, “Joint mitigation of power

amplifier and I/Q modulator impairments in broadband direct-conversion

transmitters,” IEEE Trans. Microw. Theory Techn., vol. 58, no. 4,

pp. 730–739, Apr. 2010.

[6] P.-Y. Wu, Y. Liu, B. Hanafi, H. Dabag, P. Asbeck, and J. Buckwalter,

“A 45-GHz Si/SiGe 256-QAM transmitter with digital predistortion,” in

IEEE MTT-S Int. Microw. Symp. Dig., May. 2015, pp. 1–3.

[7] S.-A. Yu et al., “A single-chip 125-MHz to 32-GHz signal source in

0.18-μm SiGe BiCMOS,” IEEE J. Solid-State Circuits, vol. 46, no. 3,

pp. 598–614, Mar. 2011.

[8] H. Chung, Q. Ma, and G. M. Rebeiz, “A 10–40 GHz frequency quadru-

pler source with switchable bandpass filters and > 30 dBc harmonic

rejection,” in Proc. IEEE Radio F req. Integr. Circuits Symp. (RFIC),

Jun. 2017, pp. 49–52.

[9] L. Vera and J. R. Long, “A DC-100 GHz active frequency doubler with a

low-voltage multiplier core,” IEEE J. Solid-State Circuits, vol. 50, no. 9,

pp. 1963–1973, Sep. 2015.

[10] O. Inac, M. Uzunkol, and G. M. Rebeiz, “45-nm CMOS SOI technology

characterization for millimeter-wave applications,” IEEE Trans. Microw.

Theory Techn., vol. 62, no. 6, pp. 1301–1311, Jun. 2014.

[11] A. K. Gupta and J. F. Buckwalter, “Linearity considerations for

low-EVM, millimeter-wave direct-conversion modulators,” IEEE Trans.

Microw. Theory Techn., vol. 60, no. 10, pp. 3272–3285, Oct. 2012.

[12] A. A. M. Saleh, “Frequency-independent and frequency-dependent non-

linear models of TWT amplifiers,” IEEE Trans. Commun., vol. 29,

no. 11, pp. 1715–1720, Nov. 1981.

[13] S. Golara, S. Moloudi, and A. A. Abidi, “Processes of AM-PM distortion

in large-signal single-FET amplifiers,” IEEETrans.CircuitsSyst.I,Reg.

Papers, vol. 64, no. 2, pp. 245–260, Feb. 2017.

[14] C. Wang, M. Vaidyanathan, and L. E. Larson, “A capacitance-

compensation technique for improved linearity in CMOS class-AB

power amplifiers,” IEEE J. Solid-State Circuits, vol. 39, no. 11,

pp. 1927–1937, Nov. 2004.

[15] Q. Gu, RF System Design Transceivers for Wireless Commun.,1sted.

Springer, 2005.

[16] S. H. Hall and H. L. Heck, Advanced Signal Integrity for High-Speed

Digital Designs. Hoboken, NJ, USA: Wiley, 2009.

[17] C. Thakkar, “Design of multi-Gb/s multi-coefficient mixed-

signal equalizers,” Ph.D. dissertation, Univ. California, Berkeley,

CA, USA, 2012. [Online]. Available: https://www.eecs.berkeley.

edu/Pubs/TechRpts/2014/EECS2014-189.html

[18] A. J. Viterbi, “Wireless digital communication: A view based on three

lessons learned,” IEEE Commun. Mag., vol. 29, no. 9, pp. 33–36,

Sep. 1991.

[19] P. Asbeck, Linearization Techniques. San Diego, CA, USA: UCSD.

2014.

[20] S. Shopov, A. Balteanu, and S. P. Voinigescu, “A 19 dBm, 15 Gbaud,

9 bit SOI CMOS power-DAC cell for high-order QAM W-band trans-

mitters,” IEEE J. Solid-State Circuits, vol. 49, no. 7, pp. 1653–1664,

Jul. 2014.

[21] S. Voinigescu, High-Frequency Integr. Circuits. Cambridge, U.K.: Cam-

bridge Univ. Press, 2013.

[22] A. Ghilioni, A. Mazzanti, and F. Svelto, “Analysis and design of

mm-Wave frequency dividers based on dynamic latches with load

modulation,” IEEE J . Solid-State Circuits, vol. 48, no. 8, pp. 1842–1850,

Aug. 2013.

[23] N. Weiss, S. Shopov, P. Schvan, P. Chevalier, A. Cathelin, and

S. P. Voinigescu, “DC-62 GHz 4-phase 25% duty cycle quadrature

clock generator,” in Proc. IEEE Compound Semiconductor Integr. Circuit

Symp. (CSICS), Oct. 2017, pp. 1–4.

[24] K. Kibaroglu and G. M. Rebeiz, “A 0.05–6 GHz voltage-mode harmonic

rejection mixer with up to 30 dBm in-band IIP3 and 35 dBc HRR in

32 nm SOI CMOS,” in Proc. IEEE Radio Freq. Integr. Circuits Symp.

(RFIC), Jun. 2017, pp. 304–307.

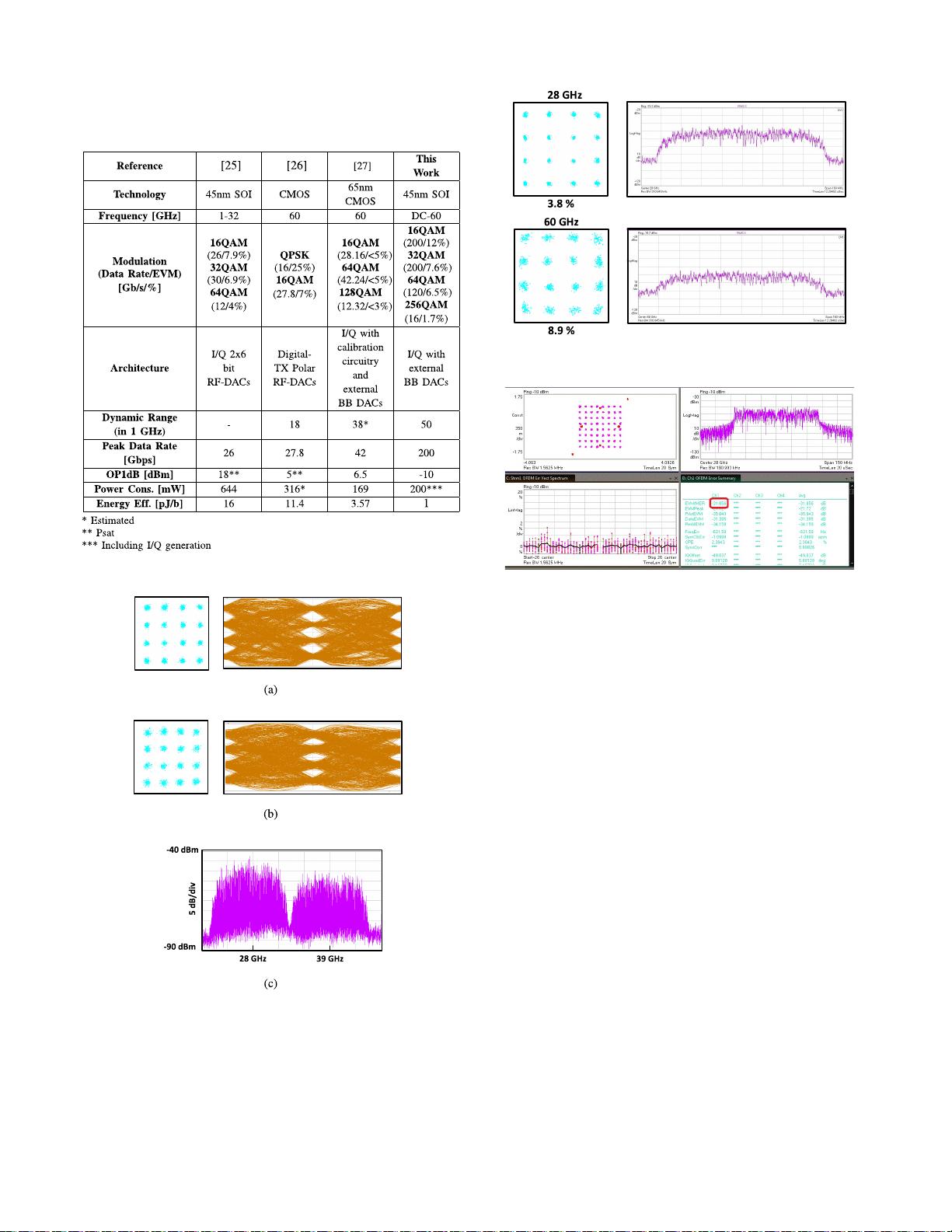

[25] S. Shopov, N. Cahoon, and S. P. Voinigescu, “Ultra-broadband I/Q RF-

DAC transmitters,” IEEE Trans. Microw. Theory Techn., vol. 65, no. 12,

pp. 5411–5421, Dec. 2017.

[26] S. Daneshgar et al., “A 27.8Gb/s 11.5pJ/b 60GHz transceiver in 28nm

CMOS with polarization MIMO,” in IEEE ISSCC Dig. Tech. Papers,

Feb. 2018, pp. 166–168.

[27] J. Pang et al., “24.9 A 128-QAM 60GHz CMOS transceiver for

IEEE802.11ay with calibration of LO feedthrough and I/Q imbalance,”

in IEEE ISSCC Dig. Tech. Papers, Feb. 2017, pp. 424–425.

[28] O. El-Aassar and G. M. Rebeiz, “4.7 A compact DC-to-108 GHz

stacked-SOI distributed PA/driver using multi-drive inter-stack coupling,

achieving 1.525 THz GBW, 20.8 dBm peak P1dB, and over 100 Gb/s in

64-QAM and PAM-4 modulation,” in IEEE ISSCC Dig. Tech. Papers,

Feb. 2019, pp. 86–88.

Hasan Al-Rubaye (S’11) received the B.Sc. degree

in electrical engineering from the University of

Toronto, Toronto, ON, Canada, in 2013, and the

Ph.D. degree from the University of California at

San Diego (UCSD), San Diego, CA, USA, in 2018.

He held internships with Advanced Micro

Devices (AMD) and Nokia Bell Labs, where he

was involved in research and development efforts in

mm-wave phased array systems. From March 2018

to June 2019, he was at Roshmere, Inc., working

on 64 Gbaud RF front ends for 400G and 800G

optical coherent systems. He is currently an R&D IC Design Engineer in the

Wireless Communications and Connectivity (WCC) division at Broadcom,

Inc., San Diego, CA.

Dr. Al-Rubaye was a recipient of the ISSCC Analog Devices Outstanding

Designer Award and the Best Conference Paper Award twice during the course

of his graduate studies.