© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

User manual Rev. 01 — 12 January 2006 20

Philips Semiconductors

UM10161

Volume 1 Chapter 3: System control block

3.5.3 Interrupt Wake-up register (INTWAKE - 0xE01F C144)

Enable bits in the INTWAKE register allow the external interrupts and other sources to

wake up the processor if it is in Power-down mode. The related EINTn function must be

mapped to the pin in order for the wake-up process to take place. It is not necessary for

the interrupt to be enabled in the Vectored Interrupt Controller for a wake-up to take place.

This arrangement allows additional capabilities, such as having an external interrupt input

wake up the processor from Power-down mode without causing an interrupt (simply

resuming operation), or allowing an interrupt to be enabled during Power-down without

waking the processor up if it is asserted (eliminating the need to disable the interrupt if the

wake-up feature is not desirable in the application).

For an external interrupt pin to be a source that would wake up the microcontroller from

Power-down mode, it is also necessary to clear the corresponding bit in the External

Interrupt Flag register (see Section 3.5.2 on page 19

).

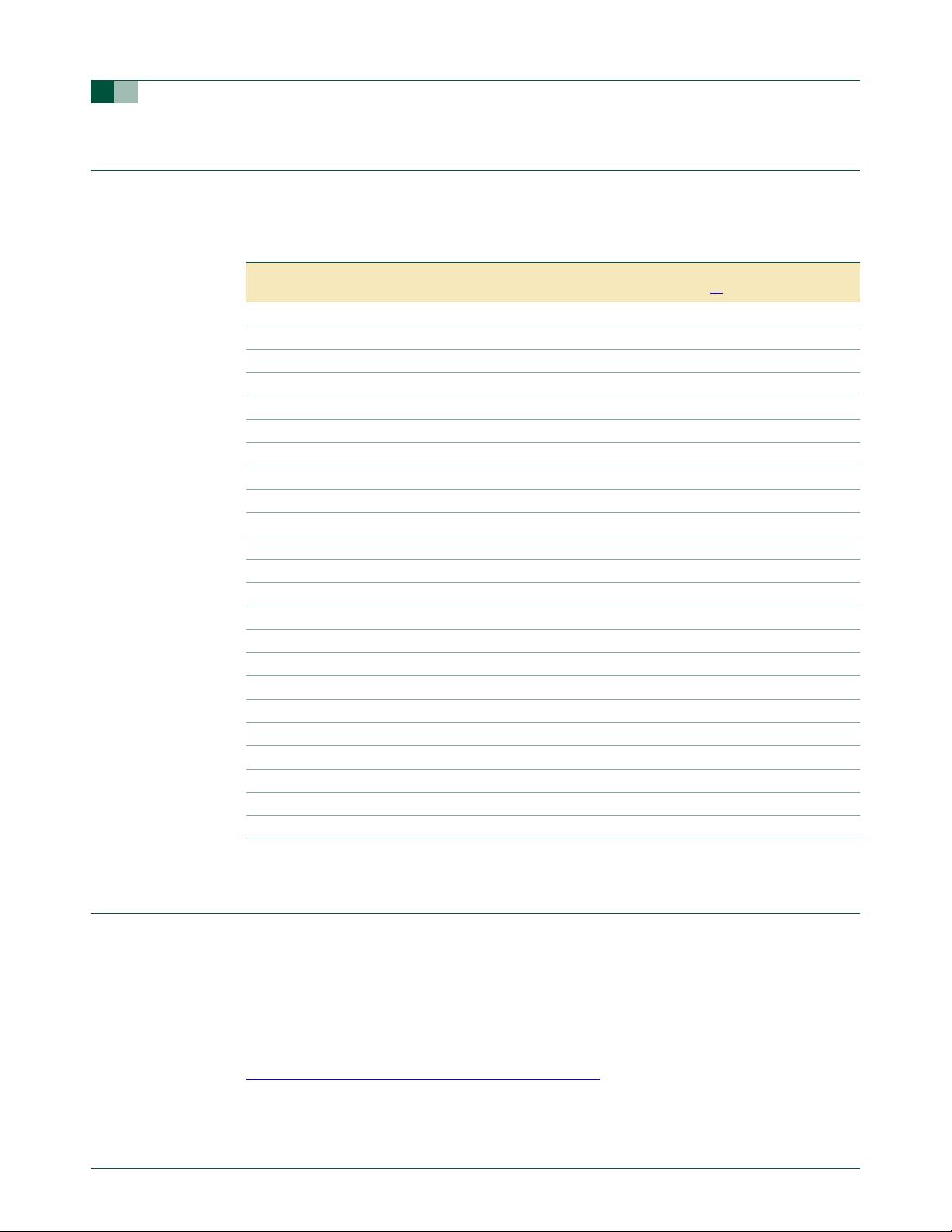

Table 9: External Interrupt Flag register (EXTINT - address 0xE01F C140) bit description

Bit Symbol Description Reset

value

0 EINT0 In level-sensitive mode, this bit is set if the EINT0 function is selected for its pin, and the pin is in

its active state. In edge-sensitive mode, this bit is set if the EINT0 function is selected for its pin,

and the selected edge occurs on the pin.

This bit is cleared by writing a one to it, except in level sensitive mode when the pin is in its active

state (e.g. if EINT0 is selected to be LOW level sensitive and a LOW level is present on the

corresponding pin, this bit can not be cleared; this bit can be cleared only when the signal on the

pin becomes HIGH).

0

1 EINT1 In level-sensitive mode, this bit is set if the EINT1 function is selected for its pin, and the pin is in

its active state. In edge-sensitive mode, this bit is set if the EINT1 function is selected for its pin,

and the selected edge occurs on the pin.

This bit is cleared by writing a one to it, except in level sensitive mode when the pin is in its active

state (e.g. if EINT1 is selected to be LOW level sensitive and a LOW level is present on the

corresponding pin, this bit can not be cleared; this bit can be cleared only when the signal on the

pin becomes HIGH).

0

2 EINT2 In level-sensitive mode, this bit is set if the EINT2 function is selected for its pin, and the pin is in

its active state. In edge-sensitive mode, this bit is set if the EINT2 function is selected for its pin,

and the selected edge occurs on the pin.

This bit is cleared by writing a one to it, except in level sensitive mode when the pin is in its active

state (e.g. if EINT2 is selected to be LOW level sensitive and a LOW level is present on the

corresponding pin, this bit can not be cleared; this bit can be cleared only when the signal on the

pin becomes HIGH).

0

7:3 - Reserved, user software should not write ones to reserved bits. The value read from a reserved

bit is not defined.

NA

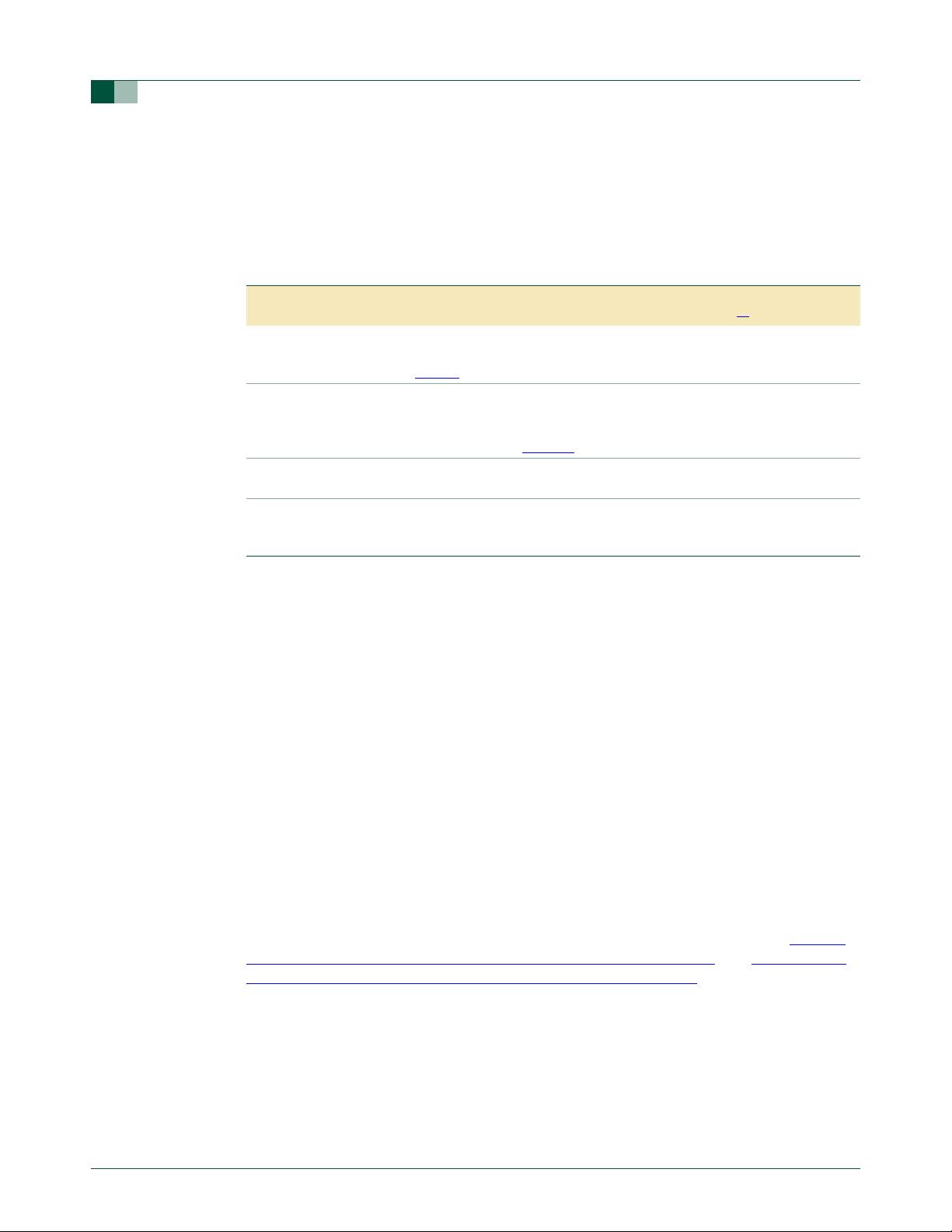

Table 10: Interrupt Wake-up register (INTWAKE - address 0xE01F C144) bit description

Bit Symbol Description Reset

value

0 EXTWAKE0 When one, assertion of EINT0 will wake up the processor from

Power-down mode.

0

1 EXTWAKE1 When one, assertion of EINT1 will wake up the processor from

Power-down mode.

0