Xilinx CPLD/FPGA规格:5V兼容高性能设计与In-system Programmability

需积分: 1 37 浏览量

更新于2024-08-03

收藏 205KB PDF 举报

本文档是Xilinx(赛灵思)公司关于CPLD (复杂可编程逻辑器件)和FPGA (现场可编程门阵列)的规格书,标题为"C45126_可编程逻辑器件(CPLD-FPGA规格书) - Xilinx技术",发布日期为2007年4月3日。该产品具有以下主要特点:

1. **延迟时间优化**:CPLD-FPGA设计有5纳秒的内部引脚到引脚逻辑延迟,确保高速数据处理性能。

2. **高系统频率**:器件支持高达178兆赫兹的系统工作频率,适应对速度有较高要求的应用场景。

3. **宏单元及可用门数**:产品包含144个宏单元,每个单元内有3,200个可用门,提供了丰富的逻辑设计空间。

4. **多种封装选择**:该器件提供小尺寸封装,如100-pin TQFP (81个用户输入/输出引脚),144-pin TQFP (117个用户输入/输出引脚),以及144-pin CSP (117个用户输入/输出引脚),满足不同应用的体积需求。

5. **绿色制造**:所有封装类型都提供无铅选项,符合环保标准。

6. **电源兼容性**:设计专为3.3伏高性能系统优化,同时也支持低功耗模式。输入/输出引脚兼容3.3伏、2.5伏和5伏信号,输出可以是3.3伏或2.5伏,增加了设计灵活性。

7. **先进工艺**:采用先进的0.35微米CMOS工艺,配合FastFLASH技术,实现快速编程和高效的电路实现。

8. **系统级功能**:支持在系统编程(ISP),这意味着用户可以在设备运行时更新或修改其逻辑配置,提高了产品的灵活性。

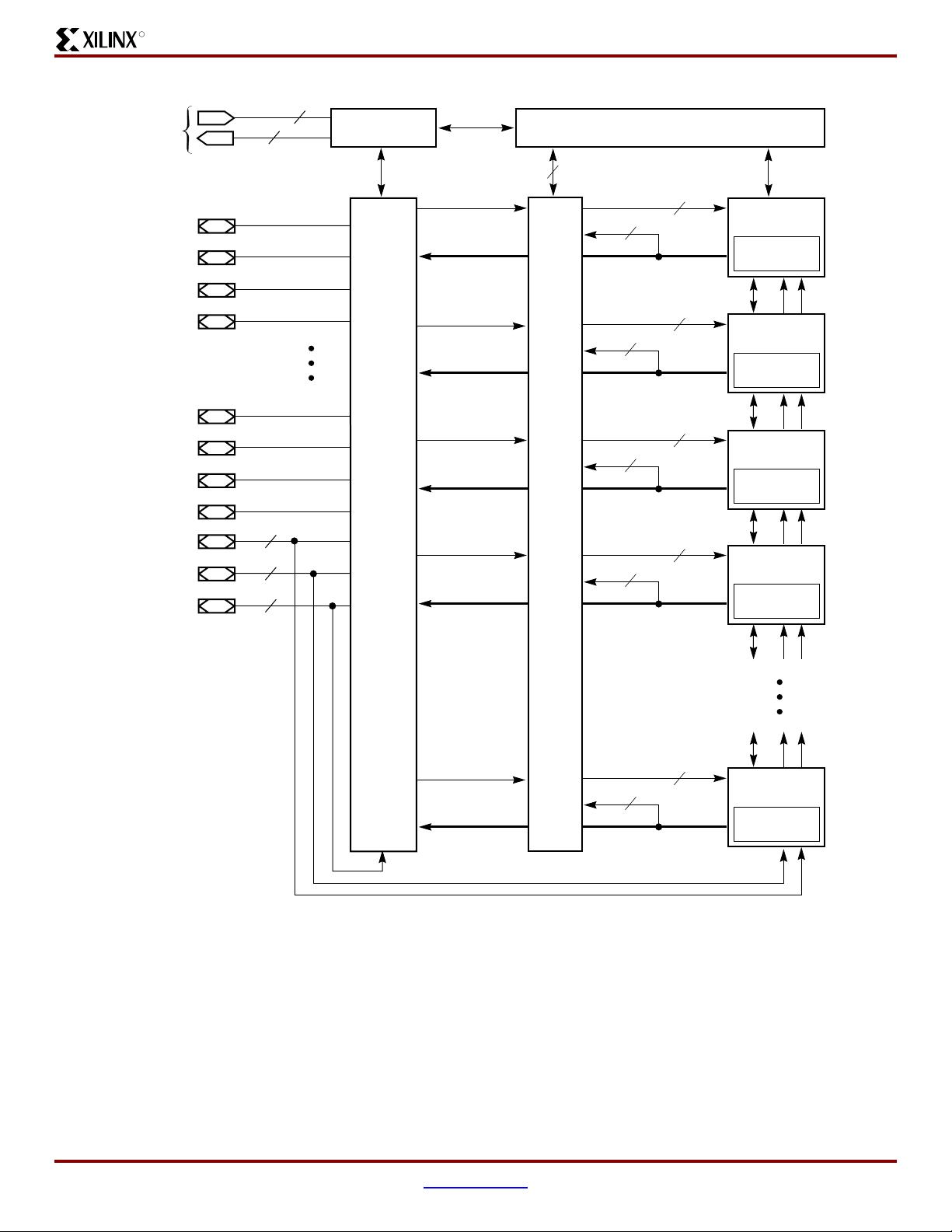

9. **高效连接性**:FastCONNECT™ II开关矩阵提供了出色的引脚锁定和布线灵活性,有助于简化电路设计。

10. **增强的函数块**:器件内置的54路输入的 Extrawide Function Blocks,增强了并行处理能力。

11. **高级逻辑密度**:每个宏单元最多支持90个产品项,允许精细的逻辑定制和复用。

这份规格书详细阐述了Xilinx的CPLD-FPGA产品在性能、功耗、接口兼容性和创新技术方面的特性,为电子工程师在选择和设计使用这类可编程逻辑器件时提供了重要的参考依据。

2023-09-20 上传

2023-11-26 上传

2023-09-20 上传

2023-11-26 上传

2022-11-15 上传

2021-07-13 上传

2021-09-17 上传

2022-07-15 上传

manylinux

- 粉丝: 4456

- 资源: 2494

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率