单片机+FPGA网络数据加密:VHDL硬件实现与安全性提升

24 浏览量

更新于2024-08-31

收藏 455KB PDF 举报

该篇文章主要探讨了在EDA/PLD(电子设计自动化/可编程逻辑器件)技术背景下,如何实现基于单片机和FPGA(现场可编程门阵列)的网络数据加密。文章的核心内容围绕以下几个关键点展开:

1. 系统架构:系统的构建主要包括单片机、FPGA以及E1通信接口,这些组件协同工作以确保数据的安全传输。单片机负责控制和协调,而FPGA作为硬件平台,执行加密算法的底层处理。

2. 加密算法:流密码加密算法采用A5/l和W7算法,这两种算法是高效的加密手段,能够在数据传输过程中提供高强度的保护。流密码的特点是实时生成密钥流,使得即使密钥泄露,也无法轻易复原过去的数据。

3. 硬件实现:FPGA内部的算法使用VHDL(Verilog Hardware Description Language)硬件描述语言编写,这种语言使得算法可以直接转化为硬件电路,提高了加密性能并减少了软件层面的攻击面。

4. 安全性:硬件实现的加密系统具有显著的优势,不依赖于CPU资源,加密过程独立且与外部总线隔离,这意味着它能提供高度的数据保护,抵御各种形式的攻击。此外,FPGA的灵活性使得算法可以轻松更新,保持系统安全性。

5. 应用场景:该系统适用于对数据安全有严格要求的环境,例如计算机网络、银行POS机等,确保在数据传输过程中,无论是保密性还是完整性都得到了充分保障。

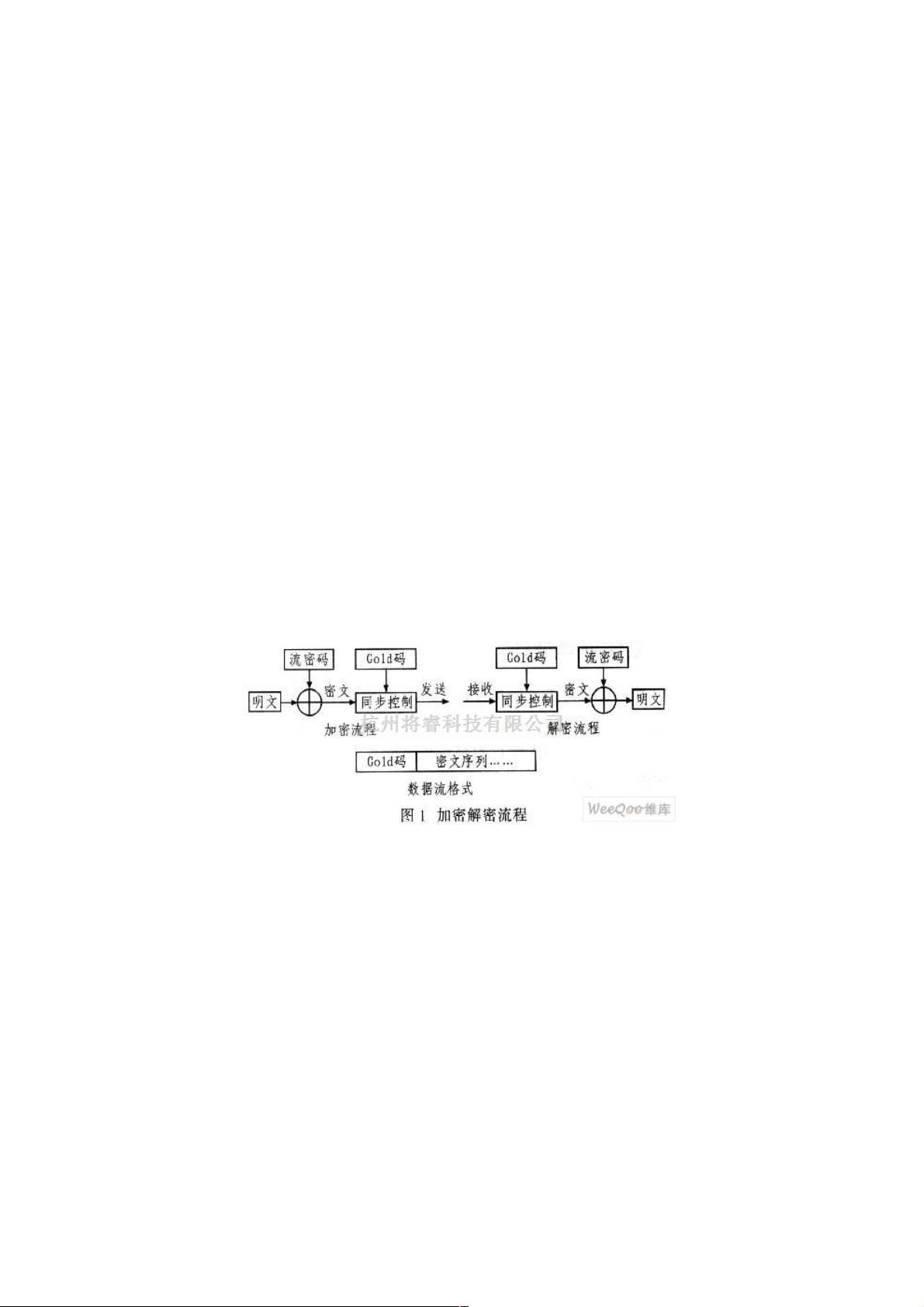

6. 加密原理:文章详细解释了流加密解密的过程,包括密钥管理、同步流密码的工作方式,以及如何通过加入同步数据和使用Gold码来实现数据的同步和解密。

这篇文章深入浅出地展示了如何利用单片机和FPGA结合VHDL技术,构建一个高效且安全的网络数据加密系统,对于理解和应用EDA/PLD技术在信息安全领域的实践具有重要意义。

171 浏览量

点击了解资源详情

点击了解资源详情

217 浏览量

157 浏览量

161 浏览量

130 浏览量

207 浏览量

134 浏览量

weixin_38557935

- 粉丝: 0

最新资源

- 酷炫烟花效果实现HTML教程

- Java期末项目:学生成绩管理系统功能解析

- 单片机滤波方法应用与调整技巧

- twain编程范例源代码详解

- LeetCode挑战:展示OOP与Python算法思维

- Spring 3.0与ActiveMQ结合实现消息发送与接收

- FoxEditor文本编辑器新版本发布:功能更加强大

- 三个颜色风格的论文答辩PPT模板分享

- 探索nk.bin文件:独立于viewbin.exe的结构解析

- C#在Android平台使用Unity NDK的实践指南

- Android平台台球游戏开发入门教程

- SQL Server工资管理系统的数据库与文档解析

- XHImageViewer:一个支持图片全屏浏览和下载的iOS源代码

- 深入理解JDK 1.8文档:最高版本的Java开发工具

- Java SE 12虚拟机规范详细解读

- Ns2脚本分析中awk程序的应用研究