VHDL实现UART串口通信详解

"VHDL串口通信开发详解,包括UART模块设计、时钟分频、发送模块等关键部分的详细讲解。"

在电子设计领域,VHDL是一种常用的硬件描述语言,用于描述数字系统的逻辑功能。本文档主要讨论的是如何使用VHDL实现UART(通用异步收发传输器)的串口通信。UART是一种广泛应用于微处理器间的异步通信协议,它不需要同步时钟线,而是依赖于数据中的起始位和停止位来确定数据边界。

UART通信的核心在于时钟分频、接收和发送模块。在设计过程中,16倍的数据波特率的时钟采样是必要的,以确保数据传输的准确性。例如,如果数据波特率是9600bps,那么需要的时钟频率就是16 * 9600,即153.6kHz。在一个50MHz的系统时钟下,分频系数为325.52,实际设计中通常取整为325。分频模块的设计通常包括计数器和比较器,用于将高频系统时钟分频成适合UART的较低频率。

时钟分频模块的VHDL设计完成后,需要进行时序仿真以验证其正确性。通过观察仿真波形,可以确认分频器是否按照预期将时钟进行了325分频。

UART的发送模块负责将并行数据转换为串行流进行发送。发送过程分为几个步骤:首先,在空闲状态下,线路保持高电平;当接收到发送数据的指令时,线路被拉低一个数据位的时间T,然后数据从低位到高位逐位发送;所有数据发送完毕后,发送一个停止位(通常是高电平),完成一帧数据的发送。发送模块的VHDL设计需要考虑这些状态变化,并实现相应的逻辑控制。

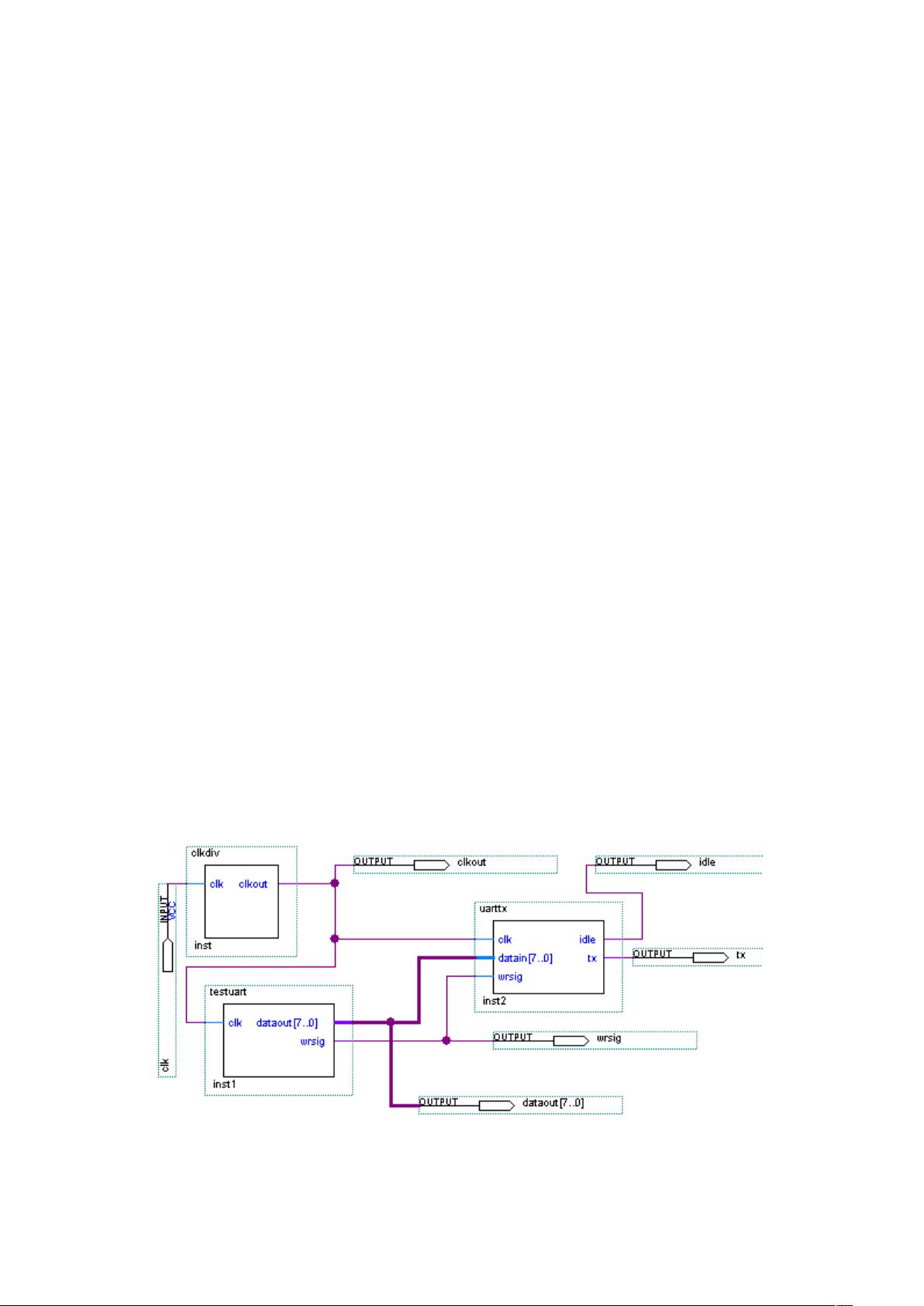

发送模块的VHDL代码通常包含输入时钟、待发送数据、发送命令和忙闲信号输出,以及串行数据输出端。在测试阶段,需要创建一个测试模块,该模块在每个时钟周期产生一个新的八位数据,以便对发送模块进行全面的时序仿真,确保其能在不同输入条件下正常工作。

VHDL串口通信设计涵盖了硬件级别的时钟管理、数据转换和通信协议的实现。理解并掌握这些知识点对于设计和调试基于FPGA或ASIC的串口通信系统至关重要。通过详细的学习和实践,工程师可以有效地实现和优化UART通信,提高系统性能和可靠性。

280 浏览量

2022-09-23 上传

134 浏览量

339 浏览量

2022-09-21 上传

zengshilun2012

- 粉丝: 0

最新资源

- Ubuntu/Mac工作站的Ansible自动化配置手册

- 掌握核心,JAVA初级面试题解析大全

- 自我测试指南:成功方法与技巧大公开

- ReactSortableHOC实现动画化可排序的触摸友好列表

- SAE开源平台:整合Spring与SMS通讯功能

- 温尼伯公交信息实时查询系统开发

- JAVA实现的可部署仓储管理信息系统详解

- ArquitecturaClass软件:探讨JavaScript的架构设计

- 掌握React项目构建与部署的capstone3指南

- 详细解读车辆购置附加费征收办法

- Java实现学生成绩管理系统的设计与功能

- 易语言实现的MDB网络数据库模块源码解析

- 艺佰设计提供清新企业Discuz模板下载

- 掌握Python中的MLEnsemble实现高效集成学习

- Java实现读取搜狗细胞词库scel文件教程

- 探索城市星球的崛起:Nature & Science精选论文