FPGA实战:数码管动态扫描技术解析

185 浏览量

更新于2024-09-03

收藏 294KB PDF 举报

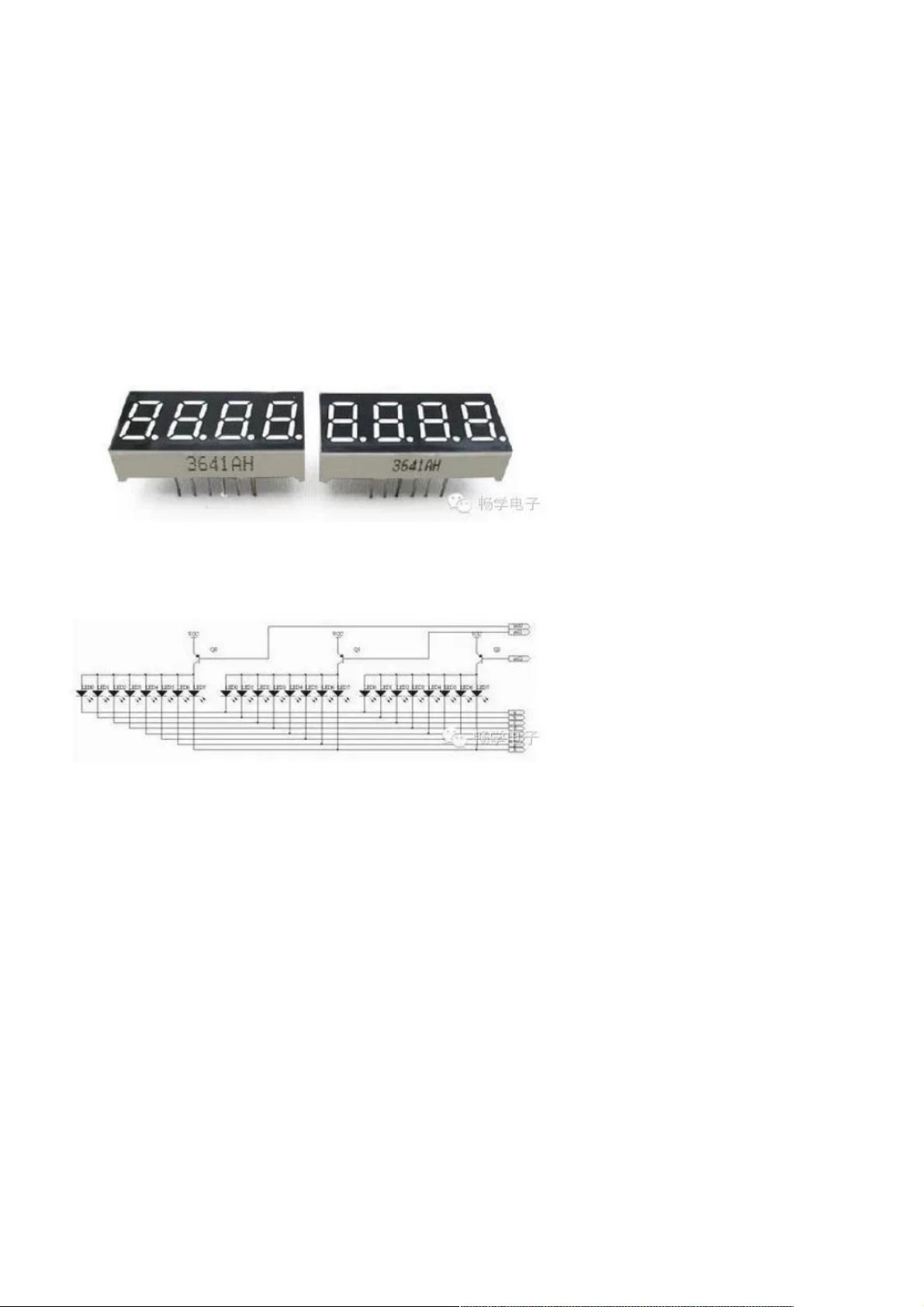

"本文介绍了如何使用FPGA进行数码管的动态扫描驱动开发,旨在实现6位7段数码管的显示,并通过4个独立按键输入数据进行验证。数码管动态扫描利用了人眼的视觉暂留效应,通过快速分时点亮各段,达到看似同时点亮的效果,避免闪烁。文中给出了3位7段数码管的等效电路图,解释了如何通过FPGA控制IO口来点亮或熄灭特定的LED段。"

深入学习FPGA之数码管动态扫描,主要针对的是在FPGA系统中如何有效地驱动数码管进行数据可视化展示。相比于单片机和ARM系统中的液晶屏,数码管由于其驱动简单和显示直观的优势,成为了FPGA的理想输出选择。实验目标设定为驱动6位7段数码管,采用BCD格式输入待显示数据,并利用4个独立按键作为交互输入,以测试驱动程序的正确性和按键消抖功能。

动态扫描技术是数码管显示的关键,它利用了人眼对于快速变化的视觉暂留现象。在每秒刷新1000次(即1KHz的刷新率)的情况下,数码管的每个段会在极短时间内交替点亮,由于这一速度远超人眼感知,所以给人的感觉是所有数码管都在同一时刻亮着,且无闪烁感。

在数码管的等效电路中,可以看到每个7段数码管由三组共24个LED组成,每组8个LED的阳极连接在一起并通过三极管与电源VCC相连。FPGA的IO口控制这些三极管的基极,当IO口输出低电平时,对应三极管导通,LED点亮。阴极部分,相同段号的LED负极连接在一起,由FPGA的其他IO口控制。通过控制不同IO口的高低电平,可以选择点亮或熄灭特定的LED段,从而实现数字的显示。

例如,若要依次显示三个不同的组合:第一个组合点亮最左边一组的led0、led5、led7,第二个组合点亮中间一组的led1、led2、led3,第三个组合点亮最右边一组的led2、led4,FPGA需按照预定顺序输出相应的控制信号,确保在规定时间内完成所有操作,保持视觉上的连续性。

数码管驱动的设计涉及到FPGA的时序控制和逻辑设计,通常需要编写Verilog或VHDL代码来实现。在实际项目中,还需要考虑电源管理、抗干扰措施以及系统级的同步问题。通过这样的实验,读者可以深入理解FPGA硬件编程的原理,提升数字逻辑设计能力,为后续的FPGA应用开发打下坚实基础。

298 浏览量

576 浏览量

2024-11-02 上传

2024-10-26 上传

2024-10-27 上传

2024-11-10 上传

2024-11-12 上传

2024-11-06 上传

weixin_38500047

- 粉丝: 9

- 资源: 978

最新资源

- 2016“华山杯”CTF php250.rar

- 基于matlab的杂草优化算法IWO仿真+仿真操作录像

- HTML5五角星探照灯文字效果特效代码

- LZW-Compression:第一次提交

- 2018--D--

- 女巫 高清壁纸 新标签页 热门传说 主题-crx插件

- lollor.github.io

- StackStuff:各种测试的源代码

- 辛格洛

- CSS3鼠标经过文字分裂特效特效代码

- win7摄像头软件 计算机自带摄像头

- github_stats_report:与机器共存GitHub Stats报告

- 注册:由ReactJ和nodeJ组成的注册平台

- yamlw_vststask:yamlw的VSTS任务

- RankPook.AdmireTop.gaKlJNg

- Girly 新标签页 热门彩色 高清壁纸 主题-crx插件