Achronix FPGA的2D高速网络:提升性能与效率的关键

68 浏览量

更新于2024-09-02

收藏 533KB PDF 举报

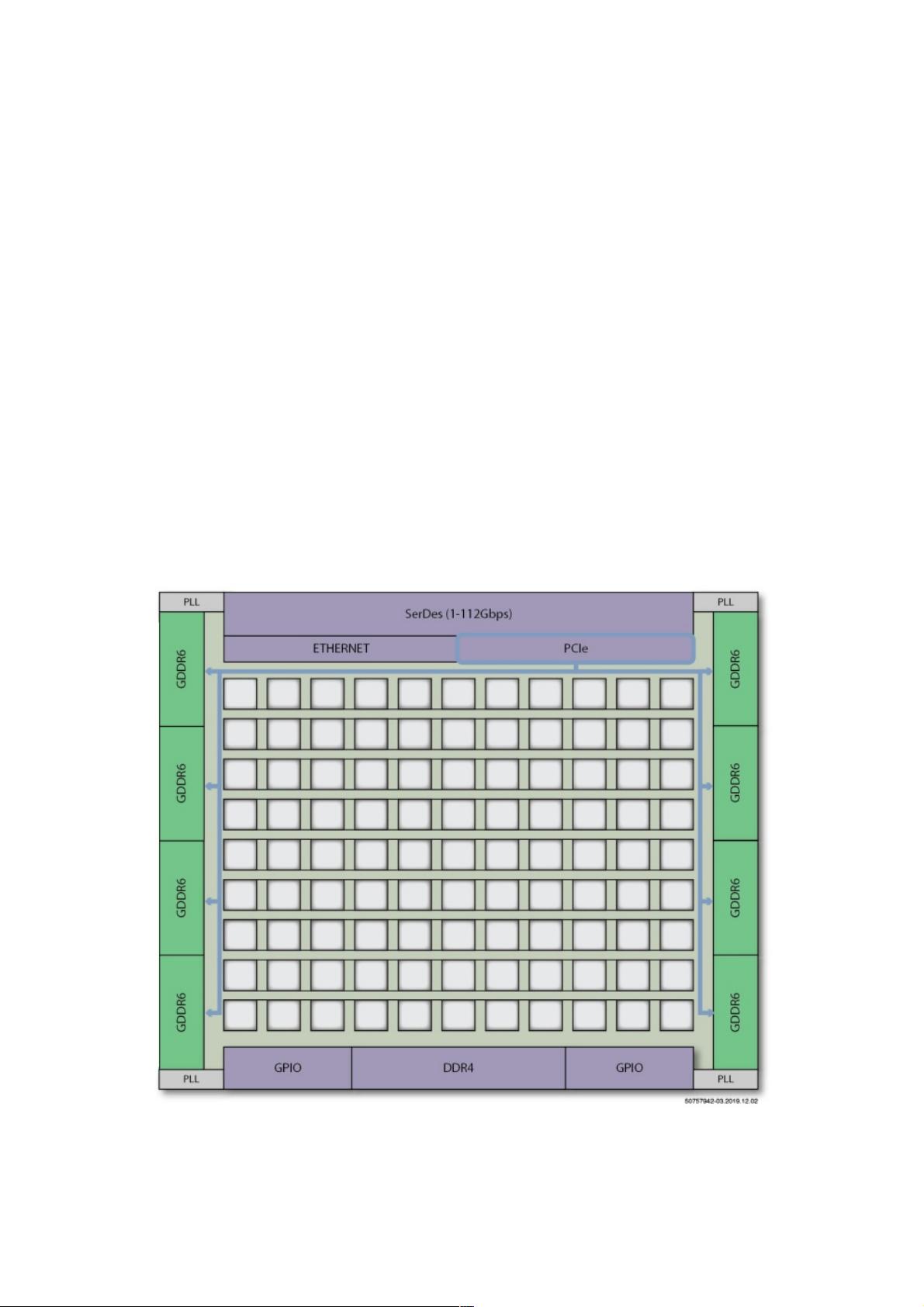

Achronix的创新在于其将传统FPGA的按位(bit-wise)布线结构提升到了一个新的高度,引入了带有片上高速网络(NoC)的FPGA技术。自从FPGA诞生以来,按位布线一直作为基础架构,它允许设计师在FPGA内构建任意逻辑功能,通过水平和垂直的独立互连线段以及开关盒实现灵活的信号路由。然而,随着高速通信标准的发展,如400G以太网、PCIe Gen5等,对数据速率的要求使得传统方法面临挑战:不断增宽的片上总线位宽导致时序收敛困难,设计者不得不在满足性能的同时进行复杂的布线优化。

传统的FPGA设计中,信号延迟和拥塞问题尤为突出,尤其是在长距离传输时,信号必须经过多个独立段,这显著降低了系统的性能。Achronix通过Speedster7tFPGA系列的二维(2D)NoC,彻底改变了这一现状。NoC是一种高性能的网络结构,它直接连接到各种高速接口,如400G以太网、PCIe Gen5等,显著减少了信号间的跳转,从而减少了延迟和拥塞,提高了数据传输速度和系统整体性能。

使用带有片上高速网络的FPGA具有以下八大优势:

1. **高性能连接**:NoC提供了一种高效的数据传输方式,减少了信号路径的复杂性和延迟,这对于实时应用和高速数据处理至关重要。

2. **时序收敛改善**:由于NoC的局部性,信号传输更直接,有助于设计师更容易地实现时序收敛,节省开发时间和资源。

3. **灵活性增强**:NoC支持不同接口间的无缝通信,使得设计者能在FPGA内构建更复杂的数据流路径,适应多种应用场景的需求。

4. **延迟减少**:与传统的按位布线相比,NoC减少了信号在多个段间的传输,从而减少了信号延迟,提高了系统响应速度。

5. **扩展性**:NoC结构能够适应未来更高带宽需求,为未来的升级和扩展提供了便利。

6. **降低复杂性**:Achronix的NoC架构减轻了设计人员在布线方面的压力,使他们能专注于核心逻辑实现。

7. **容错性提升**:NoC的冗余设计有助于提高系统可靠性,即使某个部分出现故障,也能通过其他路径维持通信。

8. **能耗效率**:通过优化的数据路径,NoC往往比传统的按位布线更能有效地利用电力,从而降低整体功耗。

Achronix的Speedster7tFPGA系列及其片上高速网络技术为FPGA设计带来了革命性的变革,提升了性能、简化了设计过程,并为未来的高速计算和通信应用奠定了坚实的基础。

112 浏览量

212 浏览量

155 浏览量

679 浏览量

207 浏览量

202 浏览量

130 浏览量

157 浏览量

weixin_38748769

- 粉丝: 10

- 资源: 924

最新资源

- 易语言3389终端修改

- Nginx1.x:Nginx1.x配置和站点模板

- kiba:用于Ruby的数据处理和ETL框架

- FRCRecycleRushPitScouter:坑侦察应用程序 2015

- Python在线考试系统后端-大学毕业设计-基于Django+Django -Rest-Framework.zip

- VBFPopFlatButton(iOS源代码)

- CSE539_Group-Project

- premierrcpdx:首要rc pdx网站

- minetesting:Minetest 游戏的客户端和模组

- jqueryEcharts-可按年月过滤.zip

- stags:Scala标签生成器

- 毕业设计:行人检测系统,pyqt + opencv .zip

- tomrolfe.com

- plot.data

- 行业资料-电子功用-凸轮控制插销式电动锁结构的介绍分析.rar

- wine-mono-deb