VHDL实现多功能数字钟设计与仿真

需积分: 12 130 浏览量

更新于2024-07-22

6

收藏 622KB DOC 举报

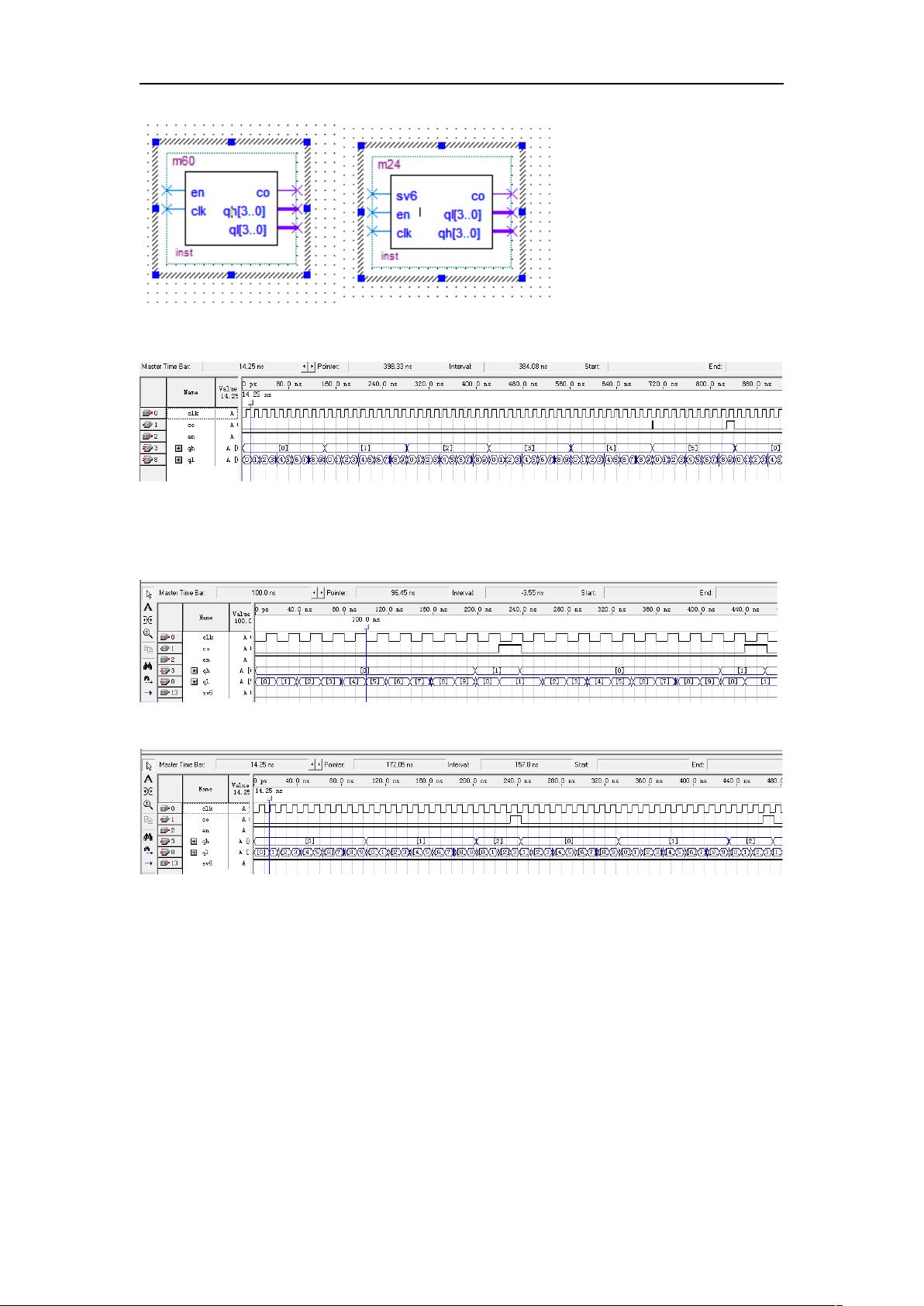

"这篇资源是关于使用VHDL设计多功能数字钟的数字逻辑课程设计报告。设计涵盖了计时器(支持24小时和12小时制转换)、闹钟、整点报时和秒表功能。设计过程中使用了QuartusII9.0工具,包含了代码实现、硬件连线图、仿真波形图以及设计者的心得体会。"

在数字逻辑设计中,VHDL是一种广泛使用的硬件描述语言,用于创建数字系统,如本案例中的多功能数字钟。这个设计项目的主要目标是提升学生对EDA(电子设计自动化)技术的理解和实践能力。以下是设计的具体细节:

1. **分频器**:设计首先从4MHz的时钟信号开始,通过分频器将其转换为1Hz的时钟,这是数字钟的基础。VHDL代码展示了如何实现这个分频,通过计数器使信号频率降低。分频器的输出作为其他模块的时钟源。

2. **计时器**:计时器由模60和模24/12计数器组成。模60计数器用于分钟的计数,而模24/12计数器则用于小时的计数,支持24小时制和12小时制之间的切换。这通过一个开关(sv6)来实现,当开关关闭(sv6=0)时,进入模12计数模式,代表12小时制;打开(sv6=1)时,进入模24计数模式。

3. **闹钟**:在基础的计时功能上,添加了闹钟模块,这可能涉及到特定时间点的触发机制,可以设置在特定小时和分钟发出警报。

4. **整点报时**:此功能在每个小时的开始时发出提示,通常是一个声音信号,表明时间已经整点。

5. **秒表**:秒表功能允许用户启动和停止时间的计数,通常用于计时短时间间隔。

6. **动态显示电路**:最后,所有这些模块的输出都需要在数字显示屏上以人类可读的形式呈现出来,这需要一个动态显示电路来处理和驱动显示器。

设计过程包括了VHDL代码的编写、硬件连线图的绘制和仿真波形的分析。通过这些步骤,设计者验证了每个模块的功能正确性,确保在实际硬件上运行时能够满足预期的设计目标。

这个VHDL设计的多功能数字钟项目提供了全面的数字逻辑设计实践经验,涵盖了从低级时钟管理到高级功能集成的各个层面,对于理解和应用EDA工具以及VHDL编程具有很高的教育价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2019-01-14 上传

2009-09-17 上传

2010-11-29 上传

2016-10-05 上传

2009-12-29 上传

athenahhh

- 粉丝: 2

- 资源: 2

最新资源

- 火炬连体网络在MNIST的2D嵌入实现示例

- Angular插件增强Application Insights JavaScript SDK功能

- 实时三维重建:InfiniTAM的ros驱动应用

- Spring与Mybatis整合的配置与实践

- Vozy前端技术测试深入体验与模板参考

- React应用实现语音转文字功能介绍

- PHPMailer-6.6.4: PHP邮件收发类库的详细介绍

- Felineboard:为猫主人设计的交互式仪表板

- PGRFileManager:功能强大的开源Ajax文件管理器

- Pytest-Html定制测试报告与源代码封装教程

- Angular开发与部署指南:从创建到测试

- BASIC-BINARY-IPC系统:进程间通信的非阻塞接口

- LTK3D: Common Lisp中的基础3D图形实现

- Timer-Counter-Lister:官方源代码及更新发布

- Galaxia REST API:面向地球问题的解决方案

- Node.js模块:随机动物实例教程与源码解析