基于FPGA的高精度TDOA时差测量系统设计与应用

88 浏览量

更新于2024-08-31

收藏 307KB PDF 举报

在EDA/PLD领域中,本文主要探讨了一种基于FPGA的高精度时差测量系统的设计与实现。时差定位(TDOA)技术在无线定位中扮演着核心角色,其精度直接影响定位的准确性。本文设计的核心是采用Altera Cyclone系列的EP1C3T144芯片,这款FPGA以其高效和灵活的特性,作为时差测算单元的基石。

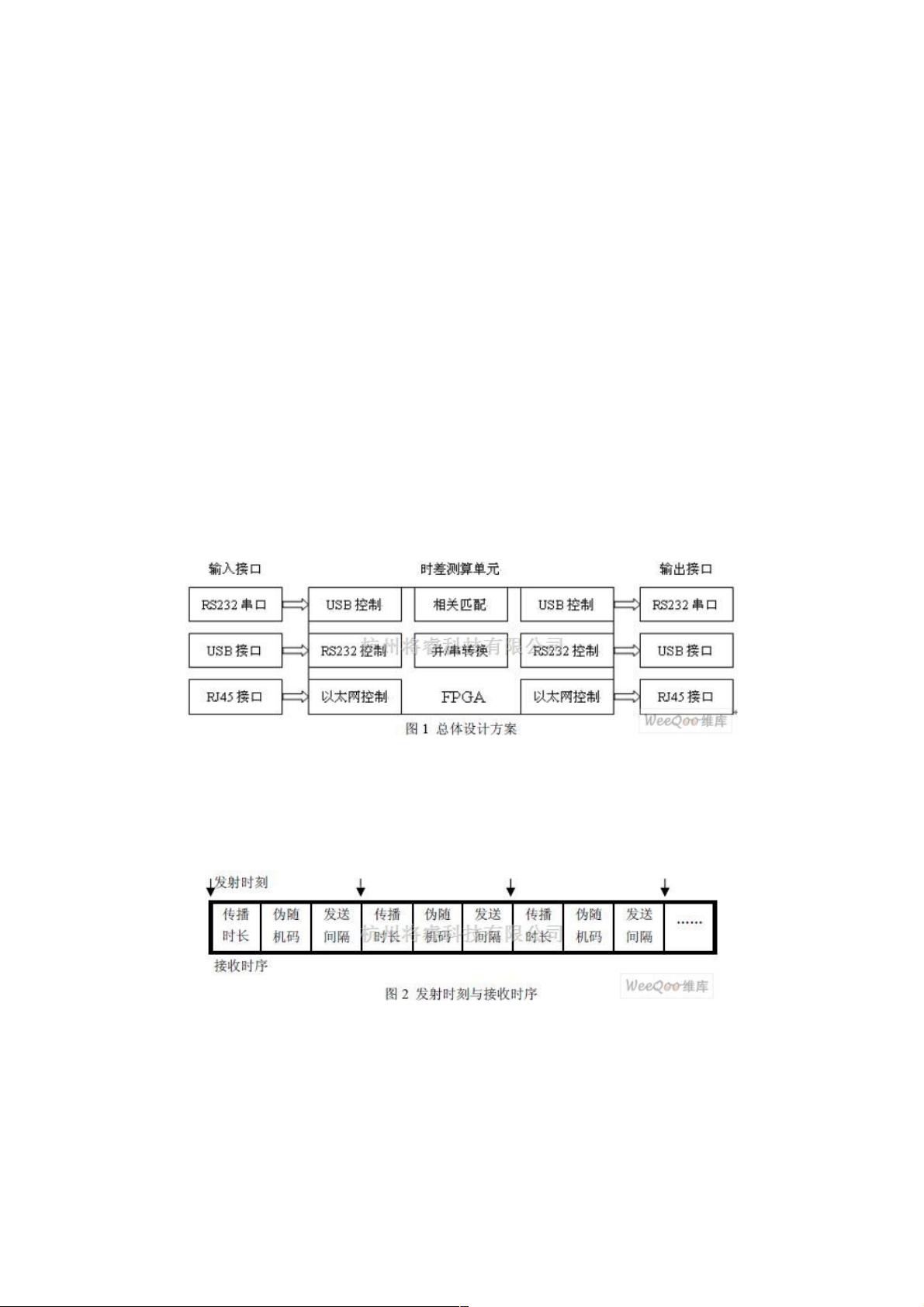

系统的关键部分是时差测算单元,它负责处理接收到的无线信号,通过比对不同路径上信号的到达时间,计算出精确的时差。FPGA的优势在于能够实时处理这些信号并执行复杂的算法,确保了测量的实时性和高精度。此外,系统还配备了以太网、USB和RS232等多种接口,使得它能够无缝集成到各种不同的无线网络和设备中,提高了系统的通用性和适应性。

设计目标包括电路简洁、成本效益高以及良好的移植性,这意味着该系统不仅适用于定位、导航和测距等专业领域,也能在其他需要高精度时间测量的应用中发挥作用。无线定位技术的进步不仅提升了服务质量,还极大地改善了人们的生活体验,特别是在智能家居、自动驾驶和物联网等领域。

1引言部分详细介绍了无线定位技术的发展趋势和TDOA技术的重要性,强调了在无线信号处理中的时差测量技术在定位中的核心作用。通过FPGA的使用,文章突出了其在抗干扰和实时性方面的优势,为实现高精度定位提供了可能。

2总体方案设计部分展示了系统架构,包括信号的输入、处理和输出流程,以及接口选择的灵活性。利用m序列编码,系统能够有效抵抗多径干扰,进一步增强了定位的可靠性。

本文的高精度时差测量系统设计是无线定位技术发展中的一项重要突破,展示了FPGA在时差测量领域的应用潜力,为无线定位技术的进一步发展提供了强有力的技术支持。

点击了解资源详情

点击了解资源详情

点击了解资源详情

285 浏览量

217 浏览量

217 浏览量

273 浏览量

248 浏览量

130 浏览量

weixin_38660108

- 粉丝: 6

最新资源

- 计算机组成原理期末试题及答案(2011参考)

- 均值漂移算法深入解析及实践应用

- 掌握npm与yarn在React和pg库中的使用

- C++开发学生信息管理系统实现多功能查询

- 深入解析SIMATIC NET OPC服务器与PLC的S7连接技术

- 离心式水泵原理与Matlab仿真教程

- 实现JS星级评论打分与滑动提示效果

- VB.NET图书馆管理系统源码及程序发布

- C#实现程序A监控与自动启动机制

- 构建简易Android拨号功能的应用开发教程

- HTML技术在在线杂志中的应用

- 网页开发中的实用树形菜单插件应用

- 高压水清洗技术在储罐维修中的关键应用

- 流量计校正方法及操作指南

- WinCE系统下SD卡磁盘性能测试工具及代码解析

- ASP.NET学生管理系统的源码与数据库教程