Intel MAX 10 FPGA ADC设计与实现指南

需积分: 10 132 浏览量

更新于2024-07-16

1

收藏 639KB PDF 举报

"该文档是Intel® MAX® 10 FPGA模数转换器用户指南,主要阐述了如何在Altera的MAX10 FPGA中使用模数转换器(ADC),包括设计流程、注意事项以及性能测试。适用于Intel® Quartus® Prime设计套件17.0版本。"

在Altera的MAX 10 FPGA系列中,模数转换器(ADC)是一个重要的组成部分,用于将模拟信号转换为数字信号,这对于许多混合信号应用至关重要。此用户指南详细介绍了MAX 10 FPGA中的ADC功能和设计考虑。

1. MAX 10模数转换器概述:

- 在MAX 10器件中,提供了多个ADC模块,每个模块可包含一个或两个独立的ADC通道。

- ADC的纵向移植支持意味着设计可以方便地从一个器件转移到另一个具有不同ADC特性的器件,而无需大规模重构。

- MAX 10系列支持单电源或双电源操作,这提供了设计灵活性,可以根据应用需求选择合适的电源配置。

- ADC转换过程涉及将模拟输入信号通过采样和量化转化为数字输出。

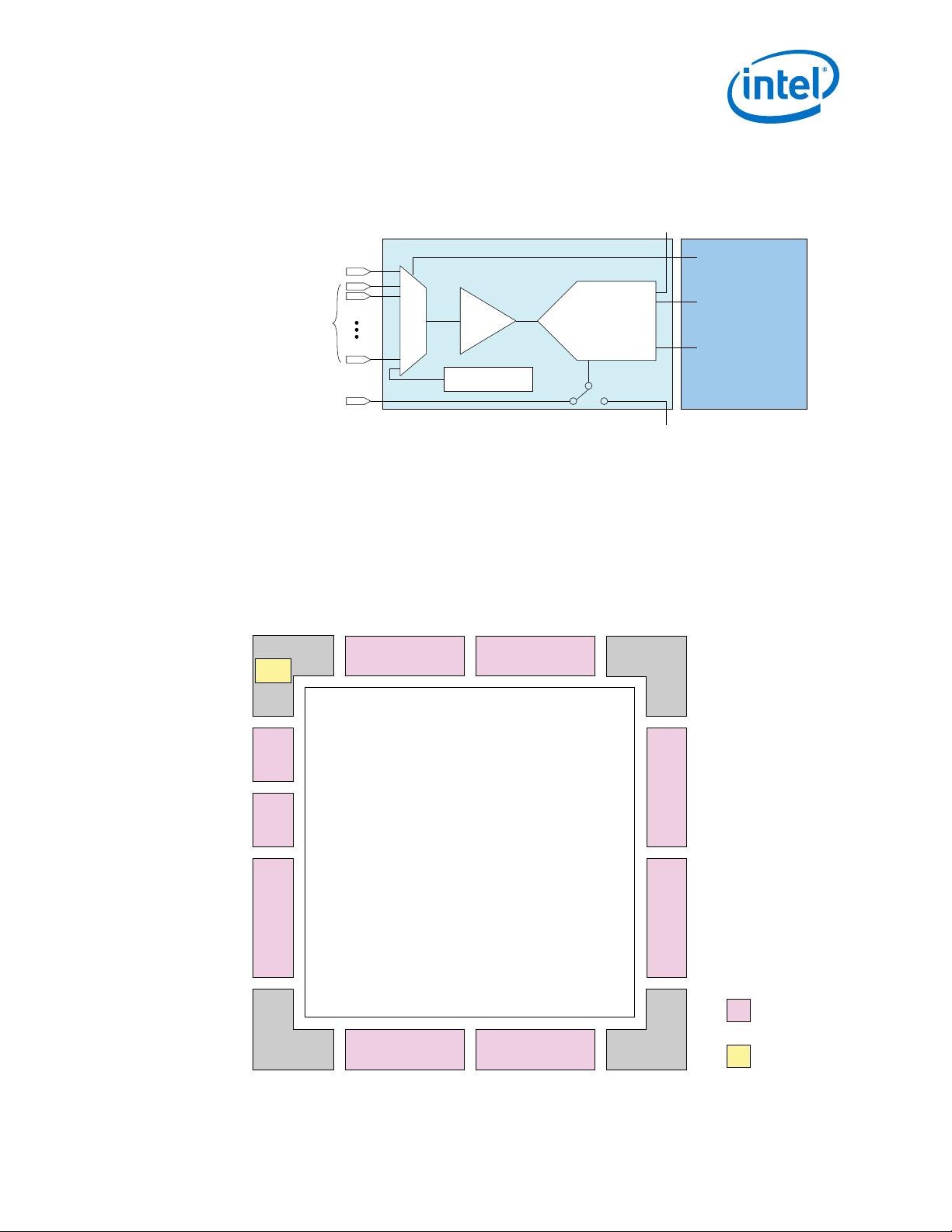

2. MAX 10 ADC的体系结构和特点:

- ADC硬核IP模块是集成在FPGA内部的专用模块,负责执行模数转换。

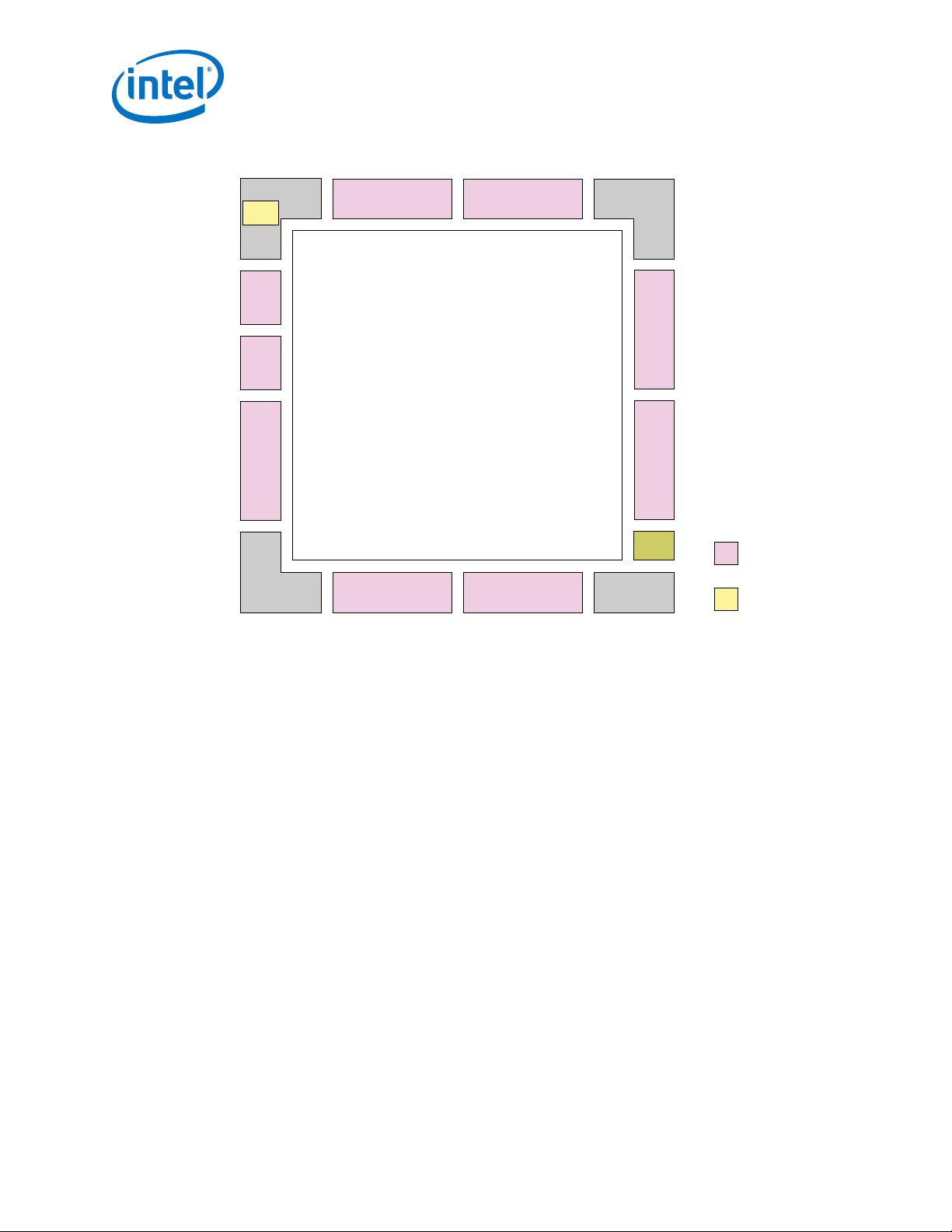

- ADC模块的位置可以在FPGA的不同区域,这取决于器件的具体型号。

- 单ADC或双ADC器件提供不同的通道数量,以满足不同应用的通道需求。

- 模拟输入引脚接收模拟信号,并将其转换为数字值。

- 预分频器用于调整ADC的采样速率。

- ADC时钟源是转换过程的关键,需要高精度以保证转换精度。

- 基准电压决定了ADC的量程,是确定数字输出范围的关键因素。

- 温度感应二极管用于监控ADC的工作温度,确保其在安全范围内工作。

- 定序器管理转换过程的时序,确保正确和有序的数据采集。

- ADC工具包提供了评估和测试ADC性能的工具。

3. 设计注意事项:

- 设计者必须关注接地平面的连接,以减少噪声和提高ADC性能。

- 电源引脚和ADC接地(REFGND)的电路板设计需要特别小心,以确保稳定的电源供应和低噪声环境。

- 模拟输入的电路板设计要求高阻抗路径和良好的信号完整性。

- ADC参考电压引脚的设计直接影响到转换精度,需要精确的布线和去耦。

4. 实现指南:

- 创建MAX 10 ADC设计涉及选择合适的ADC模块,定制IP内核参数,并配置必要的PLL(锁相环)以生成所需的时钟源。

- Altera Modular ADC IP内核允许用户自定义采样率、分辨率和其他特性。

- 完成设计后,需要进行综合、适配和编程,以在实际硬件上运行。

5. IP内核参考:

- Altera Modular ADC和Altera Modular Dual ADC IP内核提供了详细的设计参数和配置选项,帮助开发者根据特定应用优化性能。

这个用户指南为设计者提供了全面的指导,涵盖了从概念到实现的整个过程,是开发基于MAX 10 FPGA的模数转换系统的重要参考资料。

249 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

lixiaoxiang0404

- 粉丝: 0

最新资源

- 基于Java的小区水电费管理系统开发

- WinSCP:高效安全的SSH文件传输软件

- C# Winform中DataGridView合并单元格技巧分享

- 神舟优雅笔记本USB3.0驱动程序下载

- 掌握二分查找:四种变型的实现与应用

- 前端实践心得:HTML编码技巧分享

- 全面软件开发文档实例指南

- 专业API构建高效天气预报网站插件源码

- MySQL数据库安装包压缩文件解压即用

- CnWizards 1.0.1.665版本Delphi插件稳定性测试报告

- Simulink下BCH编码与解码仿真对比分析

- Linux字符设备驱动基础操作实现概述

- NFT项目探索:nftproject的创新与发展

- 2003分析工具库:Excle表格数据线性分析解决方案

- artDialog 4.1.6:实用的jqury和js网页弹出层控件

- TransModeler在城市交通规划管理中的应用详解