FPGA实现的高精度频率计设计与分析

需积分: 13 104 浏览量

更新于2024-07-23

收藏 157KB DOC 举报

"FPGA频率计是利用VHDL在FPGA上编程实现的一种高精度、等精度的数字频率计,它可以测量信号的频率、周期和占空比,且精度不受被测信号频率变化的影响。设计中包括前端的整形电路、FPGA内部的逻辑设计以及软件程序配合,以实现对任意信号的频率测量。"

本文主要围绕基于FPGA的等精度频率计设计展开,详细介绍了设计思路、单元电路设计、软件开发和系统测试过程。以下是对各章节的详细阐述:

第一章 总体设计

在这一章中,作者讨论了传统的频率计存在的问题,即测量精度随着被测信号频率降低而下降。等精度频率计则解决了这个问题,它在整个频率范围内都能保持恒定的测量精度。在方案选择上,作者对比了两种方法:一是采用数字逻辑电路直接用IC拼凑实现,这种方法简单但稳定性、精度和功耗都不理想;二是采用可编程逻辑器件,如CPLD或FPGA,通过EDA软件进行编程,这种方法虽然复杂,但可以实现更高的集成度和定制化,从而提高性能。

第二章 单元电路设计

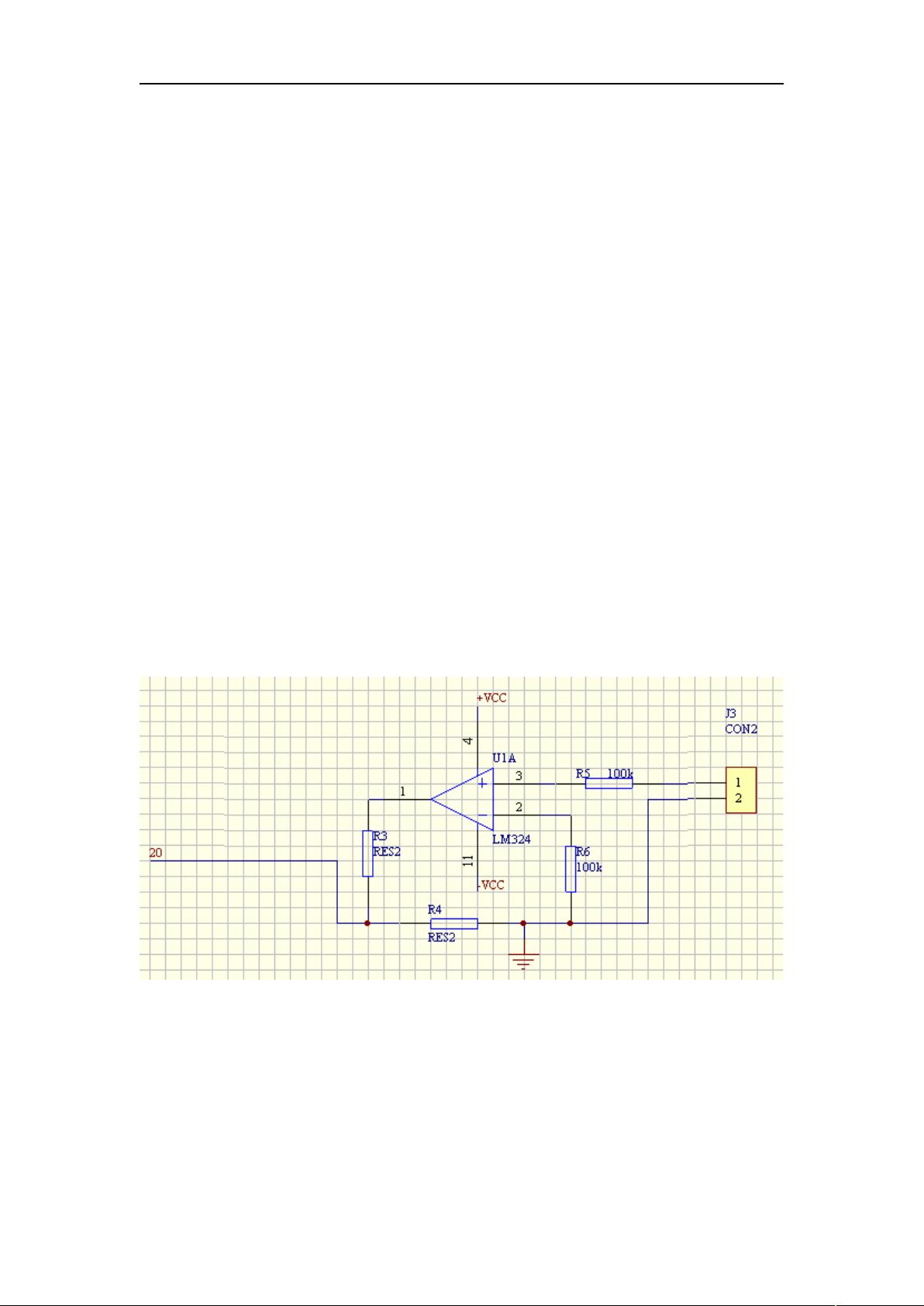

这部分详细介绍了频率计的组成部分,包括前端整形电路。整形电路的作用是将输入信号转换为适合后续处理的脉冲形式,以确保测量的准确性。此外,可能还涉及到分频器、计数器、比较器等核心单元的设计,这些电路共同作用于信号的频率、周期和占空比测量。

第三章 软件设计

在这一阶段,主要涉及的是使用VHDL语言编写FPGA内部逻辑的程序。VHDL是一种超高速硬件描述语言,用于描述数字系统的结构和行为。软件设计部分可能包括时序控制逻辑的描述、数据处理算法的实现以及与外部接口的通信协议等。

第四章 系统测试

系统测试是验证频率计功能是否符合预期的关键环节。作者可能会介绍如何设置测试信号,以及如何通过数据分析验证频率计的测量精度、稳定性和响应速度。测试结果将用来评估设计的有效性和优化改进。

第五章 结论及参考文献

这部分总结了整个设计的过程和成果,指出FPGA频率计的优势,并可能讨论了未来改进的方向或者可能遇到的技术挑战。同时,引用的相关文献为读者提供了更深入研究的起点。

第六章 附录

附录通常包含详细的设计图纸、代码清单、实验数据等辅助资料,供读者进一步理解设计细节。

FPGA频率计通过VHDL编程和FPGA的灵活性实现了高精度的频率测量,其设计考虑了硬件电路和软件程序的协同工作,旨在克服传统频率计的局限性,提供更广泛的应用范围和更高的测量可靠性。

203 浏览量

535 浏览量

104 浏览量

278 浏览量

168 浏览量

126 浏览量

305 浏览量

骅仔

- 粉丝: 0

最新资源

- Qt智能停车场系统的设计与实现

- 谭浩强C语言程序设计案例集

- Objective-C 实现即时Base64编码的MTBase64InputStream

- 基于SSM框架的零食商城系统毕业设计

- 大华秤串口通信协议详解

- 隐身侠:保护电脑私密信息的最佳选择

- 分享TR069协议的简易实现源码

- Java打字练习软件源码及文档:速度与准确率统计

- React项目实战:freeCodeCamp前端计算器解决方案

- 构建完美联系页面:HTML与CSS的结合技巧

- 最小的PHP实时控制台工具 - live-console

- 无聊桌面v2.1.0:高效桌面管理与快捷启动工具

- HTML图形化教程核心概念解析

- CNN-F-Protein-Docking: 结合反馈机制提升蛋白质对接准确性

- Delphi源码合集:包含管理系统与工具开发

- STM32 SPI从机通信的实现与配置