该文章版权归 smarteebit 所有。若有疑问,请联系 songmin2@sohu.com

Smarteebit Page 4 of 17

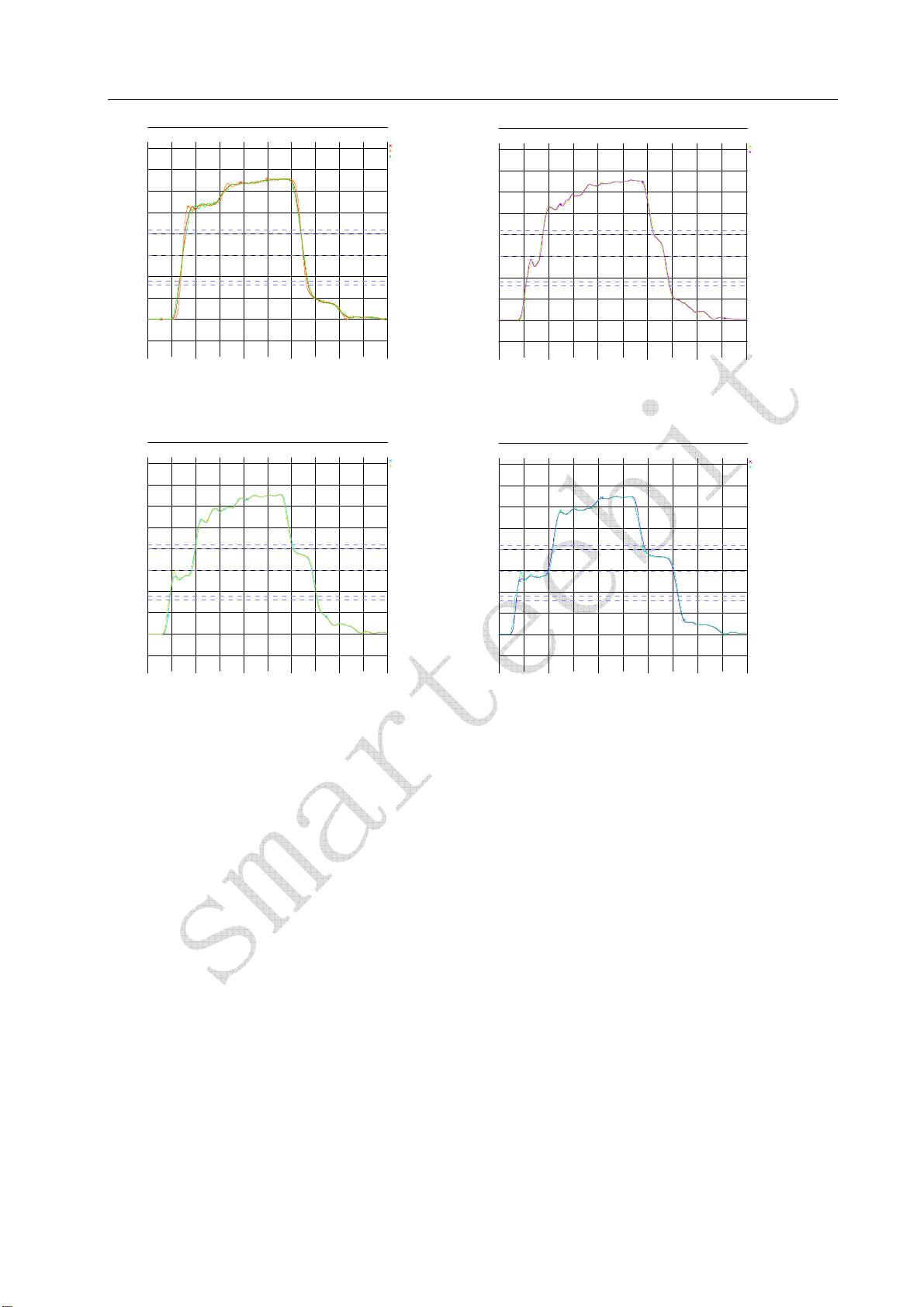

(a) (b)

(c) (d)

图 6 链型拓扑的仿真波形

可以看到,末端的波形(a)是最好的,由远及近(b)-> (c) ->(d),信号沿的非单调性问题开始出现,

越靠近驱动端,非单调性越严重。实测波形与仿真基本接近,这里就不再贴出来了。像(b)、(c)、(d)

这样的信号质量,如果是数据,只要能保证不影响时序,倒也无妨,但如果是沿有效的时钟,则是不能

接受的。该实例证明,串行匹配用于链型拓扑时,只能保证末端负载的波形。从理论上理解:源端匹配

消灭的是二次反射,当信号行波的一次反射从末端往回走的途中,与驱动信号叠加,便有了这样的波形。

有兴趣钻研的朋友可以看看Howard W. Johnson的“HIGH-SPEED DIGITAL DESIGN: A Handbook of

Black Magic”,里面的“Source Terminators”一节中有类似的阐述。

关于信号的非单调性带来的问题,后文将有另外的案例详细说明。

1.2 案例:通过修改驱动电流的方法改善过冲

每个网络拓扑都有自己的等效电容、等效电阻和等效电感,这几个参数一起,构成了网络上的一套

充放电电路,驱动端的电流越大,这套电路的充/放电时间就越快,由此产生的信号沿就越陡;反之,

信号沿越缓。这就是降低驱动电流能够使信号沿变缓的原理。

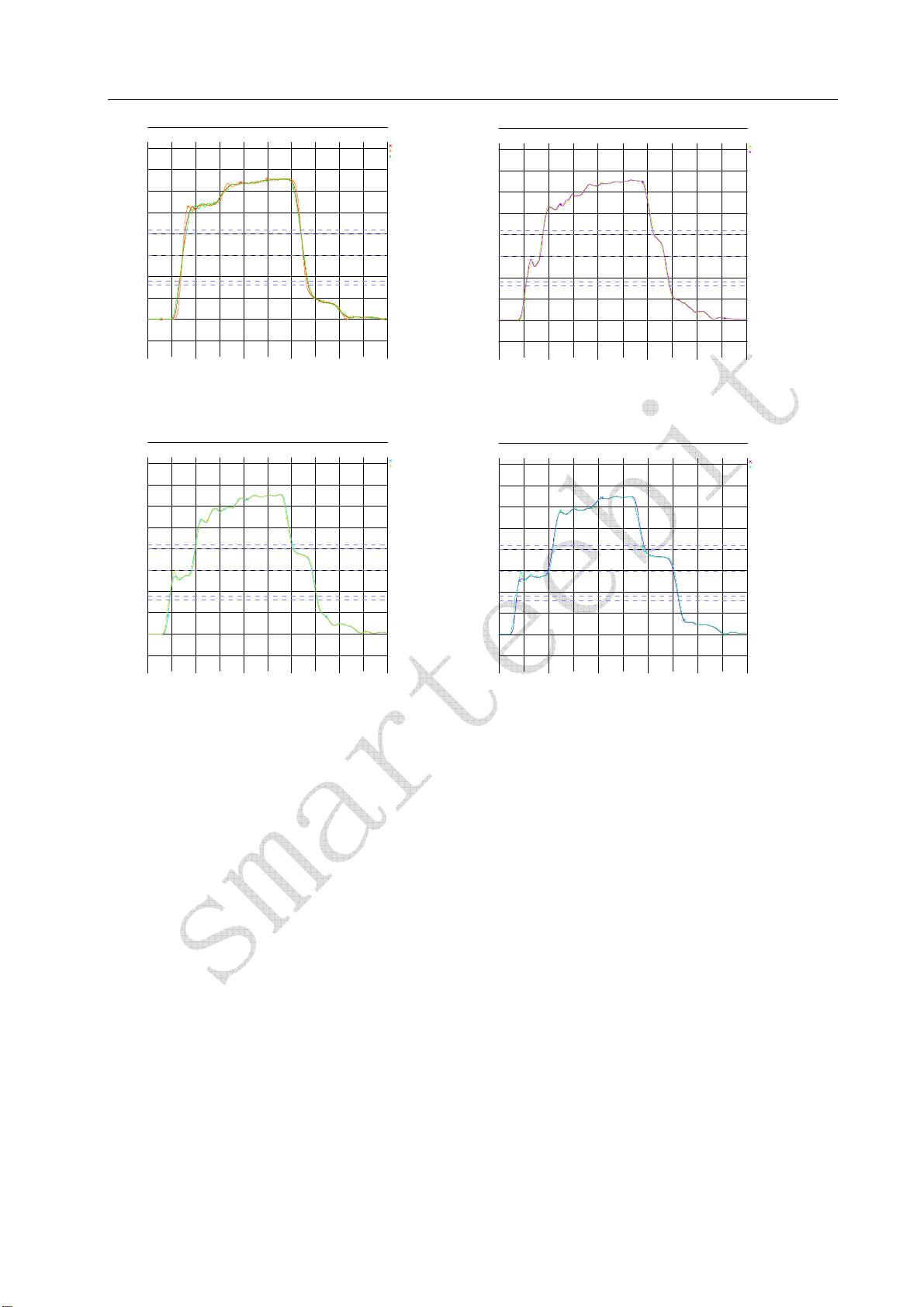

下面两个图是在不同管脚驱动能力配置下,对同一网络拓扑的同一测试点的实测结果,驱动端为

Altera 的 MAXII 器件的 LVTTL33 输出,测试点在接收端管脚。可以看到,当输出驱动能力为 8mA 时,

接收端的过冲比 16mA 时明显减小。

OSCILLOSCOPE

Design file: SAT7_682D.HYP Designer: songmin

HyperLynx V7.7

Date: Thursday Dec. 17, 2009 Time: 18:06:59

Net name: P_SCK

Show Latest Waveform = YES

-500.0

0.00

500.0

1000.0

1500.0

2000.0

2500.0

3000.0

3500.0

4000.0

0.00 4.000 8.000 12.000 16.000

Time (ns)

V

o

l

t

a

g

e

-

m

V

-

V [UA2.13 (at die)]

V [U30.11 (at die)]

OSCILLOSCOPE

Design file: SAT7_682D.HYP Designer: songmin

HyperLynx V7.7

Date: Thursday Dec. 17, 2009 Time: 18:06:14

Net name: P_SCK

Show Latest Waveform = YES

-500.0

0.00

500.0

1000.0

1500.0

2000.0

2500.0

3000.0

3500.0

4000.0

0.00 4.000 8.000 12.000 16.000

Time (ns)

V

o

l

t

a

g

e

-

m

V

-

V [UB2.13 (at die)]

V [U31.11 (at die)]

OSCILLOSCOPE

Design file: SAT7_682D.HYP Designer: songmin

HyperLynx V7.7

Date: Thursday Dec. 17, 2009 Time: 18:05:31

Net name: P_SCK

Show Latest Waveform = YES

-500.0

0.00

500.0

1000.0

1500.0

2000.0

2500.0

3000.0

3500.0

4000.0

0.00 4.000 8.000 12.000 16.000

Time (ns)

V

o

l

t

a

g

e

-

m

V

-

V [UC2.13 (at die)]

V [U32.11 (at die)]

OSCILLOSCOPE

Design file: SAT7_682D.HYP Designer: songmin

HyperLynx V7.7

Date: Thursday Dec. 17, 2009 Time: 18:04:48

Net name: P_SCK

Show Latest Waveform = YES

-500.0

0.00

500.0

1000.0

1500.0

2000.0

2500.0

3000.0

3500.0

4000.0

0.00 4.000 8.000 12.000 16.000

Time (ns)

V

o

l

t

a

g

e

-

m

V

-

V [UD2.13 (at die)]

V [U74.11 (at die)]

V [U70.11 (at die)]