Quartus_II_11.0工程创建与ModelSim仿真教程

需积分: 10 190 浏览量

更新于2024-09-11

收藏 871KB DOC 举报

"这篇文档详细介绍了如何使用Quartus_II_11.0软件创建新工程,并结合ModelSim进行功能仿真。主要内容包括新建工程、选择器件、设置仿真工具、编写代码、创建测试平台以及运行仿真等步骤。"

在电子设计自动化(Electronic Design Automation, EDA)领域,Altera的Quartus_II_11.0是一个广泛使用的FPGA(Field-Programmable Gate Array)设计工具。这个版本提供了强大的设计环境,支持从项目创建到硬件实现的全过程。以下是对使用Quartus_II_11.0进行功能仿真的详细步骤:

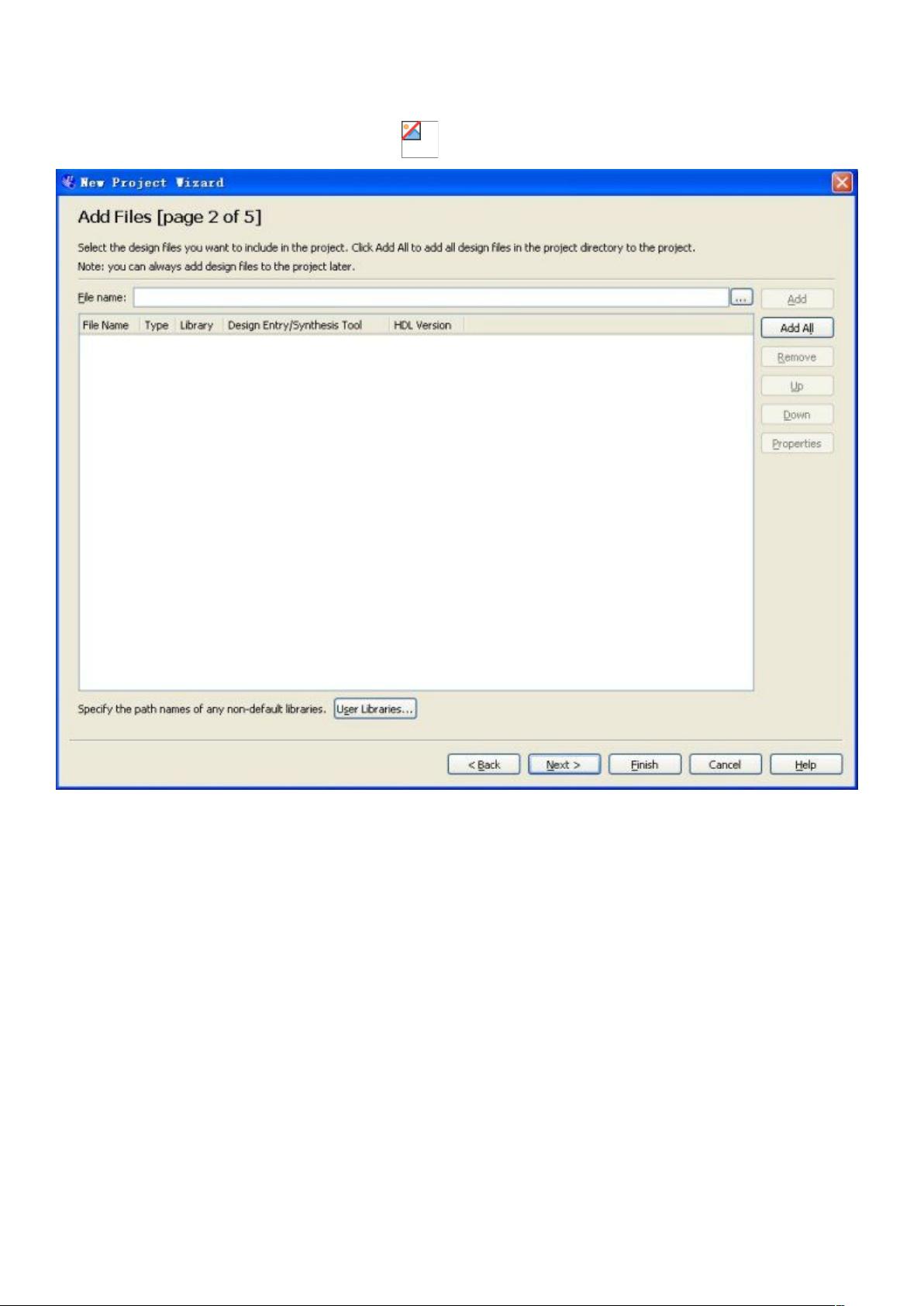

首先,新建工程:用户需要通过界面引导,依次设置工程名称、保存路径,并添加已存在的设计文件。如果还没有设计文件,可以跳过此步骤直接进入下一环节。

接着,选择器件:在工程配置中,用户可以选择适合的FPGA器件。可以允许软件自动选择,或者根据项目需求手动指定。选择正确的器件是确保设计能够成功运行在目标硬件上的关键。

然后,设置仿真工具:在设置界面中,用户可以选择仿真软件,这里是ModelSim-Altera。ModelSim是一款强大的行为级和门级仿真器,常用于验证FPGA设计的功能正确性。

在代码编写阶段,用户需要使用Verilog HDL(Hardware Description Language)来描述电路逻辑。模块名应与保存的文件名保持一致,否则编译时会出错。完成代码编写后,点击编译以检查语法错误和逻辑问题。

通过编译后,将显示编译报告,报告会列出项目的各个部分及其状态,勾选表示该部分已通过编译。

为了验证设计的功能,需要编写测试平台(Testbench)。测试平台通常也是用Verilog HDL编写,但文件后缀需改为.vt。在设置中,选择ModelSim作为仿真工具,设定输出网表格式为Verilog HDL,并设置时间单位。

接下来,使用TestBenchTemplateWriter生成测试平台模板,然后将测试文件添加到工程中。确保TestbenchName和Toplevelmoduleintestbench与实际测试平台模块名称匹配,并将测试文件添加到Testbench files列表。

最后,完成所有设置后再次编译工程,然后通过Tools菜单运行EDASimulationTool,选择EDARTL Simulation启动Modelsim进行功能仿真。在Modelsim中,用户可以观察波形,验证设计是否按照预期工作。

通过以上步骤,用户可以成功地在Quartus_II_11.0环境中完成一个FPGA设计的功能仿真,为后续的硬件实现打下基础。这个过程对于理解和调试复杂的数字系统设计至关重要。

2013-04-12 上传

2022-09-23 上传

2022-09-21 上传

2014-06-26 上传

2012-03-26 上传

2013-05-07 上传

2022-09-24 上传

2012-08-25 上传

2014-05-27 上传

shixiaoweiwin

- 粉丝: 5

- 资源: 12

最新资源

- 黑板风格计算机毕业答辩PPT模板下载

- CodeSandbox实现ListView快速创建指南

- Node.js脚本实现WXR文件到Postgres数据库帖子导入

- 清新简约创意三角毕业论文答辩PPT模板

- DISCORD-JS-CRUD:提升 Discord 机器人开发体验

- Node.js v4.3.2版本Linux ARM64平台运行时环境发布

- SQLight:C++11编写的轻量级MySQL客户端

- 计算机专业毕业论文答辩PPT模板

- Wireshark网络抓包工具的使用与数据包解析

- Wild Match Map: JavaScript中实现通配符映射与事件绑定

- 毕业答辩利器:蝶恋花毕业设计PPT模板

- Node.js深度解析:高性能Web服务器与实时应用构建

- 掌握深度图技术:游戏开发中的绚丽应用案例

- Dart语言的HTTP扩展包功能详解

- MoonMaker: 投资组合加固神器,助力$GME投资者登月

- 计算机毕业设计答辩PPT模板下载