DDR3内存控制器配置指南:以P1020 CPU和H5TQ1G63DFR为例

"DDR3内存控制器参数设计是一个关键任务,涉及到CPU、内存芯片以及硬件平台的协同工作。本文档提供了一个具体的实例,以PowerPC P1020 CPU和DDR3内存芯片H5TQ1G63DFR H9C为例,详细解释了内存控制器的参数配置。在进行内存控制器设计时,需要根据实际硬件配置和芯片特性来调整参数,因为这些参数会因硬件板的不同、芯片批次而有所差异,不能简单地复制他人的设置。"

DDR3内存参数设计中,颗粒型号H5TQ1G63DFR H9C是一个1Gbit的内存颗粒,由两片组成,总容量为2Gbit或256MB。该芯片支持多种可编程的CAS延迟(CAS latency)从6到14,附加延迟(Additive Latency)0、CL-1和CL-2,以及CAS写入延迟(CWL)5到10。它还具备4/8位突发长度(Burst Length),支持 nibble sequential 和 interleave模式,并且在数字消费应用中支持4位突发长度(BL=4,tCCD=2CLK)。此外,该芯片具备可编程ZQ校准功能,8个银行,自动自刷新,动态On-Die终端和8位预取功能。

DDR3内存控制器的关键参数包括CAS延迟(CL)、行地址至列地址延迟(tRCD)、行预充电时间(tRP)、地址至激活时间(tAA)、行周期时间(tRC)和行激活时间(tRAS)。在本例中,使用的是DDR3-1066(533MHz MCK频率,降频使用),CL=7的配置。通过示波器测量,得到时钟周期tCK为1.875ns。根据这些参数,可以计算出其他相关的时间值:

- tRCD = 13.125ns = 7tCK

- tRP = 13.125ns = 7tCK

- tAA = 13.125ns = 7tCK

- tRC > 50.625ns,可以取55ns = 29.3tCK,建议取30tCK

- tRAS > 37.5ns,可以取50ns = 26.6tCK,建议取27tCK

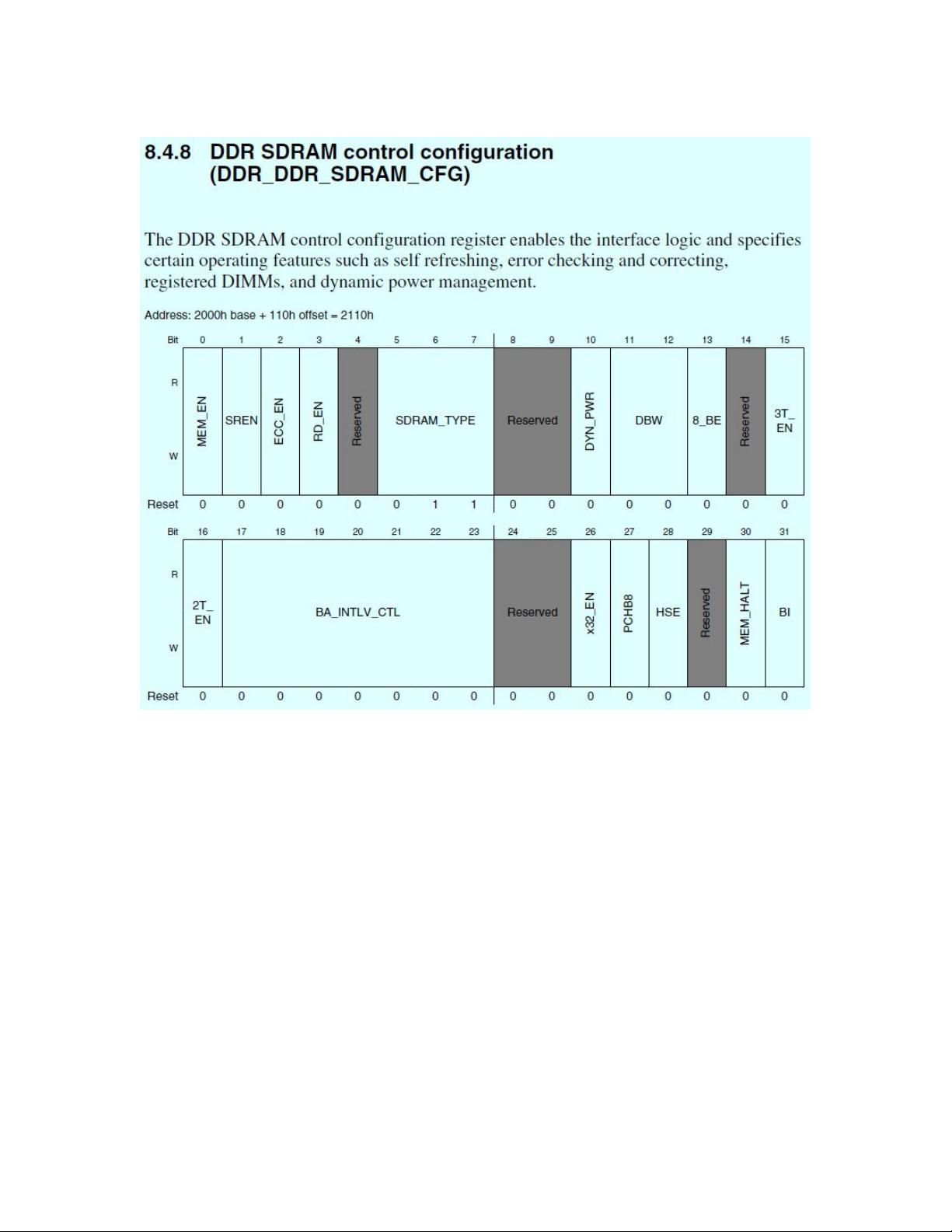

DDR_SDRAM_CF参数设置是内存控制器配置的一部分,可能包括但不限于上述提到的CAS延迟、预充电时间等。在设计过程中,需要确保这些参数符合内存芯片的数据手册推荐值,以确保系统稳定运行和性能优化。同时,要注意DDR3内存的时序特性,如tRAS和tRC,它们直接影响内存的读写速度和效率。

DDR3内存控制器参数设计是一个涉及多方面因素的复杂过程,需要对硬件平台、内存芯片特性和内存工作原理有深入理解。通过实例学习和参考,初学者可以更好地掌握这一技能,为新开发的单板提供可靠的内存管理方案。

相关推荐

sincostan

- 粉丝: 3

最新资源

- 支付宝订单监控免签工具:实时监控与信息通知

- 一键永久删除QQ空间说说的绿色软件

- Appleseeds训练营第4周JavaScript练习

- 免费HTML转CHM工具:将网页文档化简成章

- 奇热剧集站SEO优化模板下载

- Python xlrd库:实用指南与Excel文件读取

- Genegraph:通过GraphQL API使用Apache Jena展示RDF基因数据

- CRRedist2008与CRRedist2005压缩包文件对比分析

- SDB交流伺服驱动系统选型指南与性能解析

- Android平台简易PDF阅读器的实现与应用

- Mybatis实现数据库物理分页的插件源码解析

- Docker Swarm实例解析与操作指南

- iOS平台GTMBase64文件的使用及解密

- 实现jQuery自定义右键菜单的代码示例

- PDF处理必备:掌握pdfbox与fontbox jar包

- Java推箱子游戏完整源代码分享

已收录资源合集

已收录资源合集