理解Makefile:规则、命令与自动化构建

154 浏览量

更新于2024-08-03

收藏 559KB PDF 举报

"这篇文档详细介绍了Linux系统中Makefile规则的使用,重点在于如何编写和理解Makefile的基本结构和命令。Makefile是用于自动化构建和管理项目的关键文件,尤其在编程过程中,它可以帮助开发者高效地编译、链接及管理源代码文件。"

在Linux环境中,Makefile是一个至关重要的工具,它定义了一系列的规则来指导`make`命令如何构建、编译和链接程序。Makefile通常包含目标(Target)、依赖文件(Dependencies)和构建命令(Commands)三部分。目标是需要生成的文件,比如可执行程序或库;依赖文件是生成目标所需的源文件或其他中间文件;而命令则描述了如何从依赖文件生成目标文件。

在Makefile中,每条规则的格式通常是:

```makefile

<Target>: <Dependency1> <Dependency2> ... <DependencyN>

<Command1>

<Command2>

...

```

这里的命令必须以制表符(TAB)开头,这是`make`识别命令的关键。如果目标文件比其依赖文件旧或者依赖文件被修改过,`make`就会执行相应的命令来更新目标。

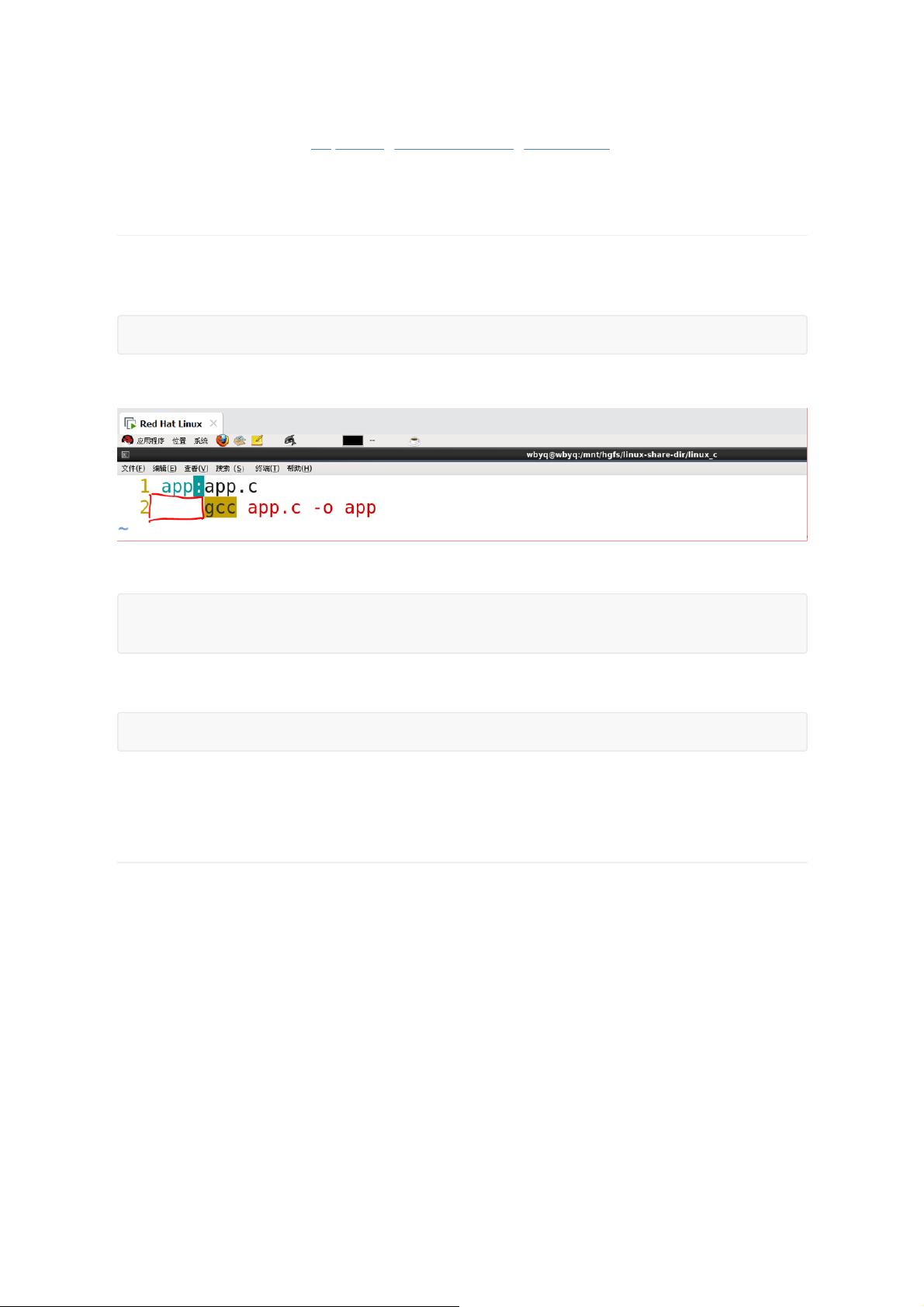

例如,一个简单的C程序Makefile可能包含以下规则:

```makefile

app: app.c

gcc -o app app.c

```

这个规则表示,如果`app.c`被修改,那么`make`将运行`gcc`命令生成`app`可执行文件。

Makefile还支持一些自动化变量,比如`$^`代表所有依赖文件,`$<`代表第一个依赖文件。这使得Makefile更加简洁和灵活,比如:

```makefile

app: app.c util.o

gcc -o $@ $^

```

在这个例子中,`$@`代表目标,`$^`包含了所有的依赖文件,这样就可以避免手动列出所有依赖文件。

在执行Makefile时,如果没有指定目标,`make`会默认构建第一个目标。若要指定特定目标,可以在`make`命令后跟上目标名,如`make app2`。此外,使用`-s`或在命令前加`@`可以抑制命令的显示,使构建过程更整洁。

示例1展示了如何为一个简单的工程编写显式规则的Makefile,每个目标及其依赖和构建命令都会明确列出。而示例2则利用自动化编译符号,如`$^`和`$<`,来简化Makefile的编写,使得当源文件增加或减少时,无需修改太多内容。

Makefile是Linux开发中的核心组件,通过合理地编写Makefile,开发者可以大大提高工作效率,实现程序构建的自动化,无论是在小型项目还是大型项目中,都是不可或缺的工具。

2023-07-11 上传

2021-12-01 上传

2021-02-17 上传

2023-07-29 上传

2023-10-21 上传

2023-05-22 上传

2024-10-16 上传

2023-05-26 上传

2023-05-24 上传

DS小龙哥

- 粉丝: 4w+

- 资源: 907

最新资源

- Raspberry Pi OpenCL驱动程序安装与QEMU仿真指南

- Apache RocketMQ Go客户端:全面支持与消息处理功能

- WStage平台:无线传感器网络阶段数据交互技术

- 基于Java SpringBoot和微信小程序的ssm智能仓储系统开发

- CorrectMe项目:自动更正与建议API的开发与应用

- IdeaBiz请求处理程序JAVA:自动化API调用与令牌管理

- 墨西哥面包店研讨会:介绍关键业绩指标(KPI)与评估标准

- 2014年Android音乐播放器源码学习分享

- CleverRecyclerView扩展库:滑动效果与特性增强

- 利用Python和SURF特征识别斑点猫图像

- Wurpr开源PHP MySQL包装器:安全易用且高效

- Scratch少儿编程:Kanon妹系闹钟音效素材包

- 食品分享社交应用的开发教程与功能介绍

- Cookies by lfj.io: 浏览数据智能管理与同步工具

- 掌握SSH框架与SpringMVC Hibernate集成教程

- C语言实现FFT算法及互相关性能优化指南