FPGA时序分析与设计实战指南

"FPGA时序分析教程,涵盖了时序基础、时序分析、时序优化、时序约束、同步设计、跨时钟域等内容,旨在解决FPGA设计中的稳定性、速度、约束等问题,并教授如何进行高效设计。"

在FPGA设计中,时序分析是至关重要的一个环节,它直接影响到设计的性能、稳定性和可实现性。时序分析主要是为了确保数据能在正确的时间被正确的采样,避免因建立时间不足或保持时间过短导致的数据错误。以下是时序分析的关键知识点:

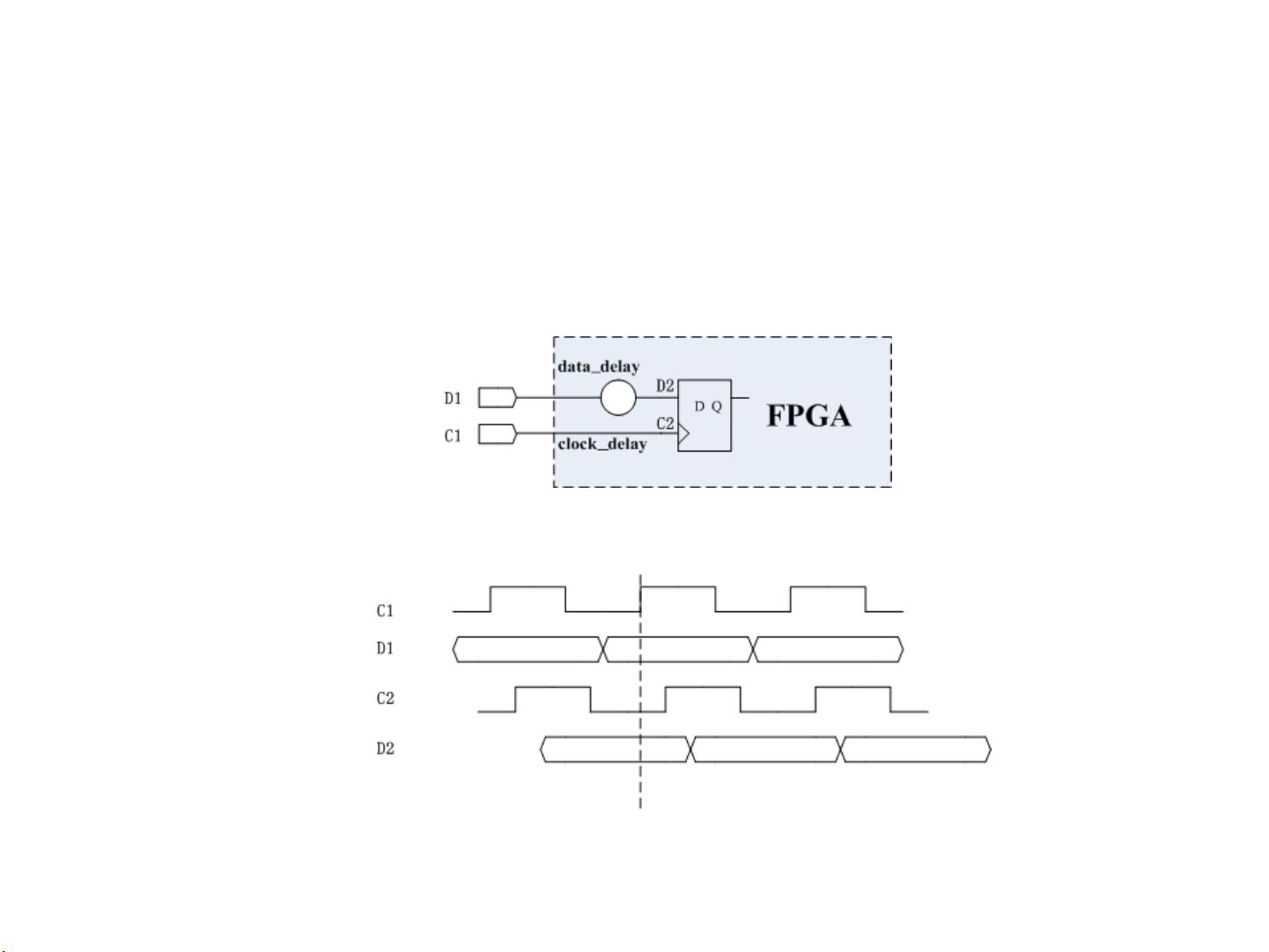

1. **时序基础**:时序分析主要关注的是数据传输和处理的时间关系,包括接口时序和内部时序。接口时序涉及到输入输出信号与时钟之间的关系,而内部时序则关注逻辑单元之间的延迟。数字域上的采样模型通常分为最简模型、内部模型、接口模型和全模型,这些模型帮助我们理解信号在物理层面上是如何转换和传输的。

2. **时序分析**:时序分析主要关注三类路径:时钟路径、数据路径和异步路径。时钟路径是时钟信号从源头到目的地的路径;数据路径则是数据在系统中传递的路径;异步路径则是不受主时钟控制的信号路径。同步路径分析关注时钟和数据路径,而异步路径分析则关注时钟与异步信号的交互。

3. **时序模型**:时序模型通常包括发射沿和锁存沿的概念。发射沿指的是数据从源寄存器传出的时钟沿,锁存沿则是数据被目标寄存器接收的时钟沿。设计工具通常会保证从发射沿到锁存沿的延迟不超过一个时钟周期(多周期路径除外)。

4. **建立时间与保持时间**:建立时间是指数据必须在时钟沿到来前保持稳定的时间,保持时间则是时钟沿到来后数据必须保持稳定的时间。这两个时间的满足是保证正确采样的必要条件,如果违反,则可能导致采样错误。

5. **数据延时时间**:数据延时时间是数据从源到目标的总延迟,包括时钟路径的延迟(Tclk1)、时钟偏移(Tco)和数据路径延迟(Tda)。优化这个时间对于提高设计速度至关重要。

6. **时序优化**:通过优化逻辑设计、减少路径延迟、合理分配资源等方式来缩短数据传输时间,提升系统性能。

7. **时序约束**:在设计过程中,设置合适的时序约束能确保设计能够满足特定的速度要求。这包括对时钟路径、数据路径和异步路径的约束,以及对建立时间和保持时间的要求。

8. **同步设计**:同步设计是遵循同一时钟域内的所有操作,目的是减少由于异步信号引起的不确定性和潜在的毛刺。同步设计原则包括使用同步复位、避免时钟域间的非法数据传输等。

9. **跨时钟域**:当需要在不同时钟域之间传递数据时,需要特别注意时序问题,如 metastability(亚稳态)问题。解决办法通常包括使用同步器(如双稳态触发器)来确保数据在两个时钟域间正确传输。

通过深入理解和熟练应用以上知识点,设计师可以有效地进行FPGA时序分析,从而实现高效、稳定、快速的FPGA设计。

242 浏览量

147 浏览量

202 浏览量

137 浏览量

2009-04-11 上传

debei8

- 粉丝: 0

- 资源: 4

最新资源

- 高质量c++ c编程指南

- WPF技术白皮书 下一代互联网主流开发技术

- 整合Flex和Java--配置篇.pdf

- unix 编程艺术指导

- 词法分析器的设计与实现

- TD7.6管理员指南

- ACE Programming Guide

- 手机游戏门户网站建设方案

- 搜索引擎技术手工索引

- 衡水信息港投资计划书 网站建设方案

- 地方门户网站策划书(转载)

- [计算机科学经典著作].SAMS.-.Tricks.Of.The.Windows.Game.Programming.Gurus.-.Fundamentals.Of.2D.And.3D.Game.Programming.[eMule.ppcn.net].pdf

- Embedded_Linux_on_ARM.pdf

- SQL语言艺术(英文版)

- Windows File Systems _FAT16, FAT32, NTFS_.pdf

- C Programming Language 2nd Edition(K & R).pdf