异步FIFO时序设计原理与解决二进制计数器误差

异步FIFO(First-In-First-Out,简称FIFO)是一种广泛应用于多时钟系统中的数据缓冲技术,尤其是在大规模集成电路(ASIC)和现场可编程门阵列(FPGA)设计中。它解决了不同时钟域间数据传输的时序问题,通过提供一个稳定的缓冲区,确保数据按照先进先出的原则在不同时钟周期之间顺畅流动。

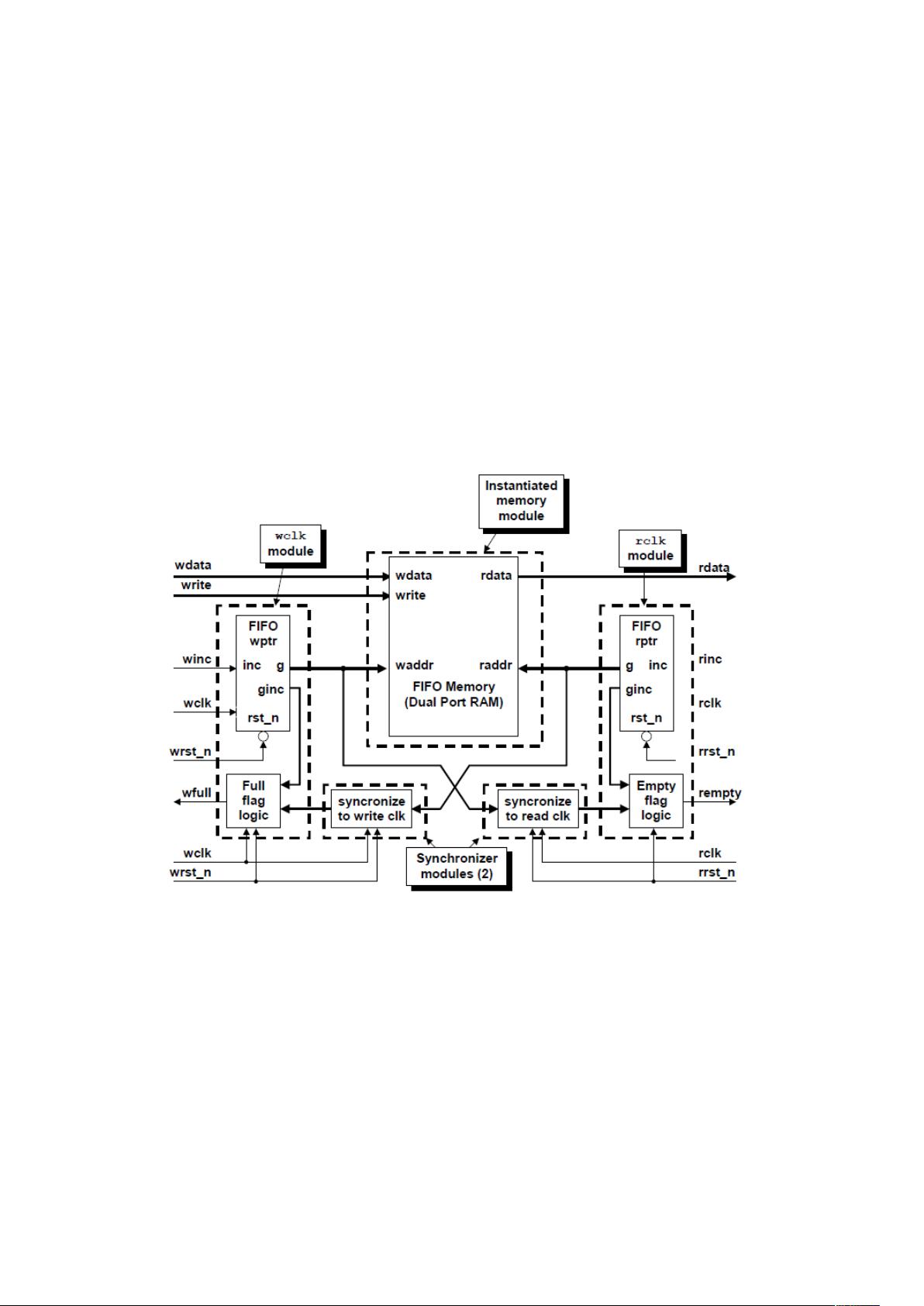

设计异步FIFO的关键在于两个核心模块:同步模块和双端口存储RAM。同步模块包括synchronizetowrite和synchronizetoread,它们分别负责将一个时钟域的读写指针同步到另一个时钟域,通过比较读写指针的位置来判断FIFO是否为空或已满。写指针wr_ptr和读指针rd_ptr的变化需经过复杂的逻辑处理,因为它们可能在不同时钟周期处于变化状态,这就需要用到二进制计数器来跟踪。

然而,二进制计数器在实现过程中存在挑战。由于读写指针在不同时钟域,且时钟相位可能不固定,可能导致读取到的数据在指针跳变时处于不确定状态,产生错误的结果。例如,如果rd_ptr在rd_clk上升沿到达寄存器时存在偏差,如图2.2.1所示,可能会经历多个临时状态,如3'b011到3'b100的过程中,通过递增操作会出现不期望的中间状态,如3'b111和3'b101。

解决这个问题的一个方法是采用延迟锁存器或者预分频机制来补偿时钟差异和路径延迟,确保在正确的时间点读取到稳定的数据。此外,设计者还需要仔细考虑时序约束,包括但不限于采样时间、保持时间和恢复时间,以防止竞态条件和数据丢失。

在异步FIFO设计中,还需要考虑其他细节,如错误检测和纠正机制、空闲状态的处理以及FIFO的初始化和清零。此外,由于FPGA和ASIC资源有限,设计师需要优化FIFO的大小、深度和读写速度,以平衡性能和资源消耗。

总结来说,异步FIFO的设计是一个精细的工程,它涉及到多个时钟同步、信号处理、时序分析以及硬件资源的有效利用。只有深入了解并妥善解决这些问题,才能在实际应用中实现高效、可靠的多时钟域数据传输。

点击了解资源详情

361 浏览量

231 浏览量

160 浏览量

101 浏览量

529 浏览量

506 浏览量

188 浏览量

2023-05-20 上传

peixiancsdn

- 粉丝: 0

最新资源

- Python大数据应用教程:基础教学课件

- Android事件分发库:对象池与接口回调实现指南

- C#开发的斗地主网络版游戏特色解析

- 微信小程序地图功能DEMO展示:高德API应用实例

- 构建游戏排行榜API:Azure Functions和Cosmos DB的结合

- 实时监控系统进程CPU占用率方法与源代码解析

- 企业商务谈判网站模板及技术源码资源合集

- 实现Webpack构建后自动上传至Amazon S3

- 简单JavaScript小计算器的制作教程

- ASP.NET中jQuery EasyUI应用与示例解析

- C语言实现AES与DES加密算法源码

- 开源项目实现复古游戏机控制器输入记录与回放

- 掌握Android与iOS异步绘制显示工具类开发

- JAVA入门基础与多线程聊天售票系统教程

- VB API实现串口通信的调试方法及源码解析

- 基于C#的仓库管理系统设计与数据库结构分析