Logisim电子钟系统设计-多功能数字钟实验

需积分: 0 45 浏览量

更新于2024-08-04

收藏 653KB DOCX 举报

"电子钟设计与实现"

在本次实验中,我们关注的是电子钟的系统设计,特别是多功能电子钟。实验的主角是CS1804课程的学生彭子晨,他将设计并验证一个具备多种功能的电子钟系统。实验的核心在于逻辑电路的设计,通过使用Logisim软件进行虚拟仿真,以确保设计符合预期。

实验的目标不仅是设计一个能够显示时、分、秒的电子钟,还要求它具备以下特点:

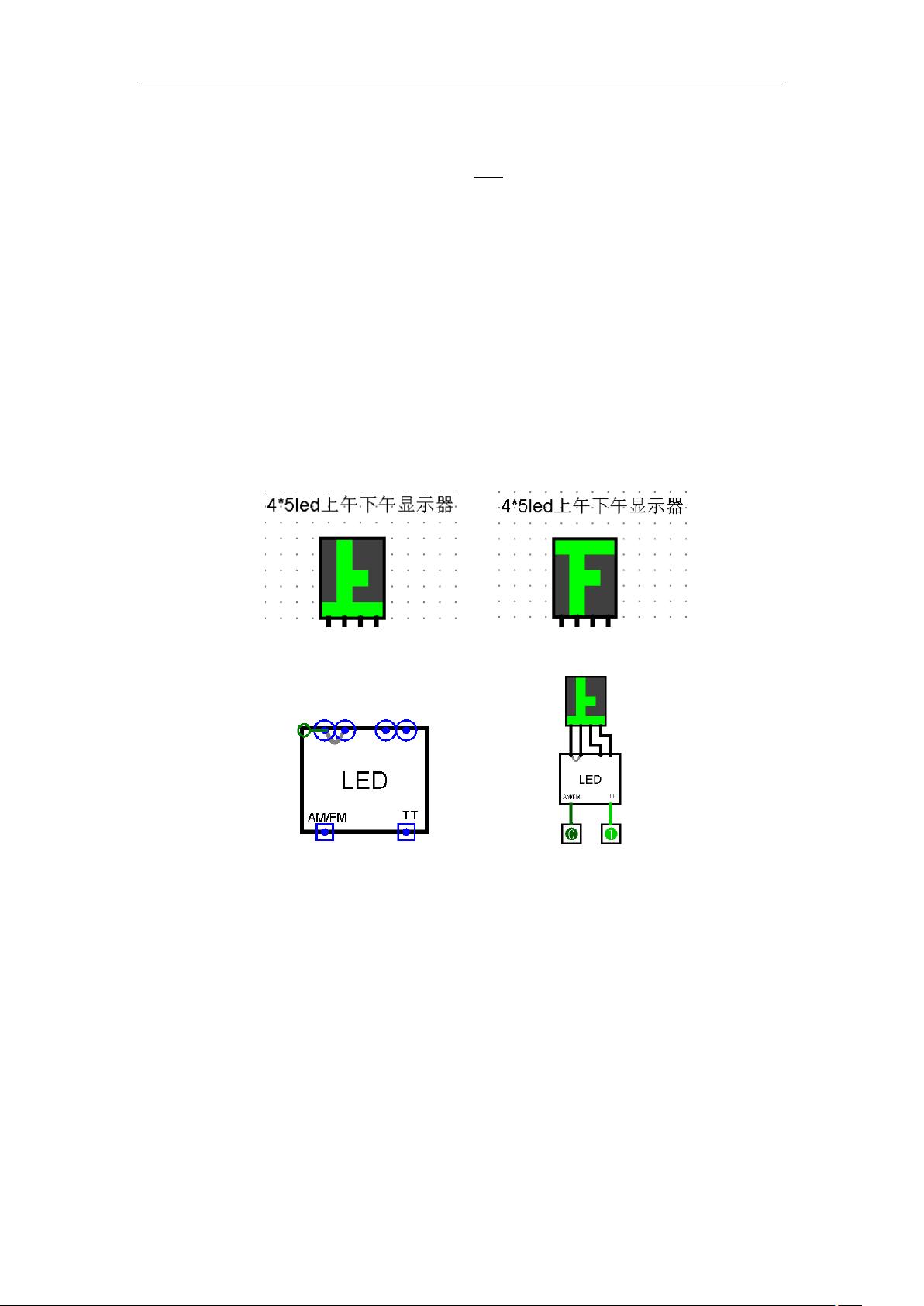

1. 时间显示模式切换:用户可以选择24小时制或12小时制(AM/PM)显示模式,以适应不同用户的偏好。

2. 整点报时功能:当到达整点时,电子钟会进行报时,报时前10秒开始,整点时结束,增强用户体验。

3. 计时校准:允许用户独立地校准小时和分钟,校准分钟值时不会影响小时值,保证了时间的精确性。

4. 闹钟功能:电子钟应能设置闹钟,当设定时间到达时,提醒用户10秒,提供定时提醒服务。

为了实现这些功能,实验要求学生使用Logisim2.7.1软件进行电路设计。实验设备包括一套Logisim软件和一台微型计算机。总共有16个课时,分为课内和课外两部分,旨在让学生掌握小型电路系统的设计、仿真和调试技巧,以及电路模块封装的方法。

在设计过程中,学生需要设计一个六十进制计数器,用于精确地计时。这个计数器需要具备以下特性:

- 六十进制计数器封装:计数器应包含一个累加计数脉冲输入CPU、一个累减计数脉冲输入CPD、清零输入信号Clr和一个计数值校准输入控制信号Adj。

- 输出与控制:输出为八个计数器状态,进位输出信号;Adj为1时,通过CPU和CPD进行加减调整;Adj为0时,计数器按CPU脉冲累加计数,满60产生进位信号;Clr为1时,计数器清零;输出为两位8421码的二进制数。

- 测试电路:设计完成后,需要构建测试电路,外接16进制显示器,并将CPU和CPD连接至按钮。

接下来,学生需要基于上述六十进制计数器,设计一个能校准计数值的十二进制或二十四进制计数器。这要求他们灵活应用已有的六十进制计数器,实现更复杂的计时功能。

整个实验通过模拟实际操作,使学生不仅理解数字电子钟的工作原理,还能锻炼他们的逻辑思维和问题解决能力,从而提升在电子工程领域的专业技能。通过这样的实践,学生们将更好地掌握数字电路设计和软件仿真的综合运用。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

242 浏览量

色空空色

- 粉丝: 981

- 资源: 330

最新资源

- Elasticsearch核心改进:实现Translog与索引线程分离

- 分享个人Vim与Git配置文件管理经验

- 文本动画新体验:textillate插件功能介绍

- Python图像处理库Pillow 2.5.2版本发布

- DeepClassifier:简化文本分类任务的深度学习库

- Java领域恩舒技术深度解析

- 渲染jquery-mentions的markdown-it-jquery-mention插件

- CompbuildREDUX:探索Minecraft的现实主义纹理包

- Nest框架的入门教程与部署指南

- Slack黑暗主题脚本教程:简易安装指南

- JavaScript开发进阶:探索develop-it-master项目

- SafeStbImageSharp:提升安全性与代码重构的图像处理库

- Python图像处理库Pillow 2.5.0版本发布

- mytest仓库功能测试与HTML实践

- MATLAB与Python对比分析——cw-09-jareod源代码探究

- KeyGenerator工具:自动化部署节点密钥生成