没有合适的资源?快使用搜索试试~ 我知道了~

首页i.MX 6Dual/6Quad:高性能低功耗多媒体应用处理器

i.MX 6Dual/6Quad:高性能低功耗多媒体应用处理器

需积分: 10 0 下载量 69 浏览量

更新于2024-07-17

收藏 3.14MB PDF 举报

"i.MX 6Dual/6Quad 是NXPSemiconductors推出的一系列高性能、低功耗的多媒体应用处理器,专为消费电子产品设计。这些处理器属于Arm Cortex-A9架构的产品线,具有显著的技术革新,包括四核处理器,最高运行速度可达1.2GHz。它们集成了先进的2D和3D图形处理器,支持1080p视频处理,以及强大的集成电源管理功能。 i.MX 6Dual/6Quad处理器提供了64位DDR3/DDR3L/LPDDR2内存接口,便于高效数据传输,同时配备了多种外围接口,如Wi-Fi(WLAN)、蓝牙(Bluetooth)、全球定位系统(GPS)等,使得设备能够连接各种外部设备。这些接口设计旨在优化设备间的通信,提升用户体验。 每款型号(如MCIMX6QxExxxxC、MCIMX6QxExxxxD、MCIMX6QxExxxxE以及MCIMX6DxExxxxC、MCIMX6DxExxxxD和MCIMX6DxExxxxE)可能有不同的功能和特性,用户在选择时应参考具体的数据表,比如文档编号IMX6DQCEC Rev.6,11/2018,以获取详细的规格和性能指标。NXP公司保留了对生产细节进行更改的权利,以适应产品设计的改进,确保持续提供最优性能。 总体而言,i.MX 6Dual/6Quad处理器在多媒体应用领域具有很高的性价比,适用于需要高性能与节能并重的现代消费电子设备,如智能电视、平板电脑、游戏机或便携式媒体播放器等。其灵活的架构和丰富的接口使其成为构建高效、功能丰富的电子产品的重要组件。"

资源详情

资源推荐

i.MX 6Dual/6Quad Applications Processors for Consumer Products, Rev. 6, 11/2018

16 NXP Semiconductors

Modules List

ROM

96 KB

Boot ROM Internal

Memory

Supports secure and regular Boot Modes. Includes read protection on 4K

region for content protection

ROMCP ROM Controller with

Patch

Data Path ROM Controller with ROM Patch support

SATA Serial ATA Connectivity

Peripherals

The SATA controller and PHY is a complete mixed-signal IP solution

designed to implement SATA II, 3.0 Gbps HDD connectivity.

SDMA Smart Direct Memory

Access

System

Control

Peripherals

The SDMA is multi-channel flexible DMA engine. It helps in maximizing

system performance by off-loading the various cores in dynamic data

routing. It has the following features:

• Powered by a 16-bit Instruction-Set micro-RISC engine

• Multi-channel DMA supporting up to 32 time-division multiplexed DMA

channels

• 48 events with total flexibility to trigger any combination of channels

• Memory accesses including linear, FIFO, and 2D addressing

• Shared peripherals between Arm and SDMA

• Very fast context-switching with 2-level priority based preemptive

multi-tasking

• DMA units with auto-flush and prefetch capability

• Flexible address management for DMA transfers (increment,

decrement, and no address changes on source and destination

address)

• DMA ports can handle unit-directional and bi-directional flows (copy

mode)

• Up to 8-word buffer for configurable burst transfers

• Support of byte-swapping and CRC calculations

• Library of Scripts and API is available

SJC System JTAG

Controller

System

Control

Peripherals

The SJC provides JTAG interface, which complies with JTAG TAP

standards, to internal logic. The i.MX 6Dual/6Quad processors use JTAG

port for production, testing, and system debugging. In addition, the SJC

provides BSR (Boundary Scan Register) standard support, which

complies with IEEE1149.1 and IEEE1149.6 standards.

The JTAG port must be accessible during platform initial laboratory

bring-up, for manufacturing tests and troubleshooting, as well as for

software debugging by authorized entities. The i.MX 6Dual/6Quad SJC

incorporates three security modes for protecting against unauthorized

accesses. Modes are selected through eFUSE configuration.

SNVS Secure Non-Volatile

Storage

Security Secure Non-Volatile Storage, including Secure Real Time Clock, Security

State Machine, Master Key Control, and Violation/Tamper Detection and

reporting.

SPDIF Sony Philips Digital

Interconnect Format

Multimedia

Peripherals

A standard audio file transfer format, developed jointly by the Sony and

Phillips corporations. It supports Transmitter and Receiver functionality.

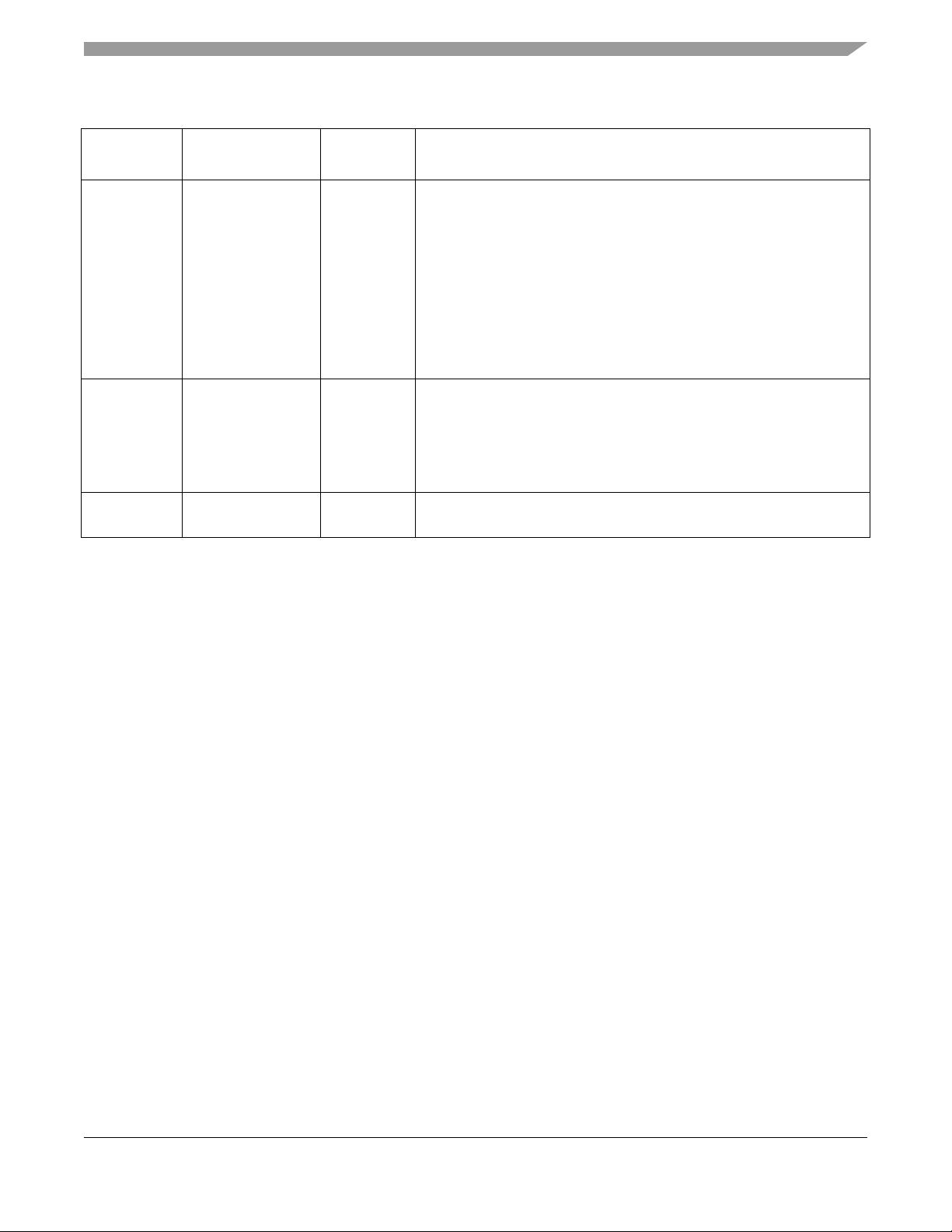

Table 2. i.MX 6Dual/6Quad Modules List (continued)

Block

Mnemonic

Block Name Subsystem Brief Description

Modules List

i.MX 6Dual/6Quad Applications Processors for Consumer Products, Rev. 6, 11/2018

NXP Semiconductors 17

SSI-1

SSI-2

SSI-3

I2S/SSI/AC97

Interface

Connectivity

Peripherals

The SSI is a full-duplex synchronous interface, which is used on the

processor to provide connectivity with off-chip audio peripherals. The SSI

supports a wide variety of protocols (SSI normal, SSI network, I2S, and

AC-97), bit depths (up to 24 bits per word), and clock / frame sync options.

The SSI has two pairs of 8x24 FIFOs and hardware support for an

external DMA controller to minimize its impact on system performance.

The second pair of FIFOs provides hardware interleaving of a second

audio stream that reduces CPU overhead in use cases where two time

slots are being used simultaneously.

TEMPMON Temperature Monitor System

Control

Peripherals

The temperature monitor/sensor IP module for detecting high temperature

conditions. The temperature read out does not reflect case or ambient

temperature. It reflects the temperature in proximity of the sensor location

on the die. Temperature distribution may not be uniformly distributed;

therefore, the read out value may not be the reflection of the temperature

value for the entire die.

TZASC Trust-Zone Address

Space Controller

Security The TZASC (TZC-380 by Arm) provides security address region control

functions required for intended application. It is used on the path to the

DRAM controller.

UART-1

UART-2

UART-3

UART-4

UART-5

UART Interface Connectivity

Peripherals

Each of the UARTv2 modules support the following serial data

transmit/receive protocols and configurations:

• 7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd

or none)

• Programmable baud rates up to 5 MHz

• 32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud

• IrDA 1.0 support (up to SIR speed of 115200 bps)

• Option to operate as 8-pins full UART, DCE, or DTE

USBOH3A USB 2.0 High Speed

OTG and 3x HS

Hosts

Connectivity

Peripherals

USBOH3 contains:

• One high-speed OTG module with integrated HS USB PHY

• One high-speed Host module with integrated HS USB PHY

• Two identical high-speed Host modules connected to HSIC USB ports.

Table 2. i.MX 6Dual/6Quad Modules List (continued)

Block

Mnemonic

Block Name Subsystem Brief Description

i.MX 6Dual/6Quad Applications Processors for Consumer Products, Rev. 6, 11/2018

18 NXP Semiconductors

Modules List

uSDHC-1

uSDHC-2

uSDHC-2

uSDHC-4

SD/MMC and SDXC

Enhanced

Multi-Media Card /

Secure Digital Host

Controller

Connectivity

Peripherals

i.MX 6Dual/6Quad specific SoC characteristics:

All four MMC/SD/SDIO controller IPs are identical and are based on the

uSDHC IP. They are:

• Conforms to the SD Host Controller Standard Specification version 3.0

• Fully compliant with MMC command/response sets and Physical Layer

as defined in the Multimedia Card System Specification,

v4.2/4.3/4.4/4.41 including high-capacity (size > 2 GB) cards HC MMC.

Hardware reset as specified for eMMC cards is supported at ports #3

and #4 only.

• Fully compliant with SD command/response sets and Physical Layer

as defined in the SD Memory Card Specifications, v3.0 including

high-capacity SDHC cards up to 32 GB and SDXC cards up to 2TB.

• Fully compliant with SDIO command/response sets and

interrupt/read-wait mode as defined in the SDIO Card Specification,

Part E1, v1.10

• Fully compliant with SD Card Specification, Part A2, SD Host

Controller Standard Specification, v2.00

All four ports support:

• 1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to

UHS-I SDR104 mode (104 MB/s max)

• 1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 52

MHz in both SDR and DDR modes (104 MB/s max)

However, the SoC-level integration and I/O muxing logic restrict the

functionality to the following:

• Instances #1 and #2 are primarily intended to serve as external slots or

interfaces to on-board SDIO devices. These ports are equipped with

“Card Detection” and “Write Protection” pads and do not support

hardware reset.

• Instances #3 and #4 are primarily intended to serve interfaces to

embedded MMC memory or interfaces to on-board SDIO devices.

These ports do not have “Card detection” and “Write Protection” pads

and do support hardware reset.

• All ports can work with 1.8 V and 3.3 V cards. There are two completely

independent I/O power domains for Ports #1 and #2 in four bit

configuration (SD interface). Port #3 is placed in his own independent

power domain and port #4 shares power domain with some other

interfaces.

VDOA VDOA Multimedia

Peripherals

The Video Data Order Adapter (VDOA) is used to re-order video data from

the “tiled” order used by the VPU to the conventional raster-scan order

needed by the IPU.

VPU Video Processing

Unit

Multimedia

Peripherals

A high-performing video processing unit (VPU), which covers many

SD-level and HD-level video decoders and SD-level encoders as a

multi-standard video codec engine as well as several important video

processing, such as rotation and mirroring.

See the i.MX 6Dual/6Quad reference manual (IMX6DQRM) for complete

list of VPU’s decoding/encoding capabilities.

WDOG-1 Watchdog Timer

Peripherals

The Watchdog Timer supports two comparison points during each

counting period. Each of the comparison points is configurable to evoke

an interrupt to the Arm core, and a second point evokes an external event

on the WDOG line.

Table 2. i.MX 6Dual/6Quad Modules List (continued)

Block

Mnemonic

Block Name Subsystem Brief Description

Modules List

i.MX 6Dual/6Quad Applications Processors for Consumer Products, Rev. 6, 11/2018

NXP Semiconductors 19

3.1 Special Signal Considerations

The package contact assignments can be found in Section 6, “Package Information and Contact

Assignments.” Signal descriptions are defined in the i.MX 6Dual/6Quad reference manual (IMX6DQRM).

Special signal consideration information is contained in the Hardware Development Guide for i.MX

6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

3.2 Recommended Connections for Unused Analog Interfaces

The recommended connections for unused analog interfaces can be found in the section, “Unused analog

interfaces,” of the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of

Applications Processors (IMX6DQ6SDLHDG).

WDOG-2

(TZ)

Watchdog

(TrustZone)

Timer

Peripherals

The TrustZone Watchdog (TZ WDOG) timer module protects against

TrustZone starvation by providing a method of escaping normal mode and

forcing a switch to the TZ mode. TZ starvation is a situation where the

normal OS prevents switching to the TZ mode. Such a situation is

undesirable as it can compromise the system’s security. Once the TZ

WDOG module is activated, it must be serviced by TZ software on a

periodic basis. If servicing does not take place, the timer times out. Upon

a time-out, the TZ WDOG asserts a TZ mapped interrupt that forces

switching to the TZ mode. If it is still not served, the TZ WDOG asserts a

security violation signal to the CSU. The TZ WDOG module cannot be

programmed or deactivated by a normal mode Software.

EIM NOR-Flash /PSRAM

interface

Connectivity

Peripherals

The EIM NOR-FLASH / PSRAM provides:

• Support 16-bit (in muxed IO mode only) PSRAM memories (sync and

async operating modes), at slow frequency

• Support 16-bit (in muxed IO mode only) NOR-Flash memories, at slow

frequency

• Multiple chip selects

XTALOSC Crystal Oscillator

interface

— The XTALOSC module enables connectivity to external crystal oscillator

device. In a typical application use-case, it is used for 24 MHz oscillator.

Table 2. i.MX 6Dual/6Quad Modules List (continued)

Block

Mnemonic

Block Name Subsystem Brief Description

i.MX 6Dual/6Quad Applications Processors for Consumer Products, Rev. 6, 11/2018

20 NXP Semiconductors

Electrical Characteristics

4 Electrical Characteristics

This section provides the device and module-level electrical characteristics for the i.MX 6Dual/6Quad

processors.

4.1 Chip-Level Conditions

This section provides the device-level electrical characteristics for the SoC. See Table 3 for a quick

reference to the individual tables and sections.

4.1.1 Absolute Maximum Ratings

CAUTION

Stresses beyond those listed under Table 4 may affect reliability or cause

permanent damage to the device. These are stress ratings only. Functional

operation of the device at these or any other conditions beyond those

indicated in the Operating Ranges or Parameters tables is not implied.

Table 3. i.MX 6Dual/6Quad Chip-Level Conditions

For these characteristics, … Topic appears …

Absolute Maximum Ratings on page 21

FCPBGA Package Thermal Resistance on page 22

Operating Ranges on page 23

External Clock Sources on page 25

Maximum Measured Supply Currents on page 27

Low Power Mode Supply Currents on page 28

USB PHY Current Consumption on page 30

SATA Typical Power Consumption on page 30

PCIe 2.0 Maximum Power Consumption on page 31

HDMI Maximum Power Consumption on page 32

剩余170页未读,继续阅读

szzjz

- 粉丝: 3

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- zlib-1.2.12压缩包解析与技术要点

- 微信小程序滑动选项卡源码模版发布

- Unity虚拟人物唇同步插件Oculus Lipsync介绍

- Nginx 1.18.0版本WinSW自动安装与管理指南

- Java Swing和JDBC实现的ATM系统源码解析

- 掌握Spark Streaming与Maven集成的分布式大数据处理

- 深入学习推荐系统:教程、案例与项目实践

- Web开发者必备的取色工具软件介绍

- C语言实现李春葆数据结构实验程序

- 超市管理系统开发:asp+SQL Server 2005实战

- Redis伪集群搭建教程与实践

- 掌握网络活动细节:Wireshark v3.6.3网络嗅探工具详解

- 全面掌握美赛:建模、分析与编程实现教程

- Java图书馆系统完整项目源码及SQL文件解析

- PCtoLCD2002软件:高效图片和字符取模转换

- Java开发的体育赛事在线购票系统源码分析

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功