5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DDR_BS00

BDDR_A1

DDR_D5

DDR_A2

DDR_BS00

DDR_D24

DDR_WE

DDR_A2

BDDR_CAS

B_DQS0N

DDR_A1

BDDR_A10

DDR_D6

B_DQS2N

DDR_A3

DDR_D[0:31]

DDR_D25

DDR_A1

VREF_STL

B_DQS1P

DDR_A0

BDDR_BS02

DDR_D7

DDR_A4

BDDR_A2

DDR_D26

BDDR_A9

DDR_A0

DDR_RAS

DDR_A[0:13]

B_DQS1N

BDDR_A11

DDR_D8

BDDR_RAS

DDR_D27

BDDR_A8

BDDR_A0

DQM1

B_DQS1P

DDR_D9

BDDR_A3

DDR_D28

B_DQS2P

BDDR_A7

DDR_CAS

DDR_D10

BDDR_A12

DDR_CK_P

DDR_D29

DQM2

B_DQS3P

BDDR_A6

DDR_D11

DDR_D30

BDDR_A4

DQM3

B_DQS2P

BDDR_D2

BDDR_D0

DDR_D12

BDDR_A5

DDR_A3

DDR_D31

DQS0P

DDR_BS[0:2]

B_DQS3N

DDR_CK_N

B_DQM0

DDR_D13

DDR_D0

BDDR_A13

DDR_CS

BDDR_D16

DDR_D14

DQS0N

B_DQS1N

B_DQS0N

BDDR_CKE

BDDR_D18

B_DQM3

VREF_STL

BDDR_WE

BDDR_D17

BDDR_D19

BDDR_D31

BDDR_D30

BDDR_D29

BDDR_D27

BDDR_D28

BDDR_D26

DDR_CLK_N

BDDR_D25

BDDR_D24

BDDR_D20

BDDR_D23

BDDR_D22

BDDR_D22

BDDR_D21

BDDR_D20

DDR_D15

BDDR_D19

BDDR_D18

BDDR_D17

BDDR_D16

BDDR_D29

BDDR_D30

BDDR_D28

BDDR_D27

BDDR_D25

DQS1P

BDDR_D23

BDDR_D21

BDDR_D31

BDDR_D24

DDR_A5

DDR_A10

DDR_A8

DDR_A7

DDR_A9

DDR_A6

DDR_A11

DDR_A12

BDDR_D26

DDR_A12

DDR_A11

DDR_A6

DDR_A5

DDR_A9

DDR_A7

DDR_A8

DDR_A10

DDR_CS

DDR_D16

B_DQM1

DDR_D5

DDR_D4

DDR_D7

BDDR_D7

DDR_D29

BDDR_D1

BDDR_D4

DDR_D30

BDDR_D9

DQS1N

BDDR_D2

DDR_D3

BDDR_D15

BDDR_D5

DDR_D26

DDR_D20

DDR_D6

DDR_D8

DDR_D25

DDR_D17

DDR_D1

BDDR_D3

DDR_D27

DDR_D21

BDDR_D13

BDDR_D7

B_DQM2

BDDR_D5

BDDR_D10

DDR_D13

DDR_D15

DDR_D22

BDDR_D3

BDDR_D6

DDR_D24

BDDR_D1

DDR_D10

BDDR_D15

DDR_D14

DDR_D12

BDDR_D14

DDR_D23

BDDR_D8 BDDR_D13

BDDR_D4

DDR_D19

DDR_D11

BDDR_D12

BDDR_D0

BDDR_D10

BDDR_D11

BDDR_D8

BDDR_D9

DDR_D31

DDR_D9

BDDR_D11 DDR_D28

BDDR_D14

BDDR_D12

DDR_CAS

BDDR_CLK_P

BDDR_D6

DDR_D0

DDR_D2

DDR_D18

DDR_D16

DDR_A12

BDDR_D[16:31]

DDR_D17

DDR_CS

DDR_CLK_P

BDDR_D[0:15]

DQS2N

B_DQS0PDDR_RAS

DDR_A11

DDR_D18

B_DQM0

DDR_CAS

DDR_WE

DDR_A10

DQS3P

DDR_D19

DDR_CKEDDR_CKE

DDR_RAS

B_DQM1

DQS3N

DDR_D20

DDR_D1

DQM0

B_DQM2

DDR_D2

DDR_WE

B_DQS2N

DDR_D21

DDR_CLK_P

BDDR_BS00

DDR_A9

BDDR_CS

B_DQM3

DDR_D3

DDR_D22

DDR_A4

DDR_BS02

DDR_CLK_N

DDR_CKE

B_DQS3P

DDR_A0

BDDR_CLK_N

DDR_D4

DDR_BS02

DDR_BS01 DDR_BS01

B_DQS0P

DDR_D23

DQS2P

DDR_A1

DDR_A3BDDR_BS01

DDR_A7

B_DQS3N

DDR_A13 DDR_A13

BDDR_A7

BDDR_A3

BDDR_BS02 DDR_BS02

BDDR_BS00 DDR_BS00

BDDR_A10

BDDR_WE

DDR_A5

DDR_WE

BDDR_BS01

DDR_A6

DDR_BS01

BDDR_A1

BDDR_A5

BDDR_A9

BDDR_A11

BDDR_A6

BDDR_A2 DDR_A2

BDDR_CAS

BDDR_RAS

BDDR_CS

BDDR_A0

DDR_CS

DDR_RAS

DDR_CAS

BDDR_A4

BDDR_A8

BDDR_A13

DDR_A4

DDR_A8

DDR_A13

BDDR_A12

VCC_1V8

VCC_1V8

VCC_1V8

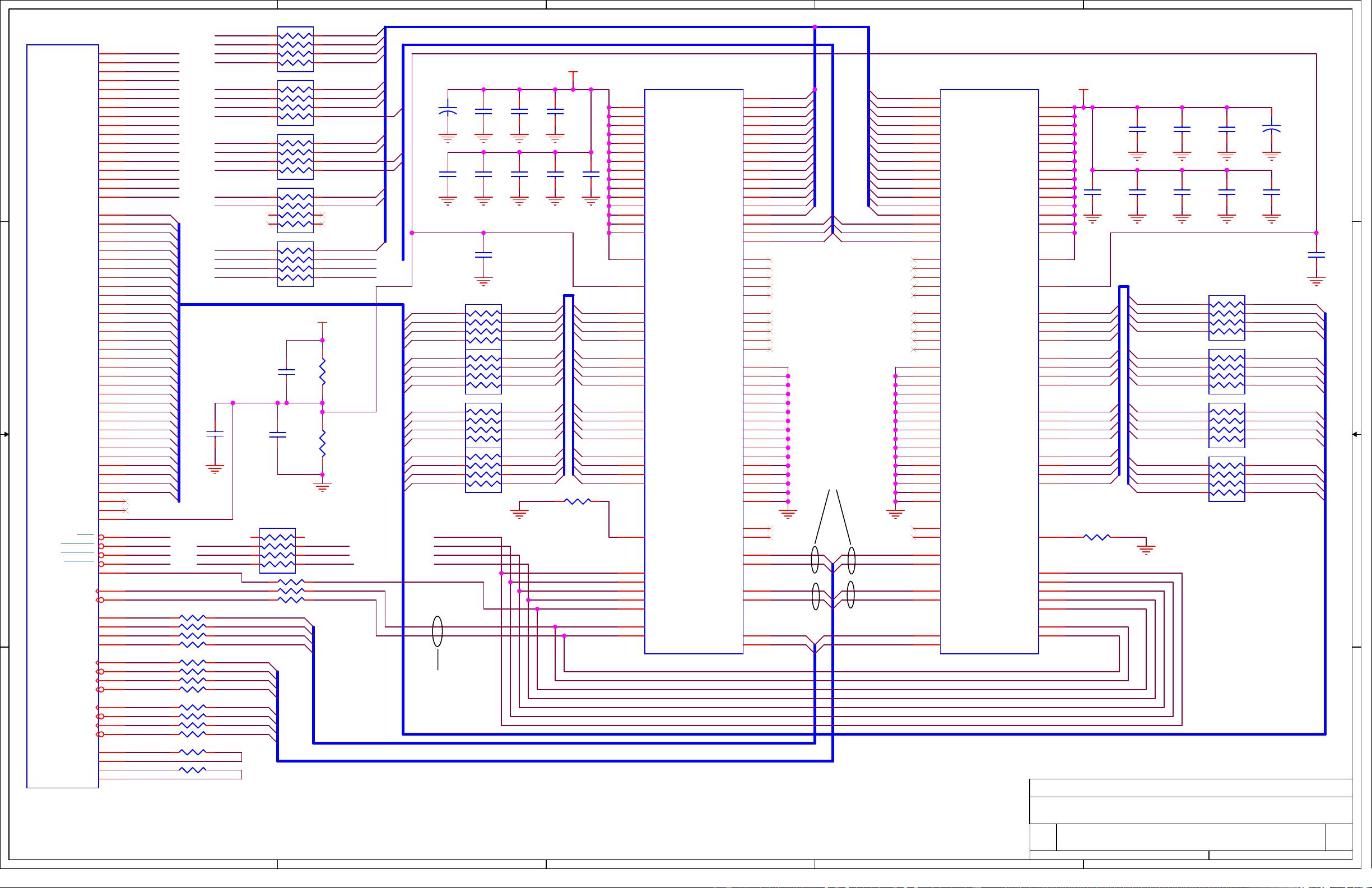

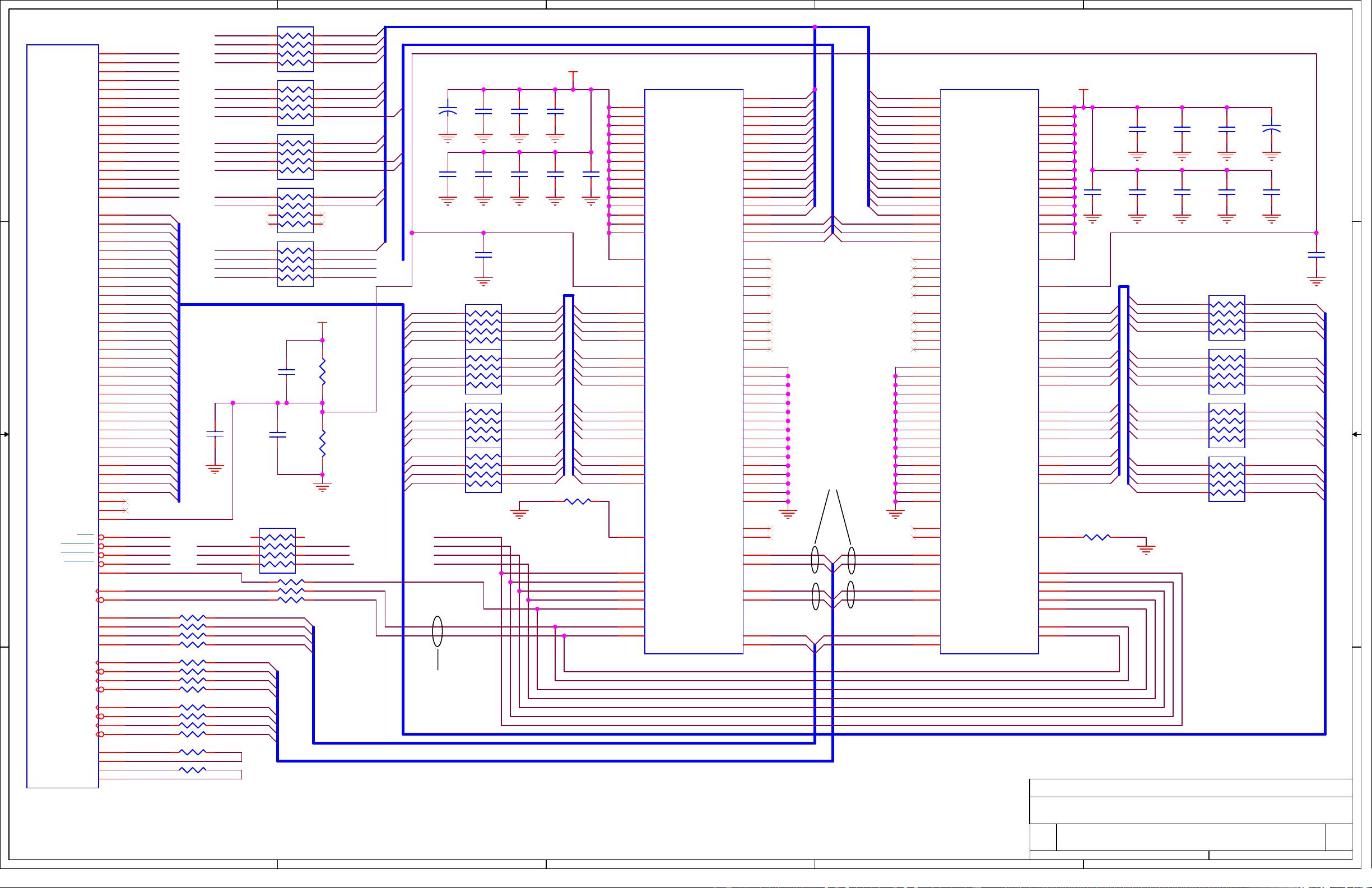

Title

Size Document Number Rev

Date: Sheet

of

<Doc> 1.2

DM648 EVM DDR2 Controller and Memory

B

524Thursday, July 05, 2007

Title

Size Document Number Rev

Date: Sheet of

<Doc> 1.2

DM648 EVM DDR2 Controller and Memory

B

524Thursday, July 05, 2007

Title

Size Document Number Rev

Date: Sheet of

<Doc> 1.2

DM648 EVM DDR2 Controller and Memory

B

524Thursday, July 05, 2007

128 MEGABYTES

128 MEGABYTES

4 DIFFERENTIAL

NETS

DIFFERENTIAL

NET

NOTE 5.1: PLACEMENT AND ROUTING OF THE DDR2 INTERFACE

SHALL BE DONE IN ACCORDANCE TO THE DM648

DDR2 COLLATERAL.

NOTE 5.2: SWIZZLING WITHIN DATA BYTES PERMITTED.

NOTE 5.3: BYPASS CAPS (0.1uF) ASSOCATED WITH U14 AND U15.

+

C734

22uF

+

C734

22uF

DDR

U23H

TMS320DM648

DDR

U23H

TMS320DM648

BED00

E9

BED01

C9

BED02

B9

BED03

C8

BED04

E8

BED05

D8

BED06

C7

BED07

E7

BED08

C6

BED09

B7

BED10

D6

BED11

A3

BED12

B3

BED13

A4

BED14

B4

BED15

C5

BED16

B16

BED17

C16

BED18

D16

BED19

E16

BED20

B17

BED21

C17

BED22

D17

BED23

E17

BED24

C18

BED25

D18

BED26

B19

BED27

C19

BED28

B20

BED29

D19

BED30

C20

BED31

E19

BBA0

C12

BBA1

B12

BBA2

E11

BEA00

D15

BEA01

C15

BEA02

F13

BEA03

E14

BEA04

D14

BEA05

C14

BEA06

F11

BEA07

B14

BEA08

F12

BEA09

D13

BEA11

B13

BEA10

A13

BEA12

E12

BEA13

F10

BCE

F9

BSDRAS

E10

BSDWE

D11

BSDCAS

D10

BSDCKE

B11

BECLKOUTP

A11

BECLKOUTN

A12

BSDDQS0P

A9

BSDDQS1P

A7

BSDDQS0N

A8

BSDDQS1N

A6

BSDDQS2P

A17

BSDDQS2N

A16

BSDDQS3P

A20

BSDDQS3N

A19

BSDDQM0

B8

BSDDQM1

D5

BSDDQM2

E15

BSDDQM3

B21

BSDDGATE0

D7

BSDDGATE1

B6

BSDDGATE2

E18

BSDDGATE3

A21

BEODT0

E13

BEODT1

A14

VREFSSTL

C11

C742

0.1uF

C742

0.1uF

R57522R57522

R570 22R570 22

R99 22R99 22

R572 22R572 22

C735

0.1uF

C735

0.1uF

C731

0.1uF

C731

0.1uF

RN517RPACK4-22 RN517RPACK4-22

2

3

4

18

5

6

7

R571 22R571 22

RN511 RPACK4-22RN511 RPACK4-22

1

2

3

4 5

6

7

8

R573 22R573 22

RN519 RPACK4-22RN519 RPACK4-22

4

2

1

3 6

8

7

5

C744

0.1uF

C744

0.1uF

R577 22R577 22

RN516 RPACK4-22RN516 RPACK4-22

3

2

4

1 8

5

7

6

C733

0.1uF

C733

0.1uF

R569 22R569 22

U32

92-ball DDR Package

U32

92-ball DDR Package

A12

V2

A11

U7

A10

R2

A9

U3

A8

U8

A7

U2

A6

T7

A5

T3

A4

T8

A3

T2

A2

R7

A1

R3

A0

R8

BA2

P1

BA1

P3

BA0

P2

NC.1

AA9

NC.2

AA8

NC.3

AA2

NC.4

AA1

NC.5

D2

NC.7

A9

NC.8

A8

NC.9

A2

NC.10

A1

NC.11

H2

RFU.1

V3

RFU.2

V7

ODT

N9

CS#

P8

CAS#

P7

RAS#

N7

WE#

N3

CKE

N2

CK

M8

CK#

N8

UDQS#/NU

D8

UDQS

E7

LDQS#/NU

H8

LDQS

J7

UDM

E3

LDM

J3

VDD.1

M9

VDD.2

H1

VDD.3

R9

VDD.4

D1

VDD.5

V1

VDDQ.1

F3

VDDQ.2

F7

VDDQ.3

K1

VDDQ.4

K3

VDDQ.5

K7

VDDQ.6

K9

VDDQ.7

D9

VDDQ.8

F1

VDDQ.9

F9

VDDQ.10

H9

VDDL

M1

VREF

M2

DQ15

E9

DQ14

E1

DQ13

G9

DQ12

G1

DQ11

G3

DQ10

G7

DQ9

F2

DQ8

F8

DQ7

J9

DQ6

J1

DQ5

L9

DQ4

L1

DQ3

L3

DQ2

L7

DQ1

K2

DQ0

K8

VSS.1

U9

VSS.2

T1

VSS.3

H3

VSS.4

D3

VSS.5

M3

VSSQ.1

G8

VSSQ.2

J8

VSSQ.3

D7

VSSQ.4

J2

VSSQ.5

E2

VSSQ.6

L8

VSSQ.7

L2

VSSQ.8

E8

VSSQ.9

H7

VSSQ.10

G2

VSSDL

M7

A13

V8

C736

0.1uF

C736

0.1uF

R567 22R567 22

R56822 R56822

C738

0.1uF

C738

0.1uF

R98 10R98 10

+

C746

22uF

+

C746

22uF

RN518RPACK4-22 RN518RPACK4-22

1

3

2

45

7

6

8

R576 22R576 22

C748

0.1uF

C748

0.1uF

RN513RPACK4-22 RN513RPACK4-22

1

3

4

27

5

6

8

C222

0.1uF

C222

0.1uF

C737

0.1uF

C737

0.1uF

RN507 RPACK4-22RN507 RPACK4-22

1

2

3

4 5

6

7

8

R92 22R92 22

C221

0.1uF

C221

0.1uF

C739

0.1uF

C739

0.1uF

RN509 RPACK4-22RN509 RPACK4-22

1

2

3

4 5

6

7

8

R97 10R97 10

C747

0.1uF

C747

0.1uF

C740

0.1uF

C740

0.1uF

R114 22R114 22

C749

0.1uF

C749

0.1uF

R221

1K 1%

R221

1K 1%

C741

0.1uF

C741

0.1uF

C168

0.1uF

C168

0.1uF

RN514RPACK4-22 RN514RPACK4-22

3

2

4

18

5

7

6

R566 22R566 22

RN508 RPACK4-22RN508 RPACK4-22

1

2

3

4 5

6

7

8

R574 22R574 22

C743

0.1uF

C743

0.1uF

C745

0.1uF

C745

0.1uF

C732

0.1uF

C732

0.1uF

R564 22R564 22

R222

1K 1%

R222

1K 1%

RN520 RPACK4-22RN520 RPACK4-22

2

1

3

4 5

6

8

7

U31

92-ball DDR Package

U31

92-ball DDR Package

A12

V2

A11

U7

A10

R2

A9

U3

A8

U8

A7

U2

A6

T7

A5

T3

A4

T8

A3

T2

A2

R7

A1

R3

A0

R8

BA2

P1

BA1

P3

BA0

P2

NC.1

AA9

NC.2

AA8

NC.3

AA2

NC.4

AA1

NC.5

D2

NC.7

A9

NC.8

A8

NC.9

A2

NC.10

A1

NC.11

H2

RFU.1

V3

RFU.2

V7

ODT

N9

CS#

P8

CAS#

P7

RAS#

N7

WE#

N3

CKE

N2

CK

M8

CK#

N8

UDQS#/NU

D8

UDQS

E7

LDQS#/NU

H8

LDQS

J7

UDM

E3

LDM

J3

VDD.1

M9

VDD.2

H1

VDD.3

R9

VDD.4

D1

VDD.5

V1

VDDQ.1

F3

VDDQ.2

F7

VDDQ.3

K1

VDDQ.4

K3

VDDQ.5

K7

VDDQ.6

K9

VDDQ.7

D9

VDDQ.8

F1

VDDQ.9

F9

VDDQ.10

H9

VDDL

M1

VREF

M2

DQ15

E9

DQ14

E1

DQ13

G9

DQ12

G1

DQ11

G3

DQ10

G7

DQ9

F2

DQ8

F8

DQ7

J9

DQ6

J1

DQ5

L9

DQ4

L1

DQ3

L3

DQ2

L7

DQ1

K2

DQ0

K8

VSS.1

U9

VSS.2

T1

VSS.3

H3

VSS.4

D3

VSS.5

M3

VSSQ.1

G8

VSSQ.2

J8

VSSQ.3

D7

VSSQ.4

J2

VSSQ.5

E2

VSSQ.6

L8

VSSQ.7

L2

VSSQ.8

E8

VSSQ.9

H7

VSSQ.10

G2

VSSDL

M7

A13

V8

C750

0.1uF

C750

0.1uF

R565 22R565 22

RN512 RPACK4-22RN512 RPACK4-22

1

2

3

4 5

6

7

8

RN515 RPACK4-22RN515 RPACK4-22

3

4

1

2 7

8

5

6

RN510 RPACK4-22RN510 RPACK4-22

1

2

3

4 5

6

7

8