Cadence设计系统详解:从微电子所讲义

需积分: 10 133 浏览量

更新于2024-08-02

收藏 4MB PPT 举报

"Cadence讲义(清华微电子所).ppt"

Cadence是全球领先的电子设计自动化(EDA)软件供应商,其工具广泛应用于集成电路设计、验证和实现等环节。这本讲义来自于清华大学微电子研究所,旨在详细介绍Cadence设计系统及其在微电子学中的应用。

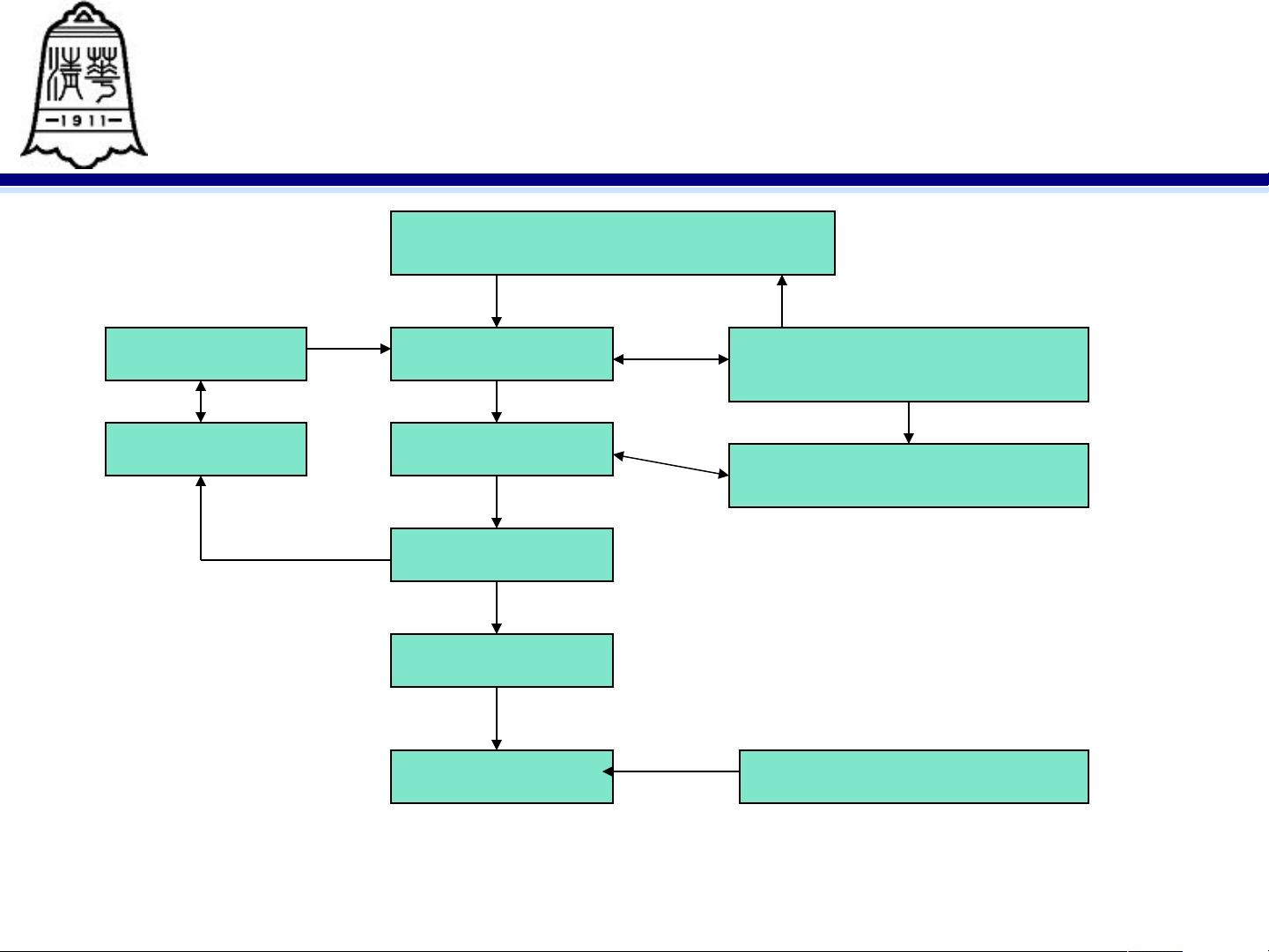

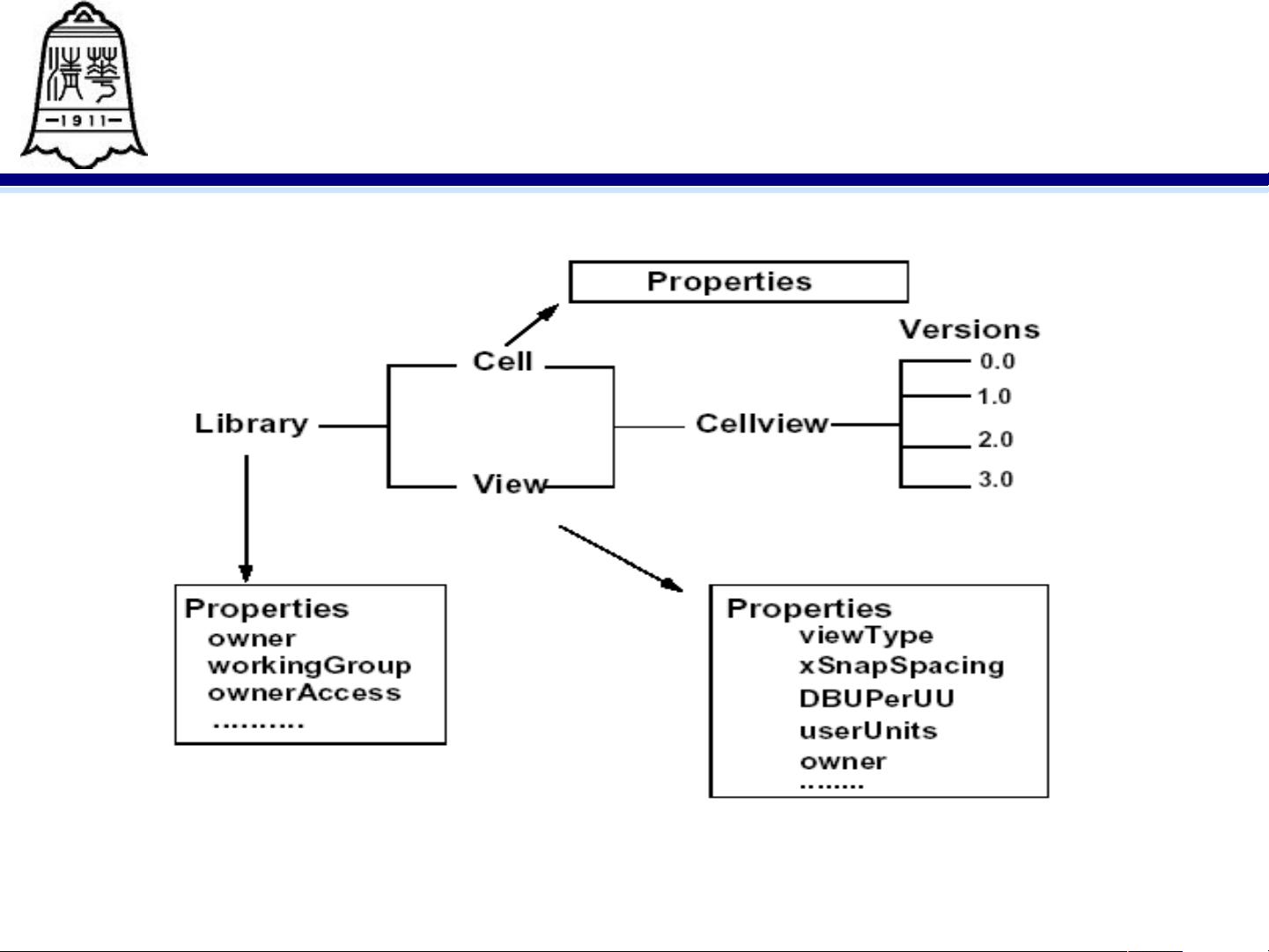

Cadence系统概述中,首先提到了设计流程,它涵盖了从概念设计到最终产品的全过程,包括了逻辑设计、模拟、布局布线、验证等多个步骤。系统组织结构指的是Cadence软件套装的组成部分,通常包括前端设计工具(如VHDL或Verilog仿真器,行为综合工具)和后端设计工具(如版图设计工具Virtuoso LE,以及版图验证工具如Diva和Dracula)。

Cadence的Virtuoso LE是一款强大的版图编辑器,用于IC物理设计,支持精细的图形操作和复杂的版图规则检查。Diva和Dracula则是用于版图验证的重要工具,确保设计符合工艺规则和电气规则,以防止潜在的制造问题。

讲义中提到了学习Cadence工具的重要性,这是因为集成电路的设计复杂度随着技术发展而不断提升。例如,特征尺寸从1997年的250nm逐渐减小到2012年的50nm,电源电压也在不断降低,而芯片面积、晶体管数量和工作频率却在增加,这导致设计难度成倍增长。为了应对这种挑战,掌握Cadence等先进的EDA工具成为了必要。

此外,Cadence工具支持多种设计方法学,如VHDL仿真,用于验证电路行为;行为综合将高级语言描述转化为门级网表;逻辑综合优化逻辑结构以提高性能;可测性设计确保芯片在测试阶段的易用性;低功耗设计则考虑了能耗优化,这对于便携式设备尤其关键。

布局是设计过程中的重要环节,涉及到如何在芯片有限的空间内高效地布置晶体管和其他元器件,同时要考虑信号完整性和功耗分布。Cadence的工具提供了高级的布局策略和自动化功能,帮助设计师实现最优的物理布局。

这本Cadence讲义是针对微电子学专业学生或从业者的一份宝贵教材,涵盖了从基础理论到实际操作的全面知识,旨在帮助读者理解和掌握利用Cadence工具进行集成电路设计的关键技能。

2021-10-06 上传

2021-10-06 上传

528 浏览量

2021-10-06 上传

2021-10-06 上传

2009-04-21 上传

hacker2009

- 粉丝: 2

- 资源: 52